運算放大器構成加法器 可以分為同相加法器和反相加法器

2022-08-05 17:17:38 22396

22396

求助誰幫我設計一個32位浮點加法器,求助啊,謝謝啊 新搜剛學verilog,不會做{:4_106:}

2013-10-20 20:07:16

`流水線設計前言:本文從四部分對流水線設計進行分析,具體如下:第一部分什么是流水線第二部分什么時候用流水線設計第三部分使用流水線的優缺點第四部分流水線加法器舉例第一 什么是流水線流水線設計就是將組合

2020-10-26 14:38:12

加法器的芯片如何選擇?常用的有哪些?

2017-08-09 14:39:13

請問下大家,,進位選擇加法器和進位跳躍加法器的區別是啥啊?我用Verilog實現16位他們的加法器有什么樣的不同啊?還請知道的大神告訴我一下。。

2016-10-20 20:23:54

IP核加法器

2019-08-14 14:24:38

圖一圖二圖三圖四最近寫了一個16位二級流水線加法器,并進行了一下仿真。發現在always塊中采用阻塞賦值(=)和非阻塞賦值(

2016-09-09 09:18:13

了觸發器,數據的采集需要發生在時鐘上升沿),總處理數據的吞吐量增加了。流水線改造實例接下來我們用一個很簡單的例子來說明如何對電路進行簡單的流水線改造,假設我們現在要實現(4*a+6*b)-10,那么我們

2019-12-05 11:53:37

現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操作(在浮點運算中的浮點加法運算幾乎占到全部運算操作的一半以上),所以,浮點加法器是現代信號

2019-07-05 06:21:42

什么是加法器?加法器的原理是什么 反相加法器等效原理圖解析

2021-03-11 06:30:35

嗨,對于下面的代碼片段,合成后會得到哪種類型的加法器?例如:半加法器,全加器,CLA,Ripple加法器?模塊ee(輸入a,e,輸出reg c);總是@(*)c = a + e;endmodule

2020-03-19 09:49:31

只是想知道,如果我做一個大加法器,我可以說128位加法器。從LUT的角度來看,加法器的外觀如何,因為我看到Spartan 6器件的片M具有與其他塊連接的進位邏輯。如果可能,有人可以為加法器提供LUT透視框圖,只需2 LUT之間的連接就可以理解這個想法。謝謝,

2019-08-08 07:13:38

如何理解fpga流水線

2015-08-15 11:43:23

前段時間發了個關于fpga的PID實現的帖子,有個人說“整個算法過程說直白點就是公式的硬件實現,用到了altera提供的IP核,整個的設計要注意的時鐘的選取,流水線的應用”,本人水平有限,想請教一下其中時鐘的選取和流水線的設計應該怎么去做,需要注意些什么,請大家指導一下。

2015-01-11 10:56:59

在數字化飛速發展的今天,人們對微處理器的性能要求也越來越高。作為衡量微處理器性能的主要標準,主頻和乘法器運行一次乘法的周期息息相關。因此,為了進一步提高微處理器性能,開發高速高精度的乘法器勢在必行

2019-09-03 08:31:04

如何進行數字相關器基本模型分析、流水線型數字相關器模型及信號處理流程 ?

2021-04-06 06:47:28

現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操作(在浮點運算中的浮點加法運算幾乎占到全部運算操作的一半以上),所以,浮點加法器是現代信號

2019-08-15 08:00:45

我為64位加法器編寫了一個Verilog代碼,并在FPGA上進行了綜合我想在Virtex FPGA板上為64位加法器進行功耗分析。任何人都可以指出可以幫助我順利進行功率分析的材料。如果可能的話,我甚至想獲得視頻教程的鏈接。任何形式的幫助都可以謝謝

2020-07-18 13:41:42

需要設計一個模加法器,書上沒有詳細的講解,只說是用端回進位加法器實現模2^n-1,可是具體應該怎么設計啊~~~~

2016-07-07 14:48:36

fpga:Spartan-6 xc6slx150-3fgg484我在資源密集型處理系統中使用了幾百個8位加法器,因此資源使用很重要。用于加法器減法器的核心生成器為具有2個8位輸入和8位輸出,0延遲

2019-04-03 15:55:35

基于FPGA的64位流水線加法器的設計基本要求: FPGA 可自行選擇可實現64位無符號數的加法運算8級流水線深度

2014-12-18 11:00:42

流水線技術是提高系統吞吐率的一項強大的實現技術,并且不需要大量重復設置硬件。20世界60年代早期的一些高端機器中第一次采用了流水線技術。第一個采用指令流水線的機器是IBM7030(又稱

2023-03-01 17:52:21

在ARM中,關于 LDR流水線,分支流水線,中斷流水線,其和 PC 之間的關系一直沒整明白,求大神詳解!!!

2019-04-30 07:45:25

請問一下高速流水線浮點加法器的FPGA怎么實現?

2021-05-07 06:44:26

我正在設計一個流水線遞歸加法器樹。該設計適用于2個輸入數的功率,但在達到奇數個輸入時似乎失敗。結構沒問題,但是比特數關閉,這導致運行模擬時的不確定狀態。請看一下。加布里埃爾adder_r1.sv 4

2019-04-25 13:53:44

FPGA重要設計思想及工程應用之流水線設

流水線設計是高速電路設計中的一 個常用設計手段。如果某個設計的處理流程分為若干步驟,而且整個數據處理 流程分

2010-02-09 11:02:20 52

52 摘要:加法運算在計算機中是最基本的,也是最重要的運算。傳統的快速加法器是使用超前進位加法器,但其存在著電路不規整,需要長線驅動等缺點。文章提出了采用二叉樹法設

2010-05-19 09:57:06 62

62 流水線技術在高速數字電路設計中的應用

2010-07-17 16:37:21 6

6 根據一款32位嵌入式CPU的400MHz主頻的要求,結合該CPU五級流水線結構,并借鑒各種算法成熟的加法器,提出了一種電路設計簡單、速度快、功耗低、版圖面積小的32位改進定點加法器

2010-07-19 16:10:03 17

17 介紹了補碼陣列乘法器的Pezaris 算法。為提高運算速度,利用流水線技術進行改進,設計出流水線結構陣列乘法器,使用VHDL語言建模,在Quartus II集成開發環境下進行仿真和功能驗證

2010-08-02 16:38:00 0

0

圖二所示為4位并行的BCD加法器電路。其中上面加法器的輸入來自低一級的BCD數字。下

2009-03-28 16:35:54 11908

11908

第二十講 加法器和數值比較器

6.6.1 加法器一、半加器1.含義 輸入信號:加數Ai,被加數Bi 輸出信號:本位和Si,向高位

2009-03-30 16:24:54 5502

5502

加法器:Summing Amplifier

The summing amplifier, a special case of the inverting amplifier, is shown in Figure 4. The circuit gives an

2009-05-16 12:38:34 2626

2626

什么是流水線技術

流水線技術

2010-02-04 10:21:39 3702

3702 加法器,加法器是什么意思

加法器 : 加法器是為了實現加法的。 即是產生數的和的裝置。加數和被加數為輸入,和數與

2010-03-08 16:48:58 5106

5106 加法器原理(16位先行進位)

這個加法器寫的是一波三折啊,昨天晚上花了兩三個小時好不容易寫完編譯通過了,之后modelsim莫

2010-03-08 16:52:27 10942

10942 十進制加法器,十進制加法器工作原理是什么?

十進制加法器可由BCD碼(二-十進制碼)來設計,它可以在二進制加法器的基礎上加上適當的“校正”邏輯來實現,該校正邏

2010-04-13 10:58:41 12741

12741 流水線中的相關培訓教程[4]

下面討論如何利用編譯器技術來減少這種必須的暫停,然后論述如何在流水線中實現數據相關檢測和定向。

2010-04-13 16:09:15 4272

4272 為了提高快速傅里葉變換( FFT)處理數據的實時性,本文利用現場可編程陣列( FPGA)邏輯資源豐富、運算速度快的特點以及FFT算法的分級特性,實現了高速、高階FFT的流水線工作方式設計。通

2011-10-01 01:52:51 55

55 為了提高快速傅里葉變換( FFT)處理數據的實時性,本文利用現場可編程陣列( FPGA)邏輯資源豐富、運算速度快的特點以及FFT算法的分級特性,實現了高速、高階FFT的流水線工作方式設計。通

2011-10-28 17:11:26 32

32 設計了一種支持IEEE754浮點標準的32位高速流水線結構浮點乘法器。該乘法器采用新型的基4布思算法,改進的4:2壓縮結構和部分積求和電路,完成Carry Save形式的部分積壓縮,再由Carry Lo

2012-02-29 11:20:45 3269

3269 浮點運算器的核心運算部件是浮點加法器,它是實現浮點指令各種運算的基礎,其設計優化對于提高浮點運算的速度和精度相當關鍵。文章從浮點加法器算法和電路實現的角度給出設計

2012-07-06 15:05:42 47

47 8位加法器和減法器設計實習報告

2013-09-04 14:53:33 133

133 為了縮短加法電路運行時間,提高FPGA運行效率,利用選擇進位算法和差額分組算法用硬件電路實現32位加法器,差額分組中的加法單元是利用一種改進的超前進位算法實現,選擇進位算

2013-09-18 14:32:05 33

33 Xilinx FPGA工程例子源碼:Xilinx 公司的加法器核

2016-06-07 15:07:45 12

12 同相加法器輸入阻抗高,輸出阻抗低 反相加法器輸入阻抗低,輸出阻抗高.加法器是一種數位電路,其可進行數字的加法計算。當選用同相加法器時,如A輸入信號時,因為是同相加法器,輸入阻抗高,這樣信號不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 55184

55184

加法器VHDL程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 15:51:00 5

5 基于Skewtolerant Domino的新型高速加法器

2017-01-22 20:29:21 8

8 流水線狀態機20進制,101序列檢測,8位加法器流水線的程序

2017-05-24 14:40:47 0

0 加法器是為了實現加法的。即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。

2017-06-06 08:45:01 22730

22730

最近在做基于MIPS指令集的單周期CPU設計,其中的ALU模塊需要用到加法器,但我們知道普通的加法器是串行執行的,也就是高位的運算要依賴低位的進位,所以當輸入數據的位數較多時,會造成很大的延遲

2018-07-09 10:42:00 19434

19434

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。

2017-08-16 09:39:34 21933

21933

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網絡所構成的運算電路來實現。

2017-08-16 11:09:48 159697

159697

8位全加器可由2個4位的全加器串聯組成,因此,先由一個半加器構成一個全加器,再由4個1位全加器構成一個4位全加器并封裝成元器件。加法器間的進位可以串行方式實現,即將低位加法器的進位輸出cout與相臨的高位加法器的最低進位輸入信號cin相接最高位的輸出即為兩數之和。

2017-11-24 10:01:45 28522

28522

摘要: 數字相關器在數字擴頻通信系統中應用廣泛,受數字信號處理器件速度限制,無法應用于高速寬帶通信系統,在此提出了一種基于流水線加法器的數字相關處理算法。該算法最大限度地減少了加法器進位操作

2018-01-18 03:49:01 324

324 只產生9個部分積,有效降低了部分積壓縮陣列的規模與延時.通過對5級流水線關鍵路徑中壓縮陣列和64位超前進位(CLA)加法器的優化設計,減少了乘法器的延時和面積.經現場可編程邏輯器件仿真驗證表明,與采用Radix-8 Booth算法的乘法器相比,該乘法器速度提高了11%,硬件資

2018-03-15 13:34:00 6

6 一、什么是加法器加法器是為了實現加法的。即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半

2018-03-16 15:57:19 20714

20714

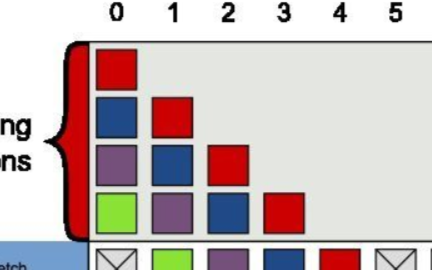

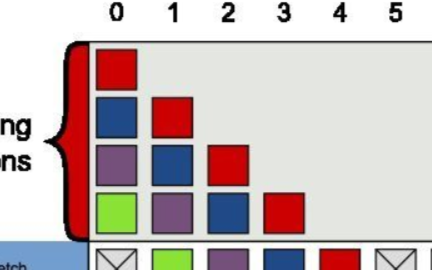

顏色表示了不同階段的可配置性或可編程性:綠色表示該流水線階段是完全可編程控制的,黃色表示該流水線階段可以配置但不是可編程的,藍色表示該流水線階段是由GPU固定實現的,開發者沒有任何控制權。實線表示該shader必須由開發者編程實現,虛線表示該Shader是可選的.

2018-05-04 09:16:00 3613

3613

第一部分什么是流水線 第二部分什么時候用流水線設計 第三部分使用流水線的優缺點 第四部分流水線加法器舉例 一. 什么是流水線 流水線設計就是將組合邏輯系統地分割,并在各個部分(分級)之間插入寄存器

2018-09-25 17:12:02 4370

4370 如果有數字電路常識的人都知道,利用一塊組合邏輯電路去做8位的加法,其速度肯定比做2位的加法慢。因此這里可以采用4級流水線設計,每一級只做兩位的加法操作,當流水線一啟動后,除第一個加法運算之外,后面每經過一個2位加法器的延時,就會得到一個結果。

2019-02-04 17:20:00 7563

7563 流水線的工作方式就象工業生產上的裝配流水線。在CPU中由5—6個不同功能的電路單元組成一條指令處理流水線,然后將一條X86指令分成5—6步后再由這些電路單元分別執行,這樣就能實現在一個CPU時鐘周期完成一條指令,因此提高CPU的運算速度。

2019-11-29 07:06:00 2251

2251 流水線的平面設計應當保證零件的運輸路線最短,生產工人操作方便,輔助服務部門工作便利,最有效地利用生產面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時應考慮流水線的形式、流水線安裝工作地的排列方法等問題。

2019-11-28 07:07:00 2039

2039 流水線又稱為裝配線,一種工業上的生產方式,指每一個生產單位只專注處理某一個片段的工作。以提高工作效率及產量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網帶線、懸掛線及滾筒流水線這七類流水線。

2019-11-28 07:04:00 3232

3232 二進制加法器是半加器和全加法器形式的運算電路,用于將兩個二進制數字加在一起.

2019-06-22 10:56:38 24316

24316

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。

2019-06-19 14:19:17 7423

7423 加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用

2019-06-19 14:20:39 24786

24786

本文檔的主要內容詳細介紹的是使用流水線結構設計加法器的方案和工程文件免費下載

2020-09-07 18:21:28 3

3 加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用

2021-02-18 14:40:31 30941

30941

verilog實現加法器,從底層的門級電路級到行為級,本文對其做出了相應的闡述。

2021-02-18 14:53:52 5585

5585

介紹各種加法器的Verilog代碼和testbench。

2021-05-31 09:23:42 19

19 按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網帶線、懸掛線及滾筒流水線這七類流水線。

2021-07-05 11:12:18 6087

6087

流水線一、定義流水線是指在程序執行時多條指令重疊進行操作的一種準并行處理實現技術。各種部件同時處理是針對不同指令而言的,他們可同時為多條指令的不同部分進行工作。? 把一個重復的過程分解為若干個子過程

2021-10-20 20:51:14 6

6 。二、半加法器的實現在解釋這個半加法器之前,要明白計算機其實就是靠簡單電路集成起來的復雜電路而已,而構成這些復雜電路最簡單的邏輯電路就是“與”、“或”、“非”。而在他們的基礎之上進行組合,...

2021-11-11 12:06:03 20

20 本文解釋了流水線及其對 FPGA 的影響,即延遲、吞吐量、工作頻率的變化和資源利用率。

2022-05-07 16:51:10 4734

4734

電子發燒友網站提供《4位加法器開源分享.zip》資料免費下載

2022-07-08 09:33:21 3

3 行波進位加法器和超前進位加法器都是加法器,都是在邏輯電路中用作兩個數相加的電路。我們再來回顧一下行波進位加法器。

2022-08-05 16:45:00 886

886

jenkins 有 2 種流水線分為聲明式流水線與腳本化流水線,腳本化流水線是 jenkins 舊版本使用的流水線腳本,新版本 Jenkins 推薦使用聲明式流水線。文檔只介紹聲明流水線。

2023-05-17 16:57:31 613

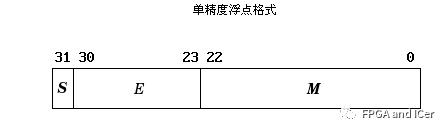

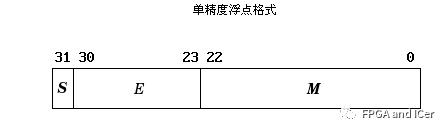

613 設計一個32bit浮點的加法器,out = A + B,假設AB均為無符號位,或者換個說法都為正數。

2023-06-02 16:13:19 590

590

有關加法器的知識,加法器是用來做什么的,故名思義,加法器是為了實現加法的,它是一種產生數的和的裝置,那么加法器的工作原理是什么,為什么要采用加法器,下面具體來看下。

2023-06-09 18:04:17 3481

3481 加法器可以是半加法器或全加法器。不同之處在于半加法器僅用于將兩個 1 位二進制數相加,因此其總和只能從 0 到 2。為了提高這種性能,開發了FullAdder。它能夠添加三個 1 位二進制數,實現從 0 到 3 的總和范圍,可以用兩個輸出位 (“11”) 表示。

2023-06-29 14:27:35 5478

5478

半加法器是一種執行二進制數相加的數字電路。它是最簡單的數字加法器,您只需使用兩個邏輯門即可構建一個;一個異或門和一個 AND 門。

2023-06-29 14:35:25 4648

4648

電子發燒友網站提供《4位加法器的構建.zip》資料免費下載

2023-07-04 11:20:07 0

0 鏡像加法器是一個經過改進的加法器電路,首先,它取消了進位反相門;

2023-07-07 14:20:50 1189

1189

,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。 但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號處理等方

2023-09-22 10:40:03 394

394

前段時間和幾個人閑談,看看在FPGA里面實現一個Mem加法器怎么玩兒

2023-10-17 10:22:25 279

279

![]()

電子發燒友App

電子發燒友App

評論