寬帶數字內容保護(HDCP)。本應用筆記介紹如何將攝像頭的RGB或YUV輸出轉換成標準顯示器接受的RGB數據。 攝像頭輸出數據格式 攝像頭芯片,例如OmniVision ?OV10630,可通過串行

2023-07-07 10:11:11 1106

1106

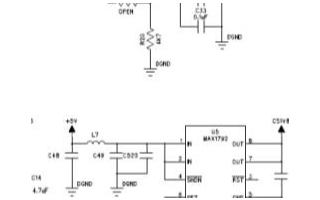

PMP9351 是一種適用于汽車輔助攝像機模塊的緊湊型電源和串行器解決方案,采用 OmniVision 圖像傳感器 OV10635。此參考板有兩個 LMR22007 同步降壓穩壓器,提供兩個 3.3V 輸出和一個 1.5V 輸出來為繞過板載 LDO 的 OV10635 評估板供電。

2015-04-20 15:00:15 2848

2848

串行數據傳輸:因為在芯片內部數據都是并行傳輸的,只是在芯片發送器一端轉換為串行形式

2023-10-08 16:15:26 5000

5000

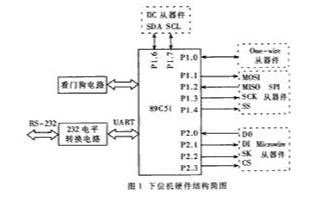

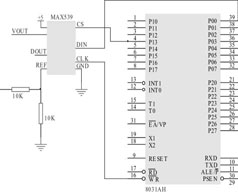

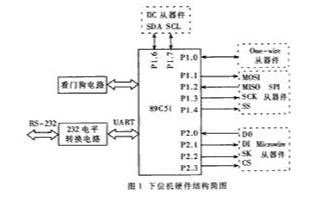

8250異步串行接口芯片的工作原理;掌握串行通信程序的設計。實驗內容:完成硬件測試環境;編寫程序對微機系統的串口進行自發自收外環測試;發送采用查詢方式,接收采用中斷方式;數據發送從鍵盤...

2022-01-19 06:04:49

各位有沒有比較便宜的8路AD芯片 SPI串行輸出,用了一個AD7888,太貴了。要求不高,只要溫度能在-25度到70度左右就好。精度位數都沒多少要求。

2015-11-13 17:07:00

概述:DS90UR905Q/906Q芯片組是5MHz-65MHz24位彩色FPD-LinkII串行化器和串并轉換器,能把并行RGB視頻接口轉換成高速串行接口。該串行總線配置通過消除時鐘和數據之間的偏移問題極大簡化了系統...

2021-04-12 06:29:15

概述:DS90UR906Q芯片組是一款5MHz-65MHz24位彩色FPD-LinkII串行化器和串并轉換器,能把并行RGB視頻接口轉換成高速串行接口。該串行總線配置通過消除時鐘和數據之間的偏移問題極大簡化了系統...

2021-04-07 06:03:25

串行異步收發器(UART).51 芯片的串口可以工作在幾個不同的工作模式下,其工作模式的設置就是使用SCON 寄存器。它的各個位的具體定義如下:SM0 SM1 SM2 REN TB8 RB8 TI

2021-11-18 06:02:06

串行模數轉換器MAX1241芯片是如何工作的?串行模數轉換器MAX1241芯片的轉化過程是怎樣的?

2021-04-12 06:12:43

通用性,穩定的數據存儲,各種規格容量,滿足了攝像頭模組對參數存儲的各種需求。就目前來看,普通的8M/13M及以上的攝像頭模組選用16-64K的EEPROM存儲器,帶OIS、雙攝像頭等功能的攝像頭模組

2016-12-16 11:01:04

1、 攝像頭數字信號處理芯片攝像頭數字信號處理芯片由鏡像信號處理器、JPEG圖像解碼器、USB設備控制器組成。DSP將感光芯片獲取的數據及時快速地傳到電腦中并刷新感光芯片,因此

2009-04-14 11:38:35

本帖最后由 qzq378271387 于 2012-8-17 14:20 編輯

攝像機CCD芯片與DSP類型

2012-08-17 14:19:32

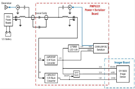

實現CMS后視鏡更換。從車輛后方來看,成像器的視頻數據輸入到TI的DS90UB933并行接口串行器或具有攝像串行接口(CSI)-2的DS90UB953串行器。然后將這些數據通過平板顯示器(FPD

2019-03-05 06:45:08

芯片解密基礎知識:串行端口的控制寄存器 串行端口控制寄存器有哪些類型?各自的工作方式是什么?下面由IC解密工程師詳解各類型的串行端口控制寄存器工作方式:串行端口共有2個控制寄存器SCON和PCON

2010-03-30 11:27:38

USB串行端口芯片

2023-03-28 15:05:25

USB串行端口芯片

2023-03-28 15:05:18

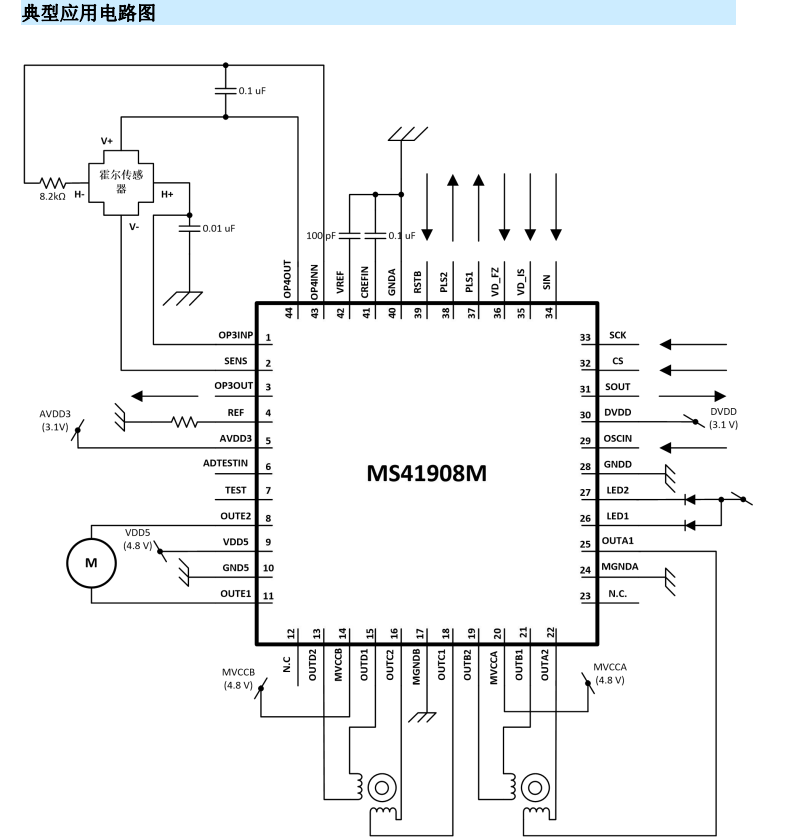

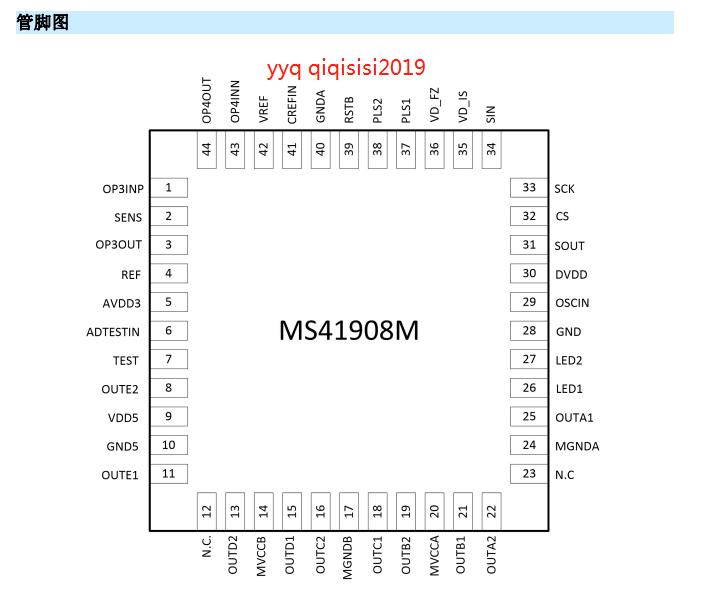

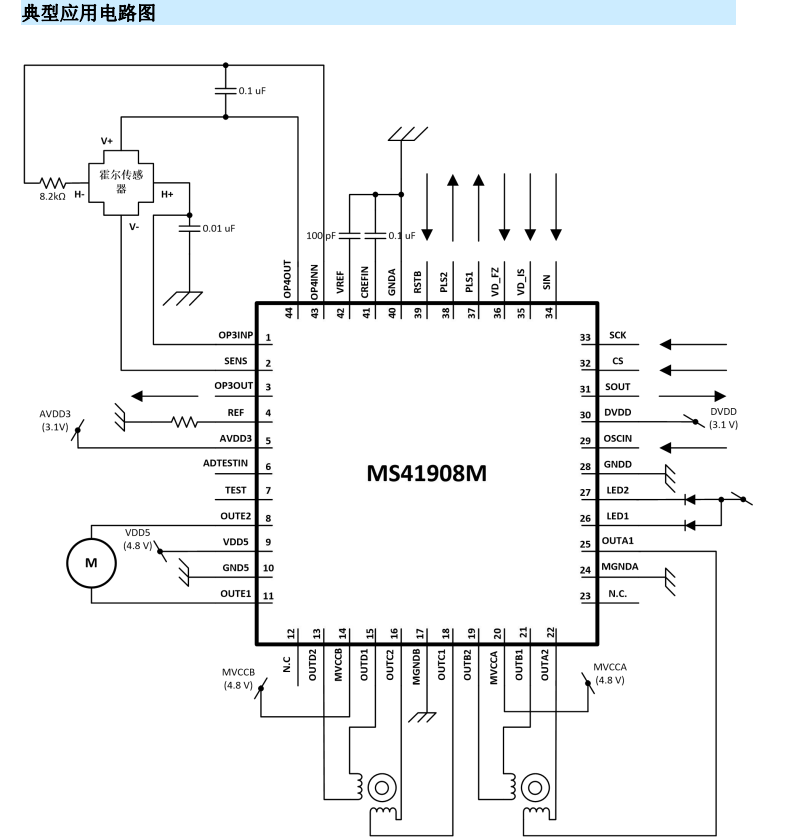

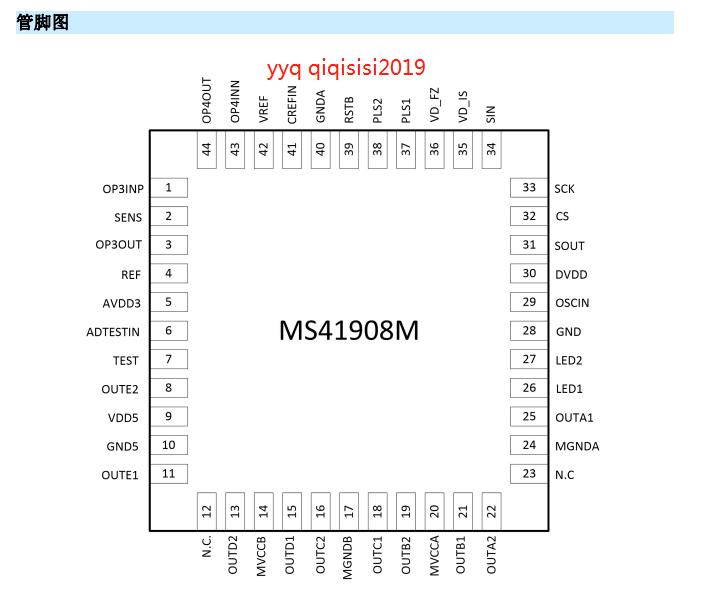

MS41908M 網絡攝像機·監控攝像機用鏡頭驅動芯片(內置光圈控制)MS41908M 是一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片。 芯片內置光圈控制功能;通過電壓驅動方式以及扭矩紋波修正技術

2021-02-28 14:29:36

MS41909MS41909MS41909產品描述:MS41909 是一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片。通過電壓驅動方式以及扭矩紋波修正技術,實現了超低噪聲微步驅動。產品特點:電壓驅動

2019-09-06 09:53:41

MS41918M是一款用于網絡攝像機和監控攝像頭的鏡頭驅動芯片。芯片內置光圈控制功能,通過電壓驅動方式以及扭矩紋波修技術,實現了超低噪聲微步驅動。主要特征:電壓驅動方式,256微步驅動電路(兩通

2019-07-29 17:28:23

MS41928M是瑞盟科技的一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片。芯片內置光圈控制功能;通過電壓驅動方式以及扭矩紋 波修正技術,實現了超低噪聲微步驅動。MS41928M集成了輸入輸出 IO

2021-11-10 14:17:51

MT9V034攝像頭模塊 MODULE_27.5X31.5MM 44.5mA

2023-03-28 13:06:39

攝像頭usb的連接方式我們常用的電腦攝像頭接口是USB接口,而常見的智能手機上的攝像頭是MIPI接口,還有一部分的攝像頭(比如說某些支持DVP接口的硬件)是DVP接口;通俗的講,USB是串行通用串行

2022-11-23 17:05:05

請問各位大神,RS232串行接口的串口攝像頭模塊 rs232攝像頭 紅外夜視 TTL可否用DSP控制?

2015-02-06 15:31:49

送入數據緩沖區,USB總線控制器從數據緩沖區中讀取數據。與計算機的通訊則通過USB接口實現。 2 USB數字攝像系統硬件2.1 EZ_USB 2131Q芯片介紹EZ_USB 2131Q內部框圖如圖2

2018-11-27 11:46:14

WIFI攝像頭模塊 MODULE_29X23MM 300mA 3.3~24V

2023-03-28 13:06:38

`本人對人臉識別技術非常感興趣,這次剛好看到了感光芯片雙目攝像頭的試用申請,果斷下手,并且非常榮幸獲得了測評的機會。我主要想要通過該款模組實現校園的人臉識別打卡,應用場景也包括進出校人員的自動識別

2020-08-28 19:01:20

(MCP),手機主板,PCBA,手機光板(新板),廢舊板,電阻,電容,電感,二三極管,MOS管,連接器等等。帝歐還回收ssd固態硬盤,回收服務器內存條,回收硬盤,回收cpu,回收芯片,回收傳感器,收購

2021-01-20 17:28:58

(MCP),手機主板,PCBA,手機光板(新板),廢舊板,電阻,電容,電感,二三極管,MOS管,連接器等等。帝歐還回收ssd固態硬盤,回收服務器內存條,回收硬盤,回收cpu,回收芯片,回收傳感器,收購

2021-05-07 19:26:41

(MCP),手機主板,PCBA,手機光板(新板),廢舊板,電阻,電容,電感,二三極管,MOS管,連接器等等。帝歐還回收ssd固態硬盤,回收服務器內存條,回收硬盤,回收cpu,回收芯片,回收傳感器,收購

2021-12-11 19:19:24

),手機主板,PCBA,手機光板(新板),廢舊板,電阻,電容,電感,二三極管,回收ssd固態硬盤,回收服務器內存條,回收硬盤,回收cpu,回收芯片,回收傳感器,收購連接器,收購鉭電容,回收sd卡,收購

2021-10-21 19:17:50

MAX9286吉比特多媒體串行鏈路(GMSL)解串器接收多達四個GMSL串行器的數據,采用50Ω同軸電纜或100Ω屏蔽雙絞線(STP)電纜,通過四個CSI-2通道輸出數據。每條串行鏈路具有嵌入式控制

2018-02-02 15:10:14

關于MAX9247/MAX9218串行器/解串器芯片組的性能測試詳細解析

2021-04-12 06:11:46

描述ADAS 傳感器互連板適合需要將諸如攝像頭、激光雷達或雷達模塊之類的遙感器連接到中央處理 ECU 的應用。此板支持多達 3 個同軸電纜輸入和 1 個 LVDS 雙絞線數據輸入,以及 3 條

2018-08-08 07:57:11

趙先生(TEL:135-3012-2202QQ:8798-21252)回收攝像頭芯片,收購攝像頭芯片,回收JX-F23A-C1-M3,JX-Q03,收購攝像頭芯片,攝像頭芯片全國高價回收,回收存儲類

2021-04-25 16:44:58

,回收服務器內存條,回收硬盤,回收cpu,回收芯片,回收傳感器,收購連接器,收購鉭電容,回收sd卡,收購tf卡。回收工廠庫存ic,大量收購工廠庫存ic,收購ic庫存料,收購電子庫存,回收電子元器件,收購

2021-08-12 19:09:06

芯片,國外的有索尼,OV,鎂光,聯詠,安霸,國內的有比亞迪微,格科微,銳芯微,思比科,中星微等等,這些品牌的圖像傳感器我們都高價回收。全新的感光芯片,攝像頭模組,拆機的CCD板,拆機的攝像頭,我們統統

2021-07-14 17:53:02

攝像頭,廣州回收索尼攝像頭,佛山回收索尼攝像頭,上海回收索尼攝像頭....全國高價大量收購攝像頭!我司幫助客戶消化積壓庫存電子料,資金雄厚,迅速幫你回籠資金。同時高價收購電子配件,包括液晶顯示屏,傳感器

2020-12-29 18:14:00

,格科微,銳芯微,思比科,中星微等等,這些品牌的圖像傳感器我們都高價回收。全新的感光芯片,攝像頭模組,拆機的CCD板,拆機的攝像頭,我們統統都回收。回收攝像頭,回收攝像頭芯片。 我們在深圳華強北,我們

2021-08-16 16:10:37

必須有足夠的gearing邏輯來支持快速串行傳感器接口。第三,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應現代攝像機對于緊湊外形的要求。具有完備子LVDS文檔支持的LatticeXP2非易失

2019-06-04 05:00:19

必須有足夠的gearing邏輯來支持快速串行傳感器接口。第三,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應現代攝像機對于緊湊外形的要求。具有完備子LVDS文檔支持的LatticeXP2非易失

2019-06-06 05:00:37

接口信號提供電信號支持。第二,FPGA的I/O必須有足夠的gearing邏輯來支持快速串行傳感器接口。第三,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應現代攝像機對于緊湊外形的要求。 具有

2018-11-05 11:08:31

如何用VHDL設計專用串行通信芯片?本文以開發統計時分復用器中的專用同步收發芯片為例,介紹整個芯片的開發流程。

2021-05-08 07:22:30

本文設計了一個用于串行總線芯片測試的實驗平臺?

2021-05-27 06:24:48

尋址 CMOS 攝像頭傳感器。但是,得益于 STMIPID02 MIPI CSI-2 解串行器離散元件,可以擴展可尋址攝像頭傳感器的范圍,如 MIPI? CSI-2 攝像頭(攝像頭串行接口)。

2023-09-07 08:16:41

請問一下有沒有采用EEPROM對大容量FPGA芯片數據實現串行加載的實際方案?

2021-04-08 06:01:39

應用。本文我們將探討串行解串器 (SerDes) 以及各種技術及其應用。串行解串器是可將大位寬并行總線壓縮成少量(通常為一條)差分串行鏈路的器件,該鏈路可在遠遠高于低速大位寬并行總線的速率下進行切換。串行

2018-09-13 09:54:18

描述TIDA-00138 參考設計是一種高速串行攝像頭接口,通過此接口,可將遠程汽車攝像頭模塊連接到顯示器或機器視覺處理系統。此設計使用 TI 的 FPD-Link III SerDes 技術,通過

2018-08-03 06:28:10

如何用EEPROM對大容量FPGA芯片數據實現串行加載?如何設計并-串轉換時序?

2021-04-29 07:13:12

求串行總線舵機芯片仿制,精通舵機編程,價格好商量!微信***

2017-02-17 22:38:09

求串行總線舵機芯片設計,價錢面議。微信***

2017-02-14 21:15:32

頭、DS90UB913A-Q1 FPD-Link 串行器芯片組和時鐘振蕩器提供 1.5V、1.8V 和 3.3V 的低噪聲電壓軌。主要特色適用于 CMOS 傳感器和串行器的空間優化型電源管理解決方案成本優化解決方案關于系統

2018-11-13 16:43:13

`瑞盟MS41909可提供樣板 產品描述:MS41909是一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片,通過電壓驅動方式以及扭矩紋修正技術,實現了超低噪聲微步驅動。產品特點:1.電壓驅動方式,256

2019-10-21 17:05:05

MS41918MMS41918MMS41918M產品描述:MS41918M是一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片。 芯片內置光圈控制功能,通過電壓驅動方式以及扭矩紋波修正技術,實現了超低

2019-09-26 09:43:57

MS41918M是瑞盟科技推出的一款用于網絡攝像機和監控攝像機的鏡頭驅動片。芯片內置光圈控制功能;通過電壓驅動方式以及扭矩紋波修正技術,實現了超低噪聲微步驅動。主要特點:■電壓驅動方式,256 微步

2021-10-21 11:32:30

Netscape)即可監視其影像。網絡攝像機內置一個嵌入式芯片,采用嵌入式實時操作系統。攝像機傳送來的視頻信號數字化后由高效壓縮芯片壓縮,通過網絡總線傳送到Web服務器。網絡上用戶可以直接用瀏覽器觀看Web服務器上的攝像機圖像,授權用戶還可以控制攝像機云臺鏡頭的動作或對系統配置進行操作。

2008-12-29 14:11:49

誰介紹一款FPGA出串行高速2711串行接口芯片

2015-05-25 10:41:52

! 現在,咱們就先來看看“汽車電子參考設計”的第5期有什么好的推薦吧! 了解更多,點擊此處獲取本參考設計的原文介紹。 設計概述PMP9351 是一種適用于汽車輔助攝像機模塊的緊湊型電源和串行器解決方案,采用 OmniVision 圖像傳感器 OV10635。此參考板有兩個 LMR22007 同步降壓穩壓器,提供兩個 3…

2022-11-22 06:04:32

手機攝像頭就選帝歐電子專業回收!深圳高價回收手機攝像頭,深圳回收手機攝像頭,深圳收購手機攝像頭,深圳帝歐電子高價回收手機攝像頭。帝歐還長期回收ssd固態硬盤,回收服務器內存條,回收硬盤,回收cpu

2021-03-10 17:40:36

重慶收購攝像頭芯片重慶高價回收手機攝像頭芯片,回收攝像頭芯片,回收手機攝像頭芯片。深圳帝歐專業電子回收。帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com。本

2021-01-23 17:19:45

重慶收購攝像頭芯片重慶高價回收手機攝像頭芯片,回收攝像頭芯片,回收手機攝像頭芯片。深圳帝歐專業電子回收。帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com。本

2021-06-28 19:23:38

重慶收購攝像頭芯片重慶高價回收手機攝像頭芯片,回收攝像頭芯片,回收手機攝像頭芯片。深圳帝歐專業電子回收。帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com。本

2021-11-30 19:35:14

長期收購索尼攝像芯片惆悵孤帆連夜發,送行淡月微云。尊前不用翠眉顰。人生如逆旅,我亦是行人。深圳高價收購索尼攝像芯片,專業回收索尼攝像芯片。深圳帝歐電子專業多年回收電子呆料。帝歐趙生

2021-04-22 19:13:43

摘要:介紹了一種基于I2C總線接口的多功能串行芯片X1288

2006-03-11 11:49:58 881

881

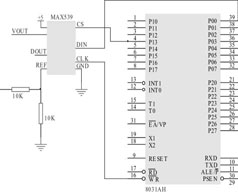

本文簡單介紹MAXIM公司生產的串行AD芯片MAX1241及串行DA芯片MAX539的接口及編程, 并簡要介紹SPI總線的使用方法。關鍵詞:串行AD;串行DA;SPI總線

2009-06-16 07:50:16 7243

7243

用VHDL設計專用串行通信芯片

一種專用串行同步通信芯片(該芯片內部結構和操作方式以INS8250為參考)的VHDL設計及CPLD實現,著重介紹了用VHDL及CPLD設計專用通信芯片的

2009-10-12 19:07:48 1701

1701

MAX9259/MAX9260吉比特串行器/解串器芯片組(Maxim)

Maxim為其高速LVDS串行器/解串器(SerDes)產品線增添新成員:

2010-04-17 10:26:48 1111

1111 Maxim推出吉比特串行器/解串器芯片組--MAX9259/MAX9260 Maxim為其高速LVDS串行器/解串器(SerDes)產品線增添新成員:MAX9259/MAX9260 SerDes芯片組。該吉比特多媒

2010-04-17 16:30:01 726

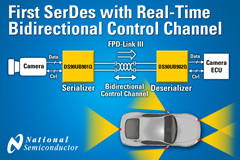

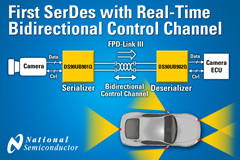

726 美國國家半導體公司(National Semiconductor Corporation)宣布推出一系列全新 FPD-Link III車用級串行/解串器芯片組。這是業界首系列可為輔助駕駛系統攝像機提供一條實時雙向控制通道的

2010-06-22 09:41:04 2325

2325

美國國家半導體公司(National Semiconductor Corporation)宣布推出一系列全新 FPD-Link III車用級串行/解串器芯片組。

這是業界首系列可為輔助駕駛系統攝像機提供

2010-06-29 14:36:34 2420

2420 根據可編程串行接口芯片8251A標準及功能,劃分其功能模塊,使用ISE和Modelsim軟件,利用VHDL語言完成了8251A的邏輯設計、功能仿真、綜合實現和布局布線,使用ISE的iMPACT工具將生成的配置

2011-12-28 10:32:41 62

62 基于串行芯片AD7887的粉塵濃度信號檢測系統的設計

2016-01-04 15:26:58 22

22 10位串行模數轉換芯片AD7810的原理及應用。

2016-01-15 17:25:07 25

25 用VHDL設計專用串行通信芯片,下來看看。

2016-12-20 18:02:50 10

10 JX-H22晶相攝像頭芯片

2017-02-25 17:30:21 6

6 德州儀器(TI)近日宣布推出業界首款符合MIPI攝像頭串行接口2(CSI-2)規格的雙端口四通道解串器集線器。新型汽車用集線器可同時聚集并復制多達四個攝像頭的高分辨率數據。

2017-08-22 08:53:28 14

14 本文主要介紹了國內攝像頭芯片的十大產商排名狀況。攝像頭作為一種視頻輸入設備,目前在我們生活中已經得到普遍的運用。

2018-04-08 09:47:38 96017

96017

本文主要介紹了攝像頭芯片型號有哪些_攝像頭芯片型號匯總。攝像頭主要有鏡頭、CCD圖像傳感器、預中放、AGC、A/D、同步信號發生器、CCD驅動器、圖像信號形成電路、D/A轉換電路和電源的電路構成

2018-04-09 08:49:03 58345

58345

串行 EEPROM 芯片串行 AT24C08C Atmel 的 AT24C08C 提供 8192 位串行電可擦除可編程只讀存儲器( EEPROM ),每個存儲單元有 1024 字,每個

2018-04-13 16:18:02 7174

7174

貿澤電子 (Mouser Electronics) 即日起開始分銷 Texas Instruments (TI) 的DS90UB935-Q1串行器。此面向汽車應用的串行器是TI FPD-Link

2019-01-01 11:49:00 3460

3460 DSP芯片對攝像機起著重要作用,它大大改觀了傳統攝像機的技術。在攝像機應用中,經過光學成像芯片產生的信號不可避免存在很多缺陷,如圖像細節信號弱、亮度不均勻、色彩不自然等,必須經過DSP對信號進行放大和校正。作為攝像機的核心元器件的DSP處理芯片,其性能優劣直接決定攝像機監控畫面的品質情況。

2020-05-09 15:52:31 2410

2410 應用串行接口芯片擴展系統時,在初步選擇了串行接口的芯片后,為了對芯片的資源更好地了解,開發者一般在系統設計前搭建一個簡單的硬件電路并編制相應的軟件對其測試,待性能驗證后再確定最終的設計方案?本文根據這一需要設計了一個用于串行總線芯片測試的實驗平臺?

2021-06-15 16:28:00 1717

1717

MR25H256是一個串行MRAM,具有使用串行外圍設備接口的芯片選擇(CS),串行輸入(SI),串行輸出(SO)和串行時鐘(SCK)的四針接口在邏...

2022-01-26 18:07:52 0

0 【汽車電子參考設計精選—5】用于汽車攝像機模塊的電源和串行器參考設計

2022-11-04 09:52:26 1

1 串行和平行通道芯片設計均采用標準 SU-8 光刻技術在 4“ 硅片上制造。

2023-02-21 16:53:51 538

538 一、產品簡述 MS41908M 是一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片。 芯片內置光圈控制功能;通過電壓驅動方式以及扭矩紋波修正技術,實現了超低噪聲微步驅動。 二、主要特點 電壓驅動方式

2023-05-15 19:09:35 903

903

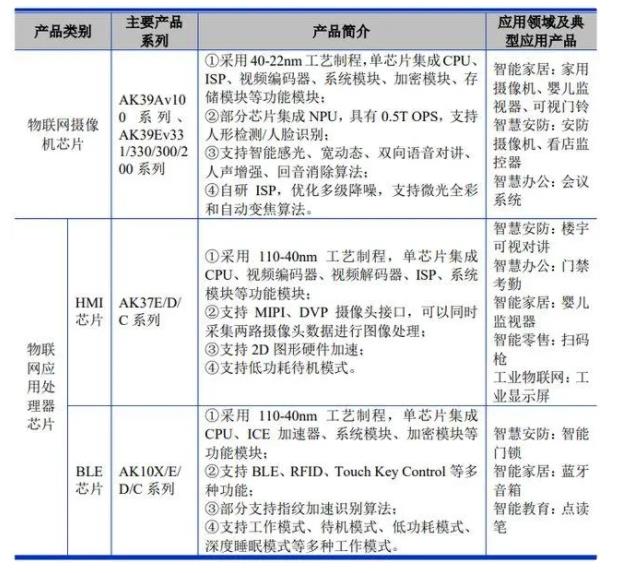

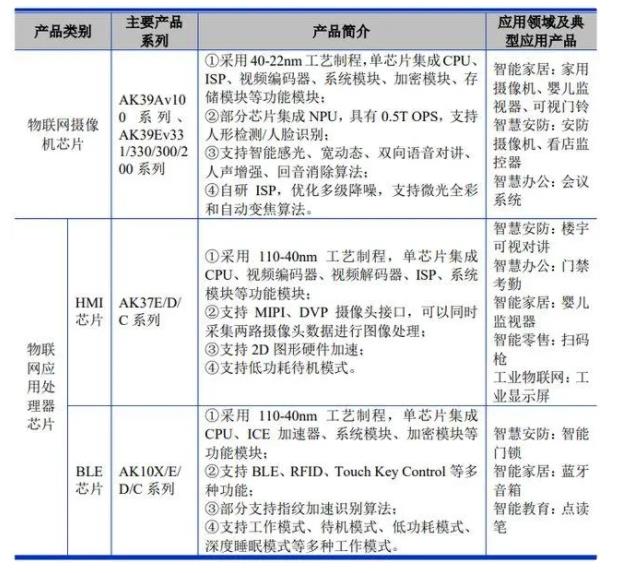

物聯網攝像機芯片方案商安凱微電子登錄科創板 廣州安凱微電子股份有限公司今日開啟申購登陸科創板;安凱微電子主營業務是物聯網智能硬件核心SoC芯片的研發、設計、終測和銷售。產品包括監控攝像機芯片、考勤機芯片

2023-06-13 15:55:36 777

777

汽車電子車載攝像頭感光芯片底部填充膠應用由漢思新材料提供汽車電子車載攝像頭感光芯片底部填充膠應用通過和客戶工作人員詳細溝通了解到;客戶生產產品是:汽車電子車載攝像頭需求原因:新產品開發需要

2023-05-17 16:56:42 464

464

攝像眼鏡POP芯片用底部填充膠應用案例分析由漢思新材料提供。客戶用膠產品為攝像眼鏡攝像眼鏡是款具有高清數碼攝像和拍照功能的太陽鏡,內置存儲器,又名“太陽鏡攝像機,可拍攝照片和高畫質視頻。主要功能

2023-06-12 17:13:09 613

613

MS41908M 是一款用于網絡攝像機和監控攝像機的鏡頭驅動芯片。芯片內置光圈控制功能;通過電壓驅動方式以及扭矩紋波修正技術,實現了超低噪聲微步驅動 主要特點 ?電壓驅動方式,256 微步驅動電路

2023-08-24 14:33:46 370

370

電子發燒友App

電子發燒友App

評論