電路功能與優(yōu)勢(shì)

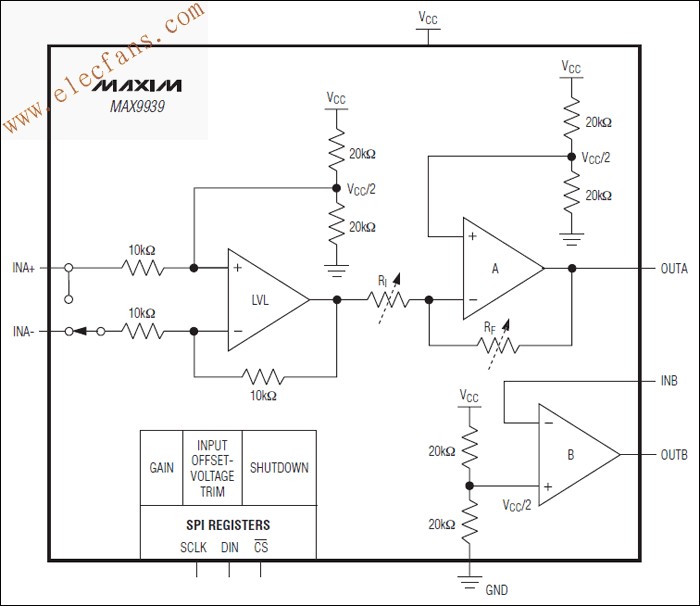

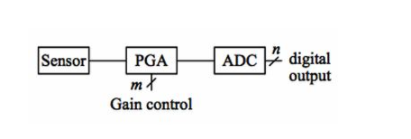

圖1所示電路是一款雙通道色度計(jì),其具有一個(gè)調(diào)制光源發(fā)射器,各通道上有可編程增益跨阻放大器,后接一個(gè)噪聲非常低的24位Σ-Δ型模數(shù)轉(zhuǎn)換器(ADC)。 ADC的輸出連接到一個(gè)標(biāo)準(zhǔn)FPGA夾層卡。 FPGA從ADC獲得采樣數(shù)據(jù),實(shí)現(xiàn)一個(gè)同步檢波算法。

通過(guò)使用調(diào)制光和數(shù)字同步檢波而非恒流(直流)源,系統(tǒng)可有力地抑制非調(diào)制頻率的噪聲源,提供出色的精度。

該雙通道電路以三種不同的波長(zhǎng)測(cè)量樣本與參考容器中的液體的吸收光線之比。 這種測(cè)量方法構(gòu)成許多通過(guò)吸收光譜測(cè)量濃度和表征材料的化學(xué)分析和環(huán)境監(jiān)控儀器儀表的基礎(chǔ)。

圖1. 帶可編程增益跨阻放大器和鎖定放大器的雙通道色度計(jì)(原理示意圖: 未顯示所有連接和去耦)

電路描述

一個(gè)設(shè)置為用戶可編程頻率的時(shí)鐘利用一個(gè)恒流驅(qū)動(dòng)器調(diào)制三種LED顏色中的一種,該恒流驅(qū)動(dòng)器由運(yùn)算放大器AD8615、開(kāi)關(guān)ADG819和數(shù)字電位計(jì) AD5201構(gòu)成。分光鏡將一半光線通過(guò)樣本容器發(fā)送,另一半通過(guò)參考容器發(fā)送。 配置為跨阻放大器的ADA4528-1隨后將光電二極管電流轉(zhuǎn)換為輸出電壓方波,其幅度與從樣本或參考容器透射出來(lái)的光線成正比。 跨阻放大器利用單刀雙擲(SPDT)開(kāi)關(guān)ADG633選擇兩個(gè)跨阻增益中的一個(gè)。AD7175-2 Σ-Δ ADC對(duì)電壓進(jìn)行采樣,并將數(shù)字?jǐn)?shù)據(jù)發(fā)送到FPGA進(jìn)行數(shù)字解調(diào)。

FPGA首先將一個(gè)以數(shù)字方式生成的正弦波與LED時(shí)鐘同步,然后將此正弦波與ADC采樣數(shù)據(jù)相乘,從而實(shí)現(xiàn)同步解調(diào)。 此外,該正弦波的90°相移版本也與ADC數(shù)據(jù)相乘以獲得調(diào)制信號(hào)的正交分量。 這些操作的結(jié)果是產(chǎn)生兩個(gè)低頻解調(diào)信號(hào),分別代表各通道接收光線的同相和正交分量。 一個(gè)窄帶FIR低通濾波器濾除所有其他頻率成分,這樣便很容易計(jì)算光電二極管測(cè)得的信號(hào)的幅度和相移,而與LED時(shí)鐘不同的頻率的光線或電氣噪聲則被抑制。 多路復(fù)用器ADG704將供電軌連接至三種顏色LED中的一個(gè),用戶可以通過(guò)2位地址選擇測(cè)試波長(zhǎng)。AD8615和NPN晶體管構(gòu)成一個(gè)簡(jiǎn)單的電流源,LED電流由下式給出:

其中:

VNON-INVERTING為AD8615同相輸入端電壓。

ADG819 SPDT開(kāi)關(guān)連接到設(shè)定點(diǎn)電壓和地,其控制引腳連接到參考時(shí)鐘。 當(dāng)時(shí)鐘在高低之間振蕩時(shí),電流源的設(shè)定點(diǎn)從0 mA變?yōu)樗璧妮敵鲭娏鳎瑥亩a(chǎn)生一個(gè)方波信號(hào)。

數(shù)字電位計(jì)AD5201充當(dāng)2.5 V基準(zhǔn)電壓源的可編程電阻分壓器,使得LED電流共有33種不同的電流輸出設(shè)置。

樣本和參考容器各接收LED光能的一半,吸收的光量取決于每個(gè)容器中介質(zhì)的類型和濃度。 每個(gè)容器另一側(cè)的光電二極管產(chǎn)生少量電流,數(shù)量與接收到的光量成比例。

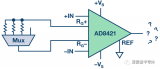

每個(gè)接收器通道的第一級(jí)包含ADA4528-1運(yùn)算放大器,該運(yùn)算放大器配置為跨阻放大器,可將光電二極管輸出電流轉(zhuǎn)換為電壓。 ADA4528-1是一款自穩(wěn)零放大器,其所導(dǎo)致的失調(diào)可忽略不計(jì),無(wú)1/f噪聲,寬帶噪聲則非常低(5.9 nV/√Hz)。 像所有自穩(wěn)零放大器一樣,在自穩(wěn)零頻率處會(huì)出現(xiàn)一個(gè)噪聲尖峰。 對(duì)于ADA4528-1,該頻率約為200 kHz,但電路信號(hào)帶寬早在此之前即發(fā)生滾降。

運(yùn)算放大器輸入偏置電流乘以輸出端的反饋電阻值,作為失調(diào)電壓。 運(yùn)算放大器的輸入失調(diào)電壓出現(xiàn)在輸出端會(huì)被放大,其增益取決于反饋電阻和光電二極管分流電阻。 此外,運(yùn)算放大器的任何輸入電壓失調(diào)都會(huì)出現(xiàn)在光電二極管上,導(dǎo)致光電二極管暗電流增加。ADA4528-1的失調(diào)電壓很低(2.5 μV),非常適合這種應(yīng)用。

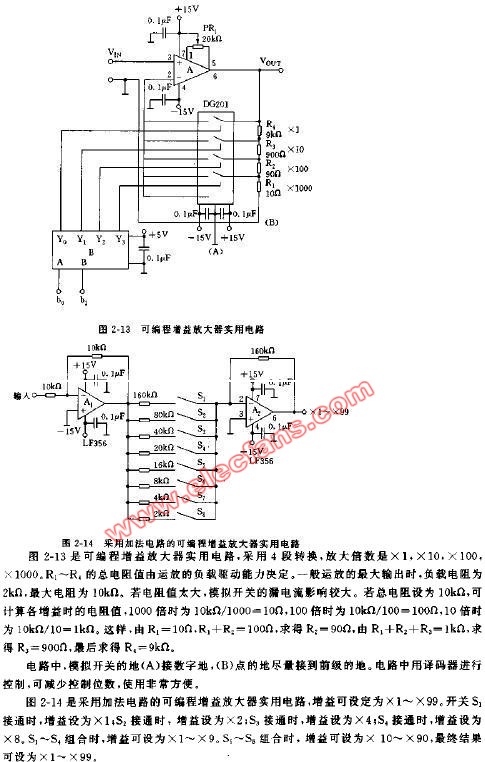

圖2顯示了一個(gè)帶單反饋電阻的典型跨阻放大器及其理想傳遞函數(shù)。

圖2. 跨阻放大器傳遞函數(shù)

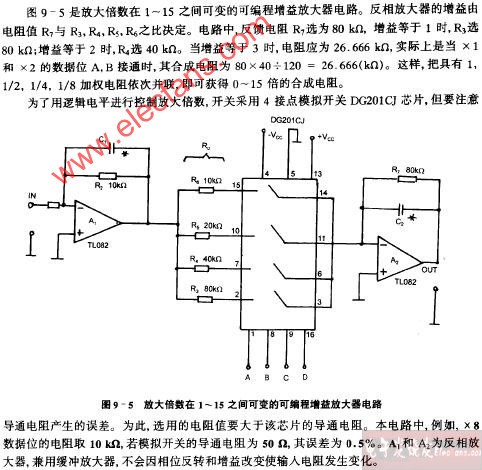

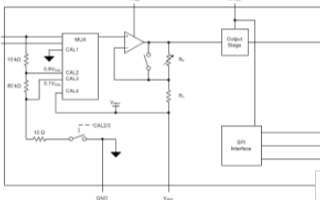

由于某些受測(cè)溶液可能具有非常強(qiáng)的吸收特性,因此有時(shí)需要使用大反饋電阻來(lái)測(cè)量光電二極管產(chǎn)生的極小電流,同時(shí)要能夠測(cè)量與高度稀釋溶液相對(duì)應(yīng)的大電流。 為了解決這一難題,圖1中的光電二極管放大器含有兩個(gè)不同的可選增益。 其中一個(gè)增益設(shè)為33 kΩ,另一個(gè)設(shè)為1 MΩ。 當(dāng)單SPDT開(kāi)關(guān)連接運(yùn)算放大器的輸出端以便開(kāi)關(guān)反饋電阻時(shí),ADG633的導(dǎo)通電阻會(huì)導(dǎo)致跨阻增益誤差。 為了避免這個(gè)問(wèn)題,圖3顯示了一種較好的配置,在該配置中,反饋環(huán)路內(nèi)部的ADG633選擇所需電阻,同時(shí)第二個(gè)開(kāi)關(guān)將系統(tǒng)下一級(jí)與所選反饋環(huán)路相連。 放大器輸出端的電壓為:

而不是

它表示增益誤差。 但是,由于其中一個(gè)ADG633位于反饋環(huán)路之外,該級(jí)的輸出阻抗即為ADG633的導(dǎo)通電阻(通常52 Ω),而非閉環(huán)工作時(shí)與運(yùn)算放大器輸出有關(guān)的極低輸出阻抗。ADG633漏電流(典型值5 pA)引起的誤差可忽略不計(jì)。

哪怕諸如ADA4528-1這類最好的軌到軌輸出放大器,其輸出都無(wú)法完全擺動(dòng)至供電軌。 此外,ADA4528-1上的輸入失調(diào)電壓可以為負(fù),雖然其數(shù)值非常小。 運(yùn)算放大器ADA4805-1不是通過(guò)一個(gè)負(fù)電源來(lái)保證放大器絕不削波,并且保證它能驅(qū)動(dòng)至0.0 V,而是提供一個(gè)100 mV緩沖電壓來(lái)偏置光電二極管陽(yáng)極和ADA4528-1。ADA4805-1非常適合用作基準(zhǔn)電壓緩沖器,因?yàn)楫?dāng)驅(qū)動(dòng)去耦用大容性負(fù)載時(shí),它能保持單位增益穩(wěn)定性。 另外還使用第二個(gè)ADA4805-1來(lái)緩沖用以設(shè)置LED電流的數(shù)字電位計(jì)AD5201輸出。

圖3. 可編程增益跨阻放大器

光電二極管放大器輸出電壓可在0.1 V至5.0 V范圍內(nèi)擺動(dòng)。對(duì)于33 kΩ范圍而言,4.9 V輸出范圍對(duì)應(yīng)148.5 μA的滿量程光電二極管電流。 對(duì)于1 MΩ范圍,其對(duì)應(yīng)4.9 μA的滿量程光電二極管電流。 使用1 MΩ的增益設(shè)置工作時(shí),務(wù)必保護(hù)光電二極管不受外界光線影響,以防放大器飽和。 雖然下文所述的同步檢波方案能夠有力地衰減任何不與LED時(shí)鐘同步的頻率,但若ADC返回飽和數(shù)據(jù),檢波方案將無(wú)法正常工作。

各通道的增益設(shè)置可通過(guò)FPGA板獨(dú)立選擇。

ADC采樣速率和調(diào)制頻率選擇

AD7175-2 ADC配置有sinc5+sinc1濾波器,輸出數(shù)據(jù)速率為250 kSPS,可采樣單周期建立對(duì)兩個(gè)通道采樣。這種配置使得各通道的有效采樣速率為25 kSPS(各通道每隔40 μs輸出數(shù)據(jù))。 任何高于12.5 kHz的頻率(例如方波調(diào)制的奇數(shù)諧波)都會(huì)混疊回到ADC通帶中,只要其不是剛好位于調(diào)制頻率之上,同步解調(diào)級(jí)就會(huì)抑制這些頻率。 為了防止調(diào)制波形的混疊頻率折回到基頻,應(yīng)根據(jù)以下關(guān)系選擇調(diào)制頻率:

其中:

FMODULATION為調(diào)制頻率。

FSAMPLE為ADC有效輸出數(shù)據(jù)速率。

n為整數(shù)(對(duì)應(yīng)于調(diào)制頻率的諧波)。

例如在本系統(tǒng)中,有效輸出數(shù)據(jù)速率為25 kSPS,因此,如果需要1 kHz左右的調(diào)制頻率,該頻率必須是1020 Hz (n = 12)或943 Hz (n = 13)以避免混疊問(wèn)題。 采樣這種方法選擇調(diào)制頻率,前端即無(wú)需使用陡峭的抗混疊濾波器。

數(shù)字同步檢波

本電路不是在硬件中實(shí)現(xiàn)同步檢波,而是獲得時(shí)間采樣數(shù)據(jù)并利用FPGA實(shí)現(xiàn)數(shù)字同步檢波。 圖4是FPGA中實(shí)現(xiàn)的數(shù)字同步檢波模塊的示意圖。 FPGA產(chǎn)生交流激勵(lì)信號(hào)驅(qū)動(dòng)LED,以數(shù)字方式產(chǎn)生的正弦波在數(shù)字鎖相環(huán)中鎖定該信號(hào)。 輸入信號(hào)與數(shù)字正弦波和90°相移版本相乘,產(chǎn)生兩個(gè)低頻解調(diào)信號(hào),其分別與輸入信號(hào)在調(diào)制頻率的同相和正交分量成正比。 如圖4所示,幅度為這兩個(gè)分量的平方和之根。 有關(guān)該解調(diào)技術(shù)的更多信息,請(qǐng)參閱“了解詳情”部分。

圖4. 包括FPGA同步檢波器的系統(tǒng)框圖

電源

EVAL-CN0363-PMDZ板由外部6 V至12 V直流電源供電。

電路的模擬部分由來(lái)自低壓差穩(wěn)壓器ADP7102的AVDD = 5 V供電。 電路的數(shù)字部分由低壓差穩(wěn)壓器ADP1720產(chǎn)生的IOVDD = 3.3 V供電。 或者,IOVDD也可以通過(guò)鏈路選項(xiàng)由PMOD連接器VCC提供。

2.5 V基準(zhǔn)電壓由AD7175-2 ADC的內(nèi)部2.5 V基準(zhǔn)源提供。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論