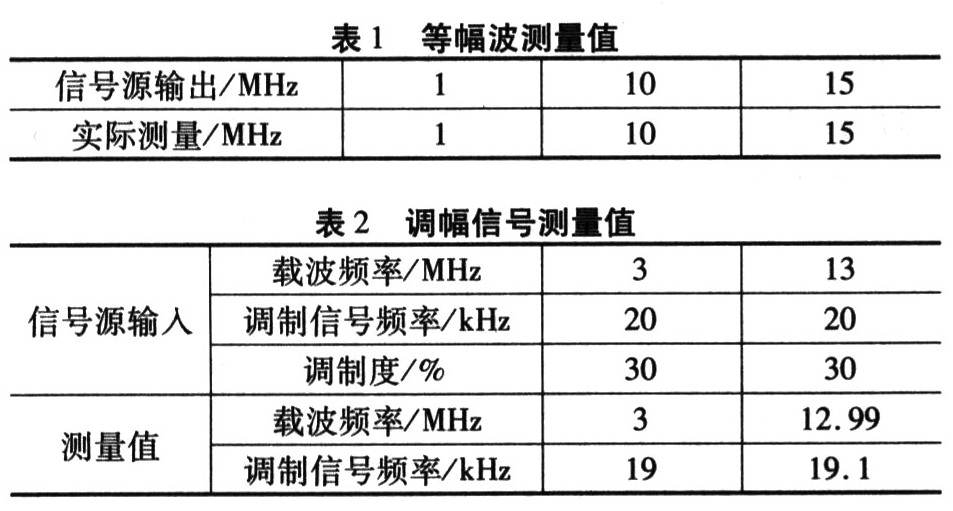

直接數字頻率合概述

DDS同DSP(數字信號處理)一樣,也是一項關鍵的數字化技術。DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。DDS是從相位概念出發直接合成所需要波形的一種新的頻率合成技術。

直接數字頻率合成是一種新的頻率合成技術和信號產生的方法,具有超高速的頻率轉換時間、極高的頻率分辨率分辨率和較低的相位噪聲,在頻率改變與調頻時,DDS能夠保持相位的連續,因此很容易實現頻率、相位和幅度調制。此外,DDS技術大部分是基于數字電路技術的,具有可編程控制的突出優點。因此,這種信號產生技術得到了越來越廣泛的應用,很多廠家已經生產出了DDS專用芯片,這種器件成為當今電子系統及設各中頻率源的首選器件。

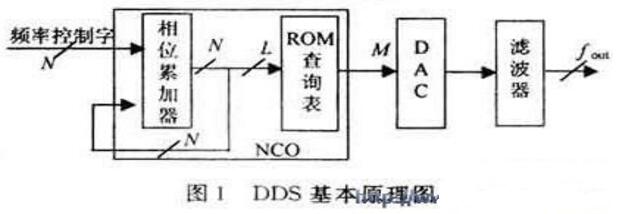

直接數字頻率合成原理

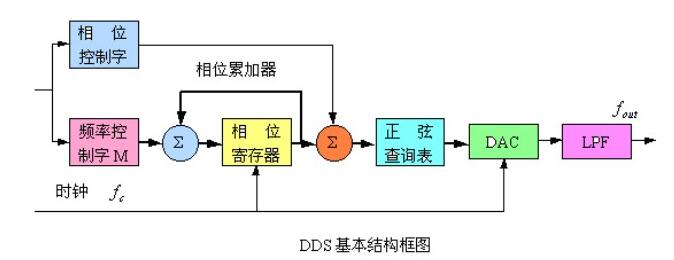

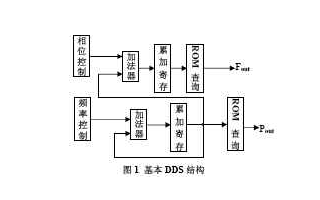

工作過程為:

1、將存于數表中的數字波形,經數模轉換器D/A,形成模擬量波形。

2、兩種方法可以改變輸出信號的頻率:

(1)改變查表尋址的時鐘CLOCK的頻率,可以改變輸出波形的頻率。

(2)、改變尋址的步長來改變輸出信號的頻率.DDS即采用此法。步長即為對數字波形查表的相位增量。由累加器對相位增量進行累加,累加器的值作為查表地址。

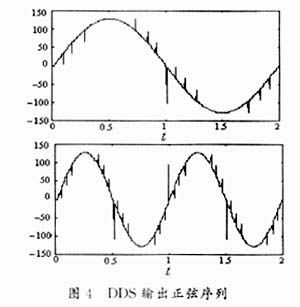

3、D/A輸出的階梯形波形,經低通(帶通)濾波,成為質量符合需要的模擬波形。

直接數字頻率合成系統的構成

直接數字頻率合成主要由標準參考頻率源、相位累加器、波形存儲器、數/模轉換器、低通平滑濾波器等構成。其中,參考頻率源一般是一個高穩定度的晶體振蕩器,其輸出信號用于DDS中各部件同步工作。DDS的實質是對相位進行可控等間隔的采樣。

直接數字頻率合成優缺點

優點:

(1)輸出頻率相對帶寬較寬

輸出頻率帶寬為50%fs(理論值)。但考慮到低通濾波器的特性和設計難度以及對輸出信號雜散的 抑制,實際的輸出頻率帶寬仍能達到40%fs。

(2)頻率轉換時間短

DDS是一個開環系統,無任何反饋環節,這種結構使得DDS的頻率轉換時間極短。事實上,在 DDS的頻率控制字改變之后,需經過一個時鐘周期之后按照新的相位增量累加,才能實現頻率的轉 換。因此,頻率時間等于頻率控制字的傳輸,也就是一個時鐘周期的時間。時鐘頻率越高,轉換時 間越短。DDS的頻率轉換時間可達納秒數量級,比使用其它的頻率合成方法都要短數個數量級。

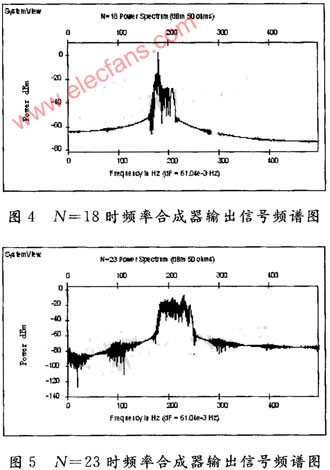

(3)頻率分辨率極高

若時鐘fs的頻率不變,DDS的頻率分辨率就是則相位累加器的位數N決定。只要增加相位累加器的 位數N即可獲得任意小的頻率分辨率。目前,大多數DDS的分辨率在1Hz數量級,許多小于1mHz甚 至更小。

(4)相位變化連續

改變DDS輸出頻率,實際上改變的每一個時鐘周期的相位增量,相位函數的曲線是連續的,只是在 改變頻率的瞬間其頻率發生了突變,因而保持了信號相位的連續性。

(5)輸出波形的靈活性

只要在DDS內部加上相應控制如調頻控制FM、調相控制PM和調幅控制AM,即可以方便靈活地實 現調頻、調相和調幅功能,產生FSK、PSK、ASK和MSK等信號。另外,只要在DDS的波形存儲器 存放不同波形數據,就可以實現各種波形輸出,如三角波、鋸齒波和矩形波甚至是任意的波形。當 DDS的波形存儲器分別存放正弦和余弦函數表時,既可得到正交的兩路輸出。

(6)其他優點

由于DDS中幾乎所有部件都屬于數字電路,易于集成,功耗低、 體積小、重量輕、可靠性高,且易于程控,使用相當靈活,因此性價 比極高。

缺點:

DDS也有局限性,主要表現在:

(1)輸出頻帶范圍有限

由于DDS內部DAC和波形存儲器(ROM)的工作速度限 制,使得DDS輸出的最高頻有限。目前市場上采用CMOS、 TTL、ECL工藝制作的DDS工習片,工作頻率一般在幾十 MHz至400MHz左右。采用GaAs工藝的DDS芯片工作頻 率可達2GHz左右。

(2)輸出雜散大

由于DDS采用全數字結構,不可避免地引入了雜散。其來 源主要有三個:相位累加器相位舍位誤差造成的雜散;幅 度量化誤差(由存儲器有限字長引起)造成的雜散和DAC 非理想特性造成的雜散。

直接數字式頻率合成器基本技術實現方案

(1)采用高性能的DDS單片電路解決方案

隨著DDS技術和VLSI的發展,DDS單片化在九十年代就已經完成。由于DDS芯片性能日漸完善,促成了許多DDS芯片生產廠家出現,它們推出了許多性能優越的DDS芯片,為電路設計者提供了多種選擇。其中AD公司的DDS系列產品性價比較高,目前取得了極為廣泛的應用。

(2)自行設計基于可編程器件的解決方案

由于可編程邏輯器件的規模大、速度快、可編程,以及有強大的EDA軟件支持等特性,十分適合實現DDS系統的數字部分。在高可靠性的應用領域,如果設計合理得當,將不會存在類似MCU的復位不可靠等問題。而且由于它的高度集成,完全可以將整個系統下載到同一個芯片當中,實現所謂的片上系統,從而大大縮小產品的體積,提高了系統的可靠性。

(3)基于FPGA的DDS系統合成方案

通過FPGA控制DDS產生線性調頻信號及跳頻信號。基于FPGA的DDS系統技術可以產生多種調制方式以及多種組合方式,并且可以實現多個DDS芯片的功能,更加集成。

事實上,除了這三種基礎合成方案外,還可考慮這三種方案的優勢組合,形成新的方案。

直接數字頻率合成系統實現

1、DSP及DDS芯片介紹

本次設計采用DSP控制DDS實現頻率合成器。使用TI公司生產的DSP處理器TMS320VC5402和ADI公司生產的DDS芯片AD9835,下面分別對這兩個芯片做簡單介紹。

數字信號處理器(DSP)是在模擬信號變換成數字信號以后進行高速實時處理的專用處理器,其處理速度比最快的通用CPU還快1O一50倍。在當今的數字化時代,DSP己成為通信、計算機、消費類電子產品等領域的基礎器件,被稱為信息社會革命的旗手。

VC5402是TI公司1999年10月推出性價比較高的定點數字信號處理器,VC5402具有先進的改進型哈佛結構,操作速率可達100MIPS;多總線結構。VC5402的存儲器的配置比較靈活,主要由模式寄存器PMST里的OVLY、DROM和MP/MC位進行配置。其中,OVLY和DROM上電復位均為0,而MP/MC決定配置DSP為微處理器/微機模式。上電后采樣MP/MC引腳信號,保存在MP/MC位,可以在DSP運行中由軟件配置該位。

AD9835是AD公司生產的一款CMOS工藝完備的DDS芯片,5V供電。它的最高時鐘頻率可達50MHZ。AD9835主要由數控振蕩器(NCO)和相位調制器、正弦查詢表以及一個10位數模轉換器(DAC)組成。其中數控振蕩器和相位調制器部分包含兩個32位的頻率寄存器、一個32位的相位累加器和四個12位的相位寄存器。

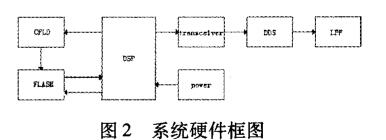

2、系統硬件實現

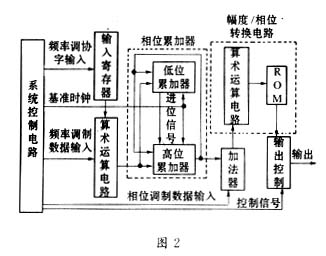

系統硬件框圖如圖2所示:

選用的FLASH存儲器為AM29LV160D。由DSP芯片通過CPLD對FLASH進行邏輯控制。這樣可以使系統的存儲器配置更加靈活。由于外擴了FLASH,DSP要對FLASH進行正常讀寫的邏輯時序控制就由CPLD來實現,由于CPLD可在線編程,使得日后系統的邏輯的修改也非常方便,這比用傳統的組合邏輯電路設計要靈活方便,只需要的是將DSP對FLASH讀寫時序分析清楚。在此采用的是Altera公司的EPM7064S來完成以上功能。

電源芯片采用rI’I公司生產的TPS767D318,該芯片是雙電源輸出,每個電源輸出都有單獨的復位和輸出使能控制。它采用TSSOP封裝,固定兩路電壓輸出,第一路輸出1.8V,第二路輸出電壓為3.3V。該芯片同時還提供)兩路復位信號,該系統中只使用了第二路復位信號,芯片的22引腳輸出低電平復位信號,復位后需為高電平,上拉為3.3V。

數字解調實驗時采用的信號是已調模擬信號,模擬信號不能直接送人DSP中,要先由模數轉換器(AD)轉換為數字信號后,再送入DSP中進行數字解調和基帶處理。模數轉換器選用了AD公司的AD轉換芯片AD7822。AD7822是20腳的8位模數轉換芯片,最大采樣率可以達到2MSPS。AI)7822以并行的方式和DSP相連。數模轉換(DA)模塊的功能就是完成數字信號的模擬化,在進行數字調制實驗時通過DA模塊把DSP輸出的已調數字信號轉換為模擬信號,可以為解調實驗提供一個已調的模擬信號,也可以通過示波器觀測調制信號波形。該模塊選用了AD公司的芯片AD7303。

電子發燒友App

電子發燒友App

評論