0 引言

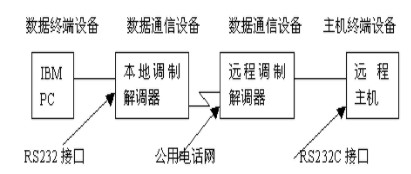

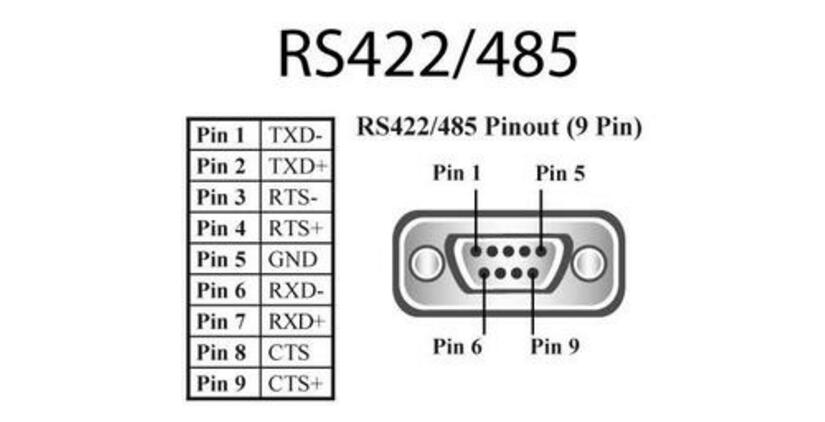

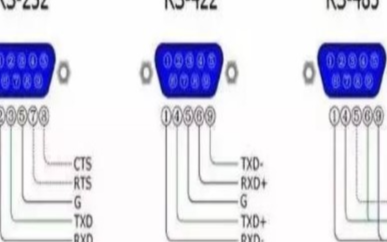

隨著我國(guó)航空技術(shù)的不斷發(fā)展,我國(guó)新研制了眾多不同型號(hào)和不同用途的飛機(jī)。這些飛機(jī)以及這些飛機(jī)上電子設(shè)備之間采用的RS 232和RS 422格式傳輸?shù)臄?shù)據(jù)總線也有了極大的發(fā)展。它們傳輸數(shù)據(jù)的數(shù)據(jù)位、校驗(yàn)位、停止位、波特率及傳輸?shù)?a target="_blank">信息塊形式各不相同,尤其波特率,已經(jīng)從當(dāng)初的幾十Kb/s發(fā)展到現(xiàn)在的上百Kb/s甚至上Mb/s。這就需要研制一種高速RS 232/422信號(hào)模擬器,它能夠模擬我國(guó)現(xiàn)有飛機(jī)及機(jī)上設(shè)備采用RS 232或RS 422格式進(jìn)行相互通信的RS 232/422總線數(shù)據(jù),為機(jī)載測(cè)試工程師在試驗(yàn)室對(duì)機(jī)上采集RS 232或RS 422信號(hào)的設(shè)備進(jìn)行通電和編程驗(yàn)證,以及外場(chǎng)機(jī)上排故時(shí)提供方便可靠而又靈活的RS 232/422信號(hào)模擬器。

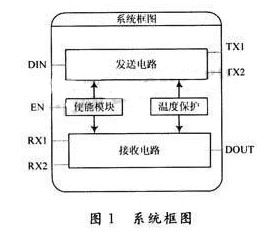

1 系統(tǒng)總體方案設(shè)計(jì)

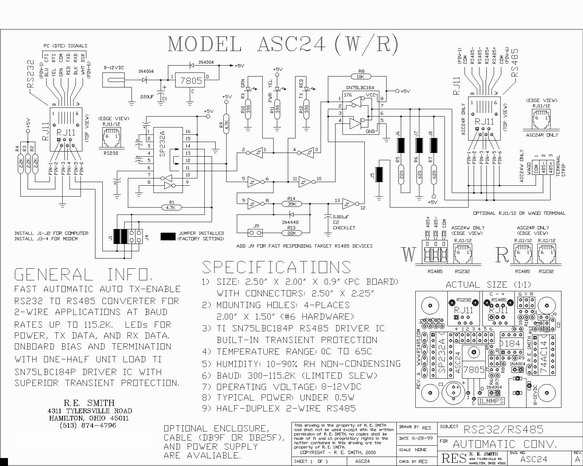

RS 232/422信號(hào)模擬器主要由USB接口、鍵盤(pán)顯示、電源管理、RS 232/422信號(hào)電平轉(zhuǎn)換和FPGA核心控制這幾部分電路模塊組成。USB接口電路主要功能是和上位計(jì)算機(jī)通過(guò)USB接口建立連接,把上位計(jì)算機(jī)發(fā)送數(shù)據(jù)傳送到FPGA核心控制電路,或者把FPGA核心控制電路發(fā)送的數(shù)據(jù)傳送到上位計(jì)算機(jī)。鍵盤(pán)顯示電路主要功能是當(dāng)信號(hào)模擬器脫離PC機(jī)獨(dú)立工作時(shí),通過(guò)鍵盤(pán)輸入命令和數(shù)據(jù),并在LED顯示屏上觀察輸入的命令和數(shù)據(jù)是否正確,并可以在接收時(shí)能察看接收到的數(shù)據(jù),以判斷接收到的數(shù)據(jù)正確與否;此外,它還可以實(shí)時(shí)顯示電源的狀態(tài)和電池的電量等信息。電源管理主要是對(duì)供電源頭進(jìn)行排序和自動(dòng)選擇,同時(shí)監(jiān)控電池的電量信息,并把這些信息傳送給FPGA核心控制電路。

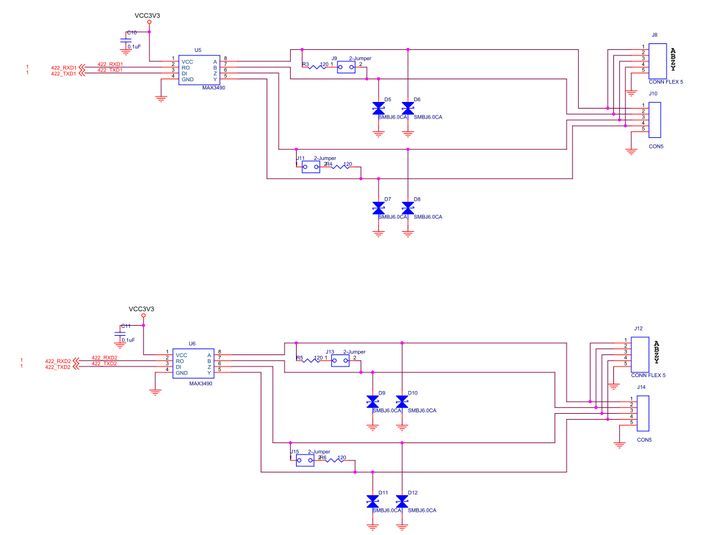

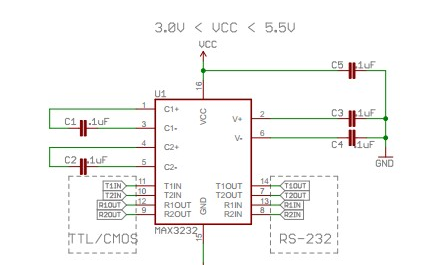

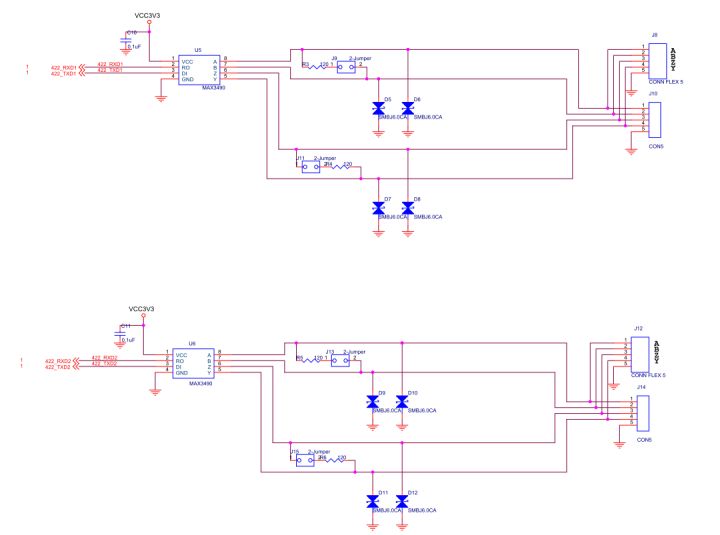

RS 232/422信號(hào)電平轉(zhuǎn)換電路主要功能則是把TTL或CMOS電平轉(zhuǎn)換成符合要求電平傳送出去,或者把接收到的RS232或RS 422標(biāo)準(zhǔn)的信號(hào)電平轉(zhuǎn)換成TTL或COMS電平,同時(shí)在不工作時(shí)使這些電路處于睡眠狀態(tài),以降低功耗。FPGA核心控制電路是本硬件系統(tǒng)的核心,它對(duì)以上部分的電路系統(tǒng)進(jìn)行統(tǒng)一管理,監(jiān)控所有電路的工作狀態(tài),并隨接收來(lái)自這些電路的數(shù)據(jù)信息,根據(jù)這些信息做出不同的處理,如果需要的話,并把部分結(jié)果在LED顯示屏或者上位計(jì)算機(jī)屏幕上顯示出來(lái),供操縱者參考。本信號(hào)仿真器的硬件系統(tǒng)電路原理框圖如圖1所示。

2 主要電路模塊設(shè)計(jì)

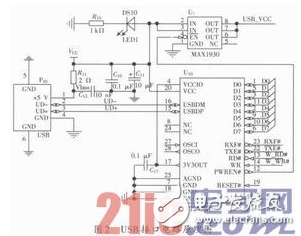

2.1 USB接口電路模塊設(shè)計(jì)

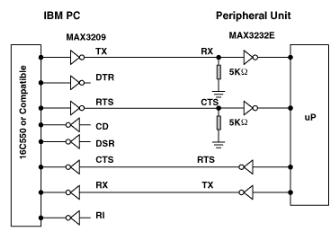

USB(Universal Serial Bus,(計(jì)算機(jī))通用串行總線)是計(jì)算機(jī)和外圍設(shè)備連接的最常用,也是最方便的總線接口,它支持熱插拔和即插即用,應(yīng)用靈活,易于升級(jí),全速率傳輸可達(dá)12 Mb/s,而高速傳輸達(dá)480 Mb/s,并且它同時(shí)可以向外圍設(shè)備提供耗電電流不大于500 mA的

5 V電源。在本信號(hào)仿真器中,USB接口不僅僅具有和信號(hào)仿真器交換數(shù)據(jù)的任務(wù),同時(shí)還向信號(hào)源提供5 V的直流供電的功能。通過(guò)USB接口,上位計(jì)算機(jī)依靠用戶(hù)界面程序?qū)π盘?hào)仿真器的工作狀態(tài)、模擬的信號(hào)格式和信息塊內(nèi)容進(jìn)行沒(méi)置;當(dāng)處于接收工作狀態(tài)時(shí),還可以把接收到的數(shù)據(jù)實(shí)時(shí)顯示在計(jì)算機(jī)屏幕上。在設(shè)計(jì)中,本文采用了FTDI公司的FT245RL芯片作為主要的接口協(xié)議處理芯片,它本身集成了協(xié)議處理的固件程序,并且FTDI公司網(wǎng)站上也提供了此芯片的驅(qū)動(dòng)程序,縮小了開(kāi)發(fā)難度,加快了開(kāi)發(fā)時(shí)間和成本。USB接口電路模塊的電路原理圖如圖2所示。

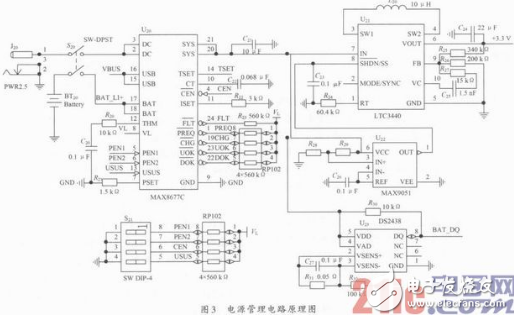

2. 2 電源管理電路模塊設(shè)計(jì)

信號(hào)模擬器既有USB接口供電,也有AC/DC適配器供電,同時(shí)還有著電池供電,這里供電電源的管理顯得異常重要。在電源管理電路的設(shè)計(jì)中,首先要有電源排序和自動(dòng)切換電路,當(dāng)同時(shí)存在這三個(gè)電路供電時(shí),要求能自動(dòng)切斷AC/DC和電池供電,無(wú)縫的轉(zhuǎn)向USB供電。當(dāng)USB接口不供電時(shí),轉(zhuǎn)向了AC/DC適配器供電,最后才是電池供電。整個(gè)過(guò)程的供電順序是USB供電→AC/DC供電→電池;其次是要求能夠?qū)╇婋娐返臓顟B(tài)和信息進(jìn)行監(jiān)控。電源管理電路模塊要求能提供供電是來(lái)自USB接口、AC/DC適配器或是電池的信息,當(dāng)是電池供電時(shí),還需要提供電池的電量信息,即電池還剩余多少電量;最后,還要有鋰離子充電電池的放電和充電的管理。為保護(hù)鋰離子電池因過(guò)度放電而無(wú)法再次使用,當(dāng)電池放電到終止電壓時(shí),自動(dòng)切斷供電電路,使電池供電電路處于斷開(kāi)狀態(tài)。當(dāng)插入AC/DC適配器和USB接口供電時(shí),電源管理電路模塊可以對(duì)電池進(jìn)行充電,同時(shí),電池的放電是一個(gè)電源逐漸衰減的過(guò)程,還需要對(duì)電源進(jìn)行穩(wěn)壓。鑒于這些原因,電源管理電路模塊的設(shè)計(jì)是本文的重難點(diǎn)之一。本系統(tǒng)中電源管理電路模塊原理圖如圖3所示。

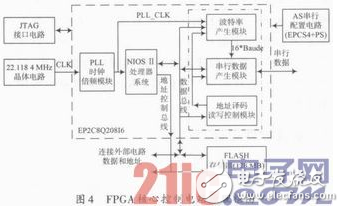

2. 3 FPGA核心控制電路模塊設(shè)計(jì)

FPGA核心控制電路監(jiān)控以上各電路模塊的工作狀態(tài),隨時(shí)準(zhǔn)備接收來(lái)自它們的數(shù)據(jù)和命令,并進(jìn)行相應(yīng)的控制。它包括了控制部分和串行數(shù)據(jù)生成部分,控制部分是在FPGA芯片內(nèi)部嵌入Alter公司提供的NIOSⅡ的處理器IP軟核,利用QuartusⅡ軟件內(nèi)部的SOPC工具生成FPGA內(nèi)部的控制電路。串行數(shù)據(jù)生成部分利用VHDL硬件編程語(yǔ)言編制了波特率發(fā)生器和并串轉(zhuǎn)換模塊生成RS 232/422串行信號(hào)數(shù)據(jù)。所有的控制電路都是通過(guò)軟件定制在一片F(xiàn)PGA芯片內(nèi),外圍電路比較簡(jiǎn)單,除了正常的程序加載電路和程序存儲(chǔ)芯片,僅需要一片時(shí)鐘芯片即可。FPGA核心控制電路原理圖如圖4所示。

3 系統(tǒng)軟件設(shè)計(jì)

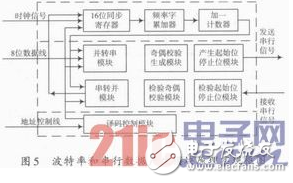

3.1 波特率和串行數(shù)據(jù)產(chǎn)生模塊設(shè)計(jì)

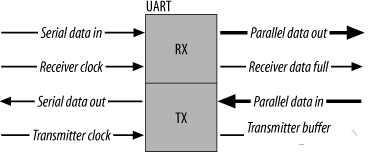

串行數(shù)據(jù)產(chǎn)生模塊負(fù)責(zé)生成符合格式設(shè)置要求的串行數(shù)據(jù),如起始位,數(shù)據(jù)位,效驗(yàn)位,停止位等。它主要是把控制器發(fā)送的并行數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù),并根據(jù)控制器發(fā)送的效驗(yàn)位,停止位等設(shè)置命令來(lái)設(shè)置數(shù)據(jù)的格式,以來(lái)自波特率產(chǎn)生模塊的16倍的波特率作為全局時(shí)鐘,生成要模擬的RS 232/422信號(hào)數(shù)據(jù)。

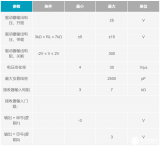

波特率產(chǎn)生模塊根據(jù)控制器發(fā)送的命令數(shù)據(jù)來(lái)產(chǎn)生符合要求的波特率。在本系統(tǒng)中,要求產(chǎn)生24種標(biāo)準(zhǔn)和非標(biāo)準(zhǔn)的波特率,其中標(biāo)準(zhǔn)的波特率16種,非標(biāo)準(zhǔn)波特率8種,最高的波特率達(dá)到1 Mb/s,這樣利用常規(guī)的分頻器不能滿(mǎn)足要求。

依據(jù)DDS(直接數(shù)字頻率合成)的原理,結(jié)合積分分頻電路,設(shè)計(jì)了頻率字累加器,通過(guò)從NIOSⅡ控制器輸入的頻率字來(lái)控制累加器的累加步長(zhǎng),將累加器輸出的最高位作為輸出的時(shí)鐘信號(hào)的方法實(shí)現(xiàn)所需要的波特率時(shí)鐘,此時(shí)輸出的時(shí)鐘即可作為串行數(shù)據(jù)產(chǎn)生模塊的全局時(shí)鐘,也就是16倍的波特率。同時(shí)為了提高時(shí)鐘的精確度,降低誤碼率,在系統(tǒng)時(shí)鐘(這里采用的是22 11 8 4 MHz)進(jìn)入分頻器以前,利用PLL倍頻電路提高時(shí)鐘的頻率。

波特率和串行數(shù)據(jù)產(chǎn)生模塊在FPGA內(nèi)部的原理實(shí)現(xiàn)框圖如5圖所示。它的實(shí)現(xiàn)是采用VHDL硬件描述語(yǔ)言實(shí)現(xiàn)的,框圖中每個(gè)小的模塊代表VHDL語(yǔ)言編制的模塊程序。

3.2 NIOSⅡ控制器系統(tǒng)定制和內(nèi)部程序設(shè)計(jì)

傳統(tǒng)的MCU,DSP或ARM等硬處理器或控制器,它們的功能和片內(nèi)外設(shè)都是固化好的,用戶(hù)只能使用,而不能做任何改動(dòng)。而NIOSⅡ處理器是FPGA芯片生成廠商Altera公司無(wú)償提供的軟IP核,可以通過(guò)QuanusⅡ軟件對(duì)它進(jìn)行設(shè)置,隨時(shí)可以添加在片的ROM或RAM,并去掉不必要的外設(shè),使得整個(gè)系統(tǒng)的搭建靈活,方便,簡(jiǎn)潔。并且,在硬件系統(tǒng)的設(shè)計(jì)上,一片F(xiàn)PGA芯片內(nèi)就可以完成整個(gè)的數(shù)字控制系統(tǒng),使得硬件系統(tǒng)的設(shè)計(jì)非常的簡(jiǎn)單可靠,性能也非常的穩(wěn)定。

在本系統(tǒng)的設(shè)計(jì)中,NIOSⅡ處理器和傳統(tǒng)的MCU,DSP或ARM等硬處理器或控制器一樣,也可以用C語(yǔ)言編程實(shí)現(xiàn)需要的控制功能,也可以嵌入各種嵌入式操作系統(tǒng),并進(jìn)行調(diào)試等。編程的開(kāi)發(fā)環(huán)境是專(zhuān)用的NIOS2-IDE集成開(kāi)發(fā)環(huán)境。

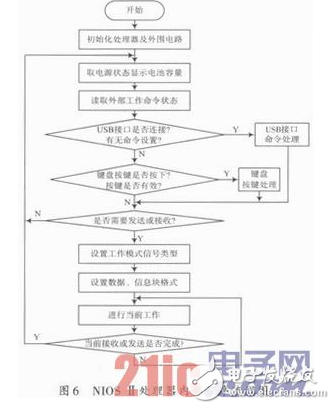

NIOSⅡ處理器內(nèi)部程序主要完成USB與PC機(jī)之間的通信協(xié)議,依據(jù)PC機(jī)發(fā)送的設(shè)置命令來(lái)完成具體RS 232/422信號(hào)的實(shí)現(xiàn),并完成數(shù)據(jù)格式的設(shè)置,數(shù)據(jù)塊的設(shè)置,數(shù)據(jù)下行發(fā)送和上行傳輸及信號(hào)源工作狀態(tài)的顯示。其內(nèi)部程序流程圖如圖6所示。

3. 3 用戶(hù)界面程序設(shè)計(jì)

信號(hào)仿真器在PC機(jī)端的軟件設(shè)計(jì)包括設(shè)備驅(qū)動(dòng)程序和用戶(hù)程序兩部分,F(xiàn)TDI公司為基于FT245RL的USB接口設(shè)備提供了VCP、D2XX(動(dòng)態(tài)鏈接庫(kù))兩種驅(qū)動(dòng)程序,這樣就不再需要自己設(shè)計(jì)設(shè)備驅(qū)動(dòng)程序,而只需要選擇不同的驅(qū)動(dòng)程序,可以把主要精力投入在用戶(hù)軟件設(shè)計(jì)上面。

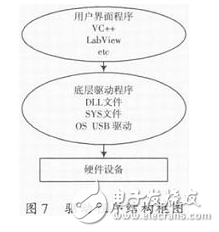

底層驅(qū)動(dòng)程序主要完成上位計(jì)算機(jī)和硬件設(shè)備的連接功能,并為用戶(hù)界面程序建立和信號(hào)源仿真器相互通信的通信協(xié)議和通道,其結(jié)構(gòu)框圖如圖7所示。

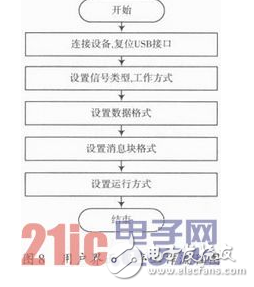

用戶(hù)界面程序主要完成用戶(hù)對(duì)模擬信號(hào)源進(jìn)行的工作模式選擇,信號(hào)種類(lèi)選擇,數(shù)據(jù)格式設(shè)置和消息塊格式設(shè)置的輸入功能,同時(shí)可以預(yù)覽信號(hào)源發(fā)送的信號(hào)數(shù)據(jù),讀取信號(hào)源接收到的數(shù)據(jù),并可以對(duì)存貯數(shù)據(jù)的FLASH芯片進(jìn)行擦除。依據(jù)其要完成的功能,其流程圖如圖8所示。

4 結(jié)語(yǔ)

本文研制的高速RS 232/422信號(hào)仿真器,即可以由計(jì)算機(jī)通過(guò)USB接口控制使用,也可以依靠自身攜帶的電池、鍵盤(pán)和LED顯示屏獨(dú)立工作。它在設(shè)計(jì)中采用了FPGA技術(shù),免除了程序跑飛的可能,提供了高速的,多種標(biāo)準(zhǔn)和非標(biāo)準(zhǔn)的波特率,靈活的數(shù)據(jù)格式和信息塊格式設(shè)置,是機(jī)載測(cè)試采集器采集RS 232/422信號(hào)進(jìn)行實(shí)驗(yàn)室通電或外場(chǎng)排除RS 232/422總線數(shù)據(jù)故障時(shí)比較理想的選擇。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論