Giga ADC是TI推出的采樣率大于1GHz的數據轉換產品系列,主要應用于微波通信、衛星通信以及儀器儀表。本文介紹了Giga ADC的主要架構以及ADC輸出雜散的成因分析,以及優化性能的主要措施。

1、Giga ADC架構及TI的Giga ADC

1.1 Giga ADC架構演進

Giga ADC目前已經廣泛的應用于數據采集、儀器儀表、雷達和衛星通信系統;隨著采樣速率和精度的進一步提高,越來越多的無線通信廠商開始考慮使用Giga ADC實現真正的軟件無線電。軟件無線電不僅可以簡化接收通道設計,同時可以方便不同平臺的移植和升級,從而降低開發成本和周期。

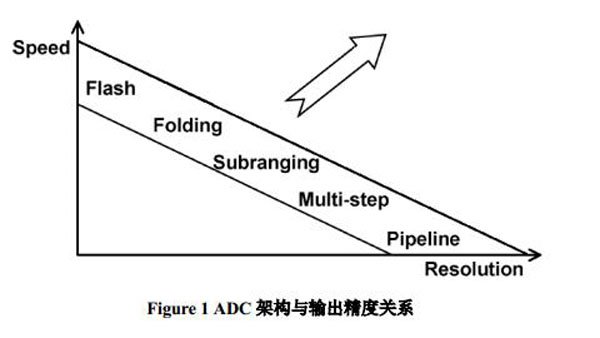

Figure 1列出了在使用各種采樣架構下,采樣精度和采樣速率之間關系。隨著技術和工藝的發展,各種架構可以支持的采速率在不斷的提升,但就目前的水平來看,要實現1Gpbs以上的采樣率,必須采用Flash或者折疊(Folding)架構。

這主要是因為在其它架構中,都采用了反饋環路;這些反饋環路的傳輸延時限制了ADC速率的進一步提升。例如在pipeline中,每一級都有一個DAC,用于把本級的數據輸出轉換成模擬信號,反饋給本級的模擬輸入,取差以后放大輸出給下一級。類似的限制也存在于Subranging或者multi-step架構中,都需要一個反饋環路輔助判決。

另一方面,雖然目前業界最快的ADC架構是Flash架構,但一個N bit的flash ADC需要2N-1個比較器,當N=8時,比較器的數量將會非常龐大;而且隨著轉換精度的增加,后端的譯碼邏輯也會變得異常復雜;這些都會對芯片的體積和功耗造成很大的影響。

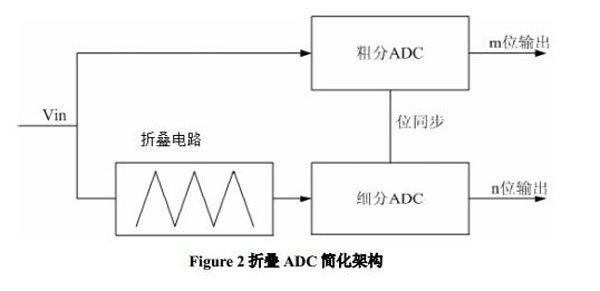

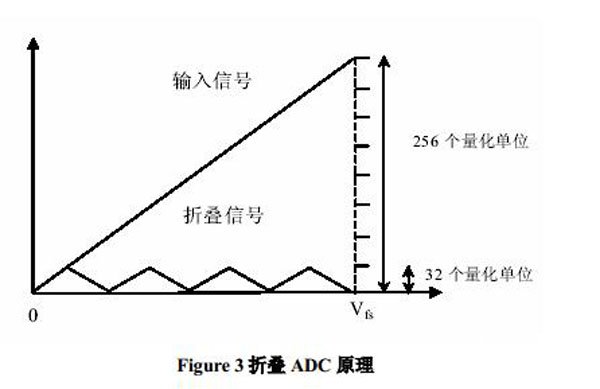

所以在TI的Giga ADC中,采用了折中的折疊(folding)架構。事實上,折疊是和flash類似的架構,不同的是,在折疊架構中,輸入信號分別通過了粗分ADC和折疊電路+細分ADC;折疊電路的理想傳輸特性為三角狀循環的折疊信號。以一個8bit ADC為例,粗分ADC輸出3bit,細分ADC輸出5bit。如Figure 2和Figure 3所示,折疊電路共折疊了8次,將滿量程的輸入范圍等分為8段,分別對應3位粗分ADC轉換產生的高位bit(MSB);同時對上述折疊電路輸出信號進行5位細化轉換得到低位bit(LSB);最后高、低位數字碼合起來組成8位的數字輸出。

對于一個8bit ADC,采用折疊電路架構所需要的比較器個數為

![]()

,

![]()

(m = 3,n = 5);如果采用flash架構,則需要比較器的個數為。顯而易見,采用折疊架構大大降低了比較器的個數。

1.2 TI Giga ADC產品介紹

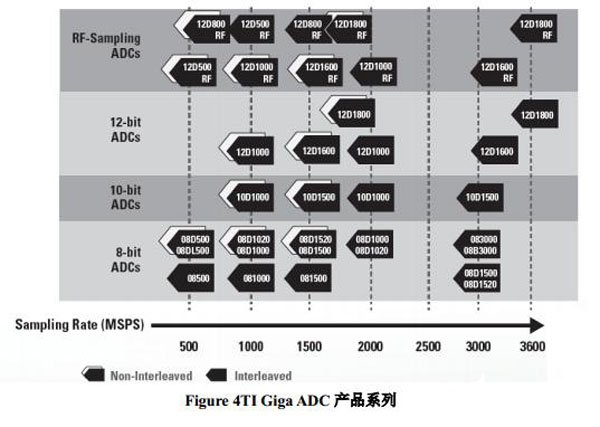

TI在過去的十年當中,利用創新的ADC架構和工藝技術,不斷的刷新業界Giga ADC的采樣速率和轉換精度,最新的產品已經可以達到5Gbps @ 7.6bit(LM97600)和4Gpbs @ 12bit(ADC12D2000RF)。Figure 4是目前TI全系列的Giga ADC產品:

2、TI Giga ADC架構介紹

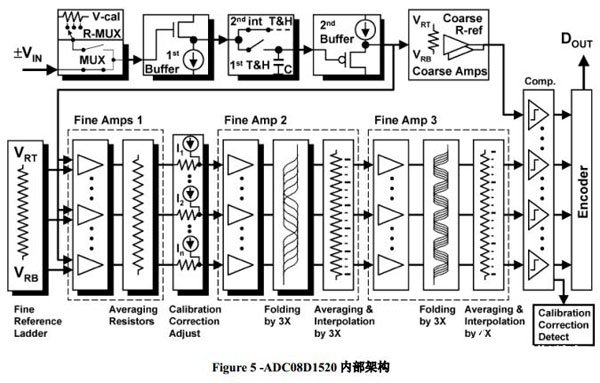

本章節中將詳細討論Giga ADC的各個功能模塊。在實際應用中,設計者一般都會采用Folding + interpolation + calibration的架構,用于進一步簡化設計,降低功耗和提高精度。

上圖是一個典型的folding-interpolation架構的Giga ADC框圖。在這類ADC中,為了解決模擬輸入端的匹配誤差和輸入偏置誤差,集成了一個校準信號源,在不需要外部輸入的情況下,實現芯片的前臺校準,使芯片達到最大性能。除此之外,還包括輸入的buffer,采保電路,folding interpolation電路以及比較器、encoder和LVDS輸出電路。

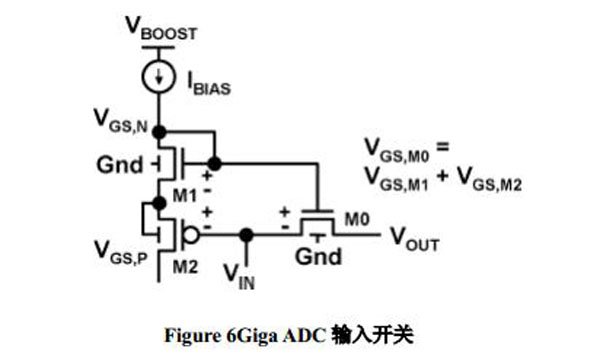

2.1 Input mux

在Figure 5中可以看到,為了盡可能的把輸入鏈路上所有器件包含到校準環路中,校準信號的輸入開關加在了輸入電路的最F前端。這對開關電路的線性和帶寬提出了很高的要求。在TI的Giga ADC電路中,采用了constant Vgst NMOS pass-gate電路,這種電路不僅寬頻帶內導通電阻穩定不變,失真小,而且功耗低。

電路校準只在器件上電或者器件工作溫度發生明顯變化的時候才會發起,輸入校準開關也只在這個時候才會導通。

2.2 Interleaved TH

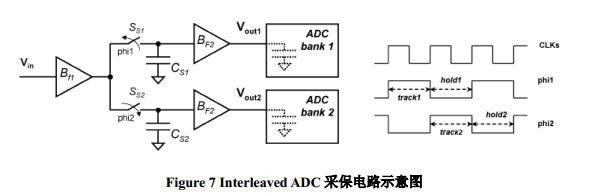

在高速ADC設計中,為了達到更高的采樣速率,采用了interleaved的架構,即一個模擬輸入,輸入到兩個相同的ADC中,但這兩個ADC的采樣速率相同,相位相反;最后芯片的數字部分把兩路ADC的輸出信號重新整合,達到了相對于每路ADC兩倍的采樣速率。將采樣保持電路放在第一級buffer之后,主要是因為這一級buffer降低了輸入信號的負載和kickback噪聲,方便寬帶匹配;同時降低了采保電路的工作頻率,使得采保電路和第二級buffer的設計和功耗大大簡化。

需要注意的是,在interleaved架構中,兩路采樣保持電路和buffer的偏置和增益誤差,以及兩路采樣時鐘之間的相位誤差,都會給整個ADC系統SNR帶來很大的影響。在設計中,兩路電路采用了完全鏡像的設計,同時兩路電路都在校準環路里,有效的降低了這些誤差帶來的性能惡化。

2.3 Preamplifier

預放大電路處于采保電路之后,比較器之前,包括第二級輸入buffer,折疊內插電路等。預放大電路的主要功能包括輸入信號的放大,以降低電路偏置誤差對性能的影響;輸入信號的折疊處理,將輸入信號通過折疊電路分成若干部分,從而降低比較器的個數;通過內插電路增加信號過零點,減少折疊電路模塊。

2.3.1 第二級輸入buffer

第二級輸入buffer的主要作用就是要把采保電路輸出的偽差分信號通過差分放大器轉換成真正的差分信號,以達到更好的電源抑制比和方便后級處理。第二級buffer輸出的差分信號分成兩路,一路輸出給粗分轉換電路,用于判決輸入信號處于那一個折疊區;一路輸出給細分轉換電路,輸出具體的轉換數據。

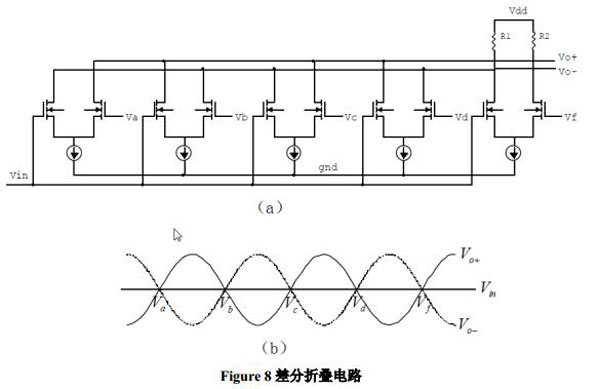

2.3.2 折疊電路

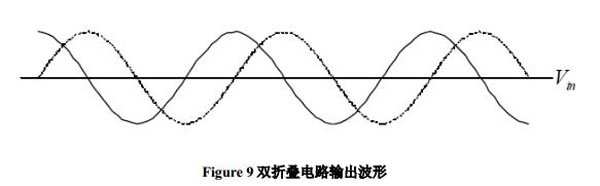

Figure 8為一種實際折疊電路及其直流傳輸特性。Figure 8(a)中,輸入信號Vin和5個量化參考電平Va、Vb、Vc、Vd和Vf;5個源極耦合對的漏極交替連接,通過負載電阻R1和R2的IV變換,形成一對5倍折疊(折疊率F = 5)的差分折疊信號Vo+與Vo-,如Figure 8(b)所示。Figure 8(b)中,直流傳輸特性上差分輸出為零的點稱為過零點。可見,除了過零點附近,實際折疊電路的傳輸特性存在著一定的非線性區域。為解決非線性區域上輸入信號的量化問題,可采用兩個具有一定相位差的折疊信號,如Figure 9所示。它們之間的相位差保證了各自的非線性區域相互錯開。

當一個折疊輸出信號不是在線性區域范圍內時,另一個折疊輸出信號恰好在線性區域內,反之亦然。這種方法可以推廣到相位差更小的一組折疊信號的情況,以減小非線性區域的影響。直至,相鄰折疊信號的過零點只相距一個量化單位(LSB)時,每個與折疊電路連接的比較器只需檢出過零點。此時,折疊結構ADC不再要求折疊信號的線性區域范圍,只要求過零點的精度。

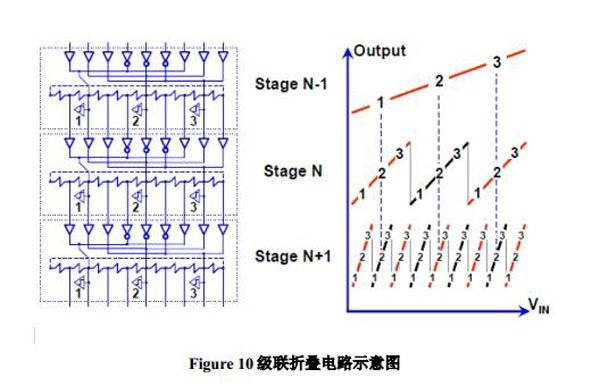

在折疊電路設計中,一級折疊電路折疊率不宜過高,這主要是因為,如果一級折疊率過高,那么這么多輸出通過長的走線連接到一起輸出給下一級比較器,寄生電容對于后級的影響變得不可忽略。在TI的Giga ADC中,一般采用多級折疊電路級連的方式,例如,如果要實現一個折疊率為9的電路,采用了兩級折疊級連,每級的折疊率是3,如Figure 10所示。

2.3.3 內插電路

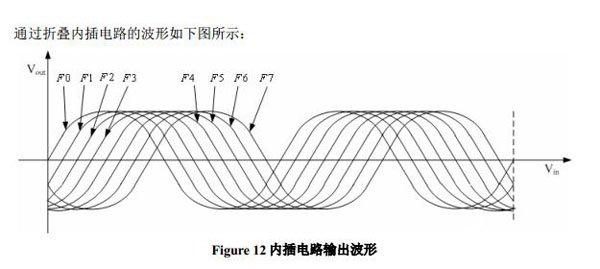

直接利用折疊電路來產生所有2N個過零點,ADC的功耗與輸入電容都很大。通常的解決辦法是采用折疊-內插結構,如Figure 11所示。每兩個折疊電路的輸出之間連接一個插值電阻串,利用插值電阻的分壓作用得到兩個折疊電壓信號之間的插值電壓。每個插值節點作為輸出,插值的數目稱為內插率I;Figure 11是當I=4的內插結果,兩側為原始的由折疊電路產生的折疊信號,夾在其間的3個信號是被節省的、由內插電路產生的折疊信號。這樣,通過4倍的內插,每4個折疊信號可以節省3個折疊電路。

通過折疊內插電路的波形如下圖所示:

2.3.4 平均電路

前面提到,影響電路精度的主要誤差是差分信號的偏置誤差。降低差分電路的偏置誤差可以增加晶體管的面積。但由于在折疊電路中,偏置誤差不僅僅來自于差分電路,折疊電路中其它飽和支路的輸出電流也增加了整個電路的偏置誤差,簡單的增加電路晶體管面積并不能有效的降低誤差。由于各個放大電路的偏置誤差是不相關的,這里采用了迭代的技術,使某一輸出節點的偏置誤差不僅僅取決于本身放大電路,還和相鄰其它并行放大電路輸出有關,偏置誤差通過放大電路輸出的迭代而隨機化,降低了整個電路的偏置誤差。

2.4 校準電路

前面提到的各種設計電路有效的提高了ADC的線性性能和帶寬,但在TI Giga ADC,仍然集成了校準電路,用以進一步優化ADC的性能。這部分校準電路包括27個高精度校準電壓,采用輪詢的方式依次輸入到輸入級的開關,并根據校準信號的輸出結果通過DAC調整預放大電路的偏置電流,達到校準修正的結果。

通過Figure 5可以看到,輸入級的MUX開關,采保電路,輸入buffer的偏置誤差以及折疊電路的偏置誤差等包括在校準環路里,通過校準不僅僅提高了放大電路的線性,而且提高了系統在interleave模式下兩路ADC之間的一致性,改善了系統的雜散性能。

3、Giga ADC雜散的分析

ADC應用中,輸出的雜散信號決定了ADC的動態范圍。在傳統的流水線ADC中,起決定作用的主要是諧波雜散,即輸入信號的二次、三次或更高次諧波混疊進入第一個Nyquist區。除此以外,Giga ADC的interleave架構帶來了其它雜散。如前文說提到的,為了達到更高的采樣速率,每路ADC實際包括兩個子ADC,這兩個子ADC工作在interleave模式下。在這種情況下,兩路子ADC之間的失配將會產生新的雜散信號。總體來說,Giga ADC的雜散主要分為三類雜散信號:1)interleave雜散;2)固定頻點雜散;3)和輸入信號相關的雜散。

3.1 Interleave相關的雜散

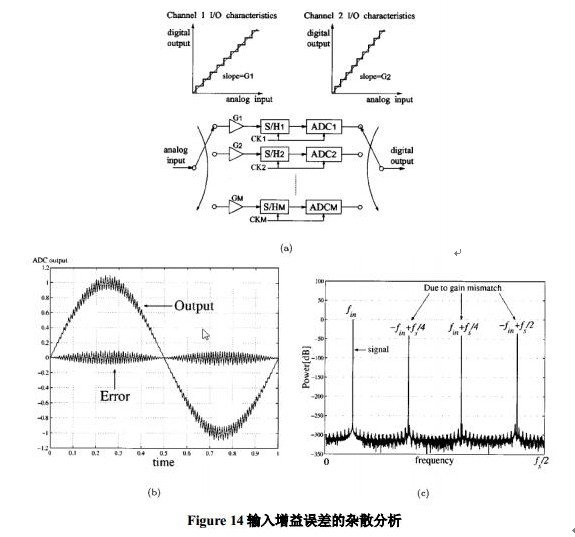

Interleave模式,如Figure 7所示,就是相同的輸入信號,輸入到兩個(或N個)采樣率相同,但采樣時鐘相位相反(或相差2πN)的ADC中,從而達到采樣率增倍的目的。但由于兩路ADC不可能完全一致,存在一些失配,從而導致了一些輸出雜散的生成。這些失配包括偏置誤差、增益誤差以及采樣時鐘的相位誤差。

這里假定:

N:一路ADC中包含的子ADC個數

Fin:輸入有用信號

Fnoise:輸出的雜散信號

Fs:ADC采樣時鐘

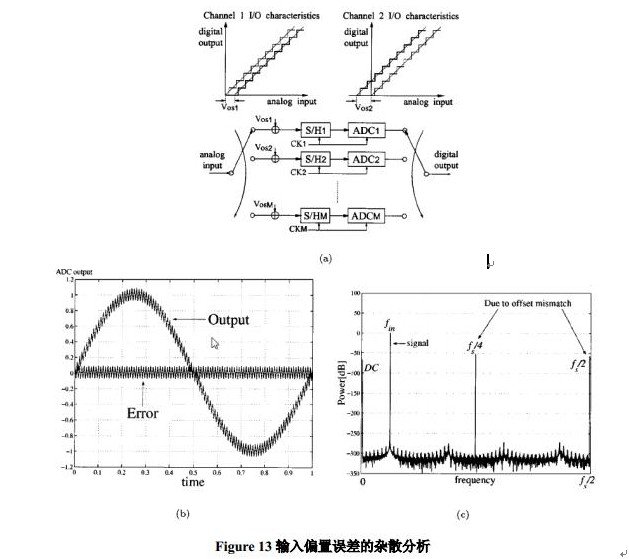

3.1.1 輸入偏置誤差

假定ADC其它參數都是理想的,只考慮輸入偏置誤差。通過數學分析可以得到,輸入偏置誤差帶來的雜散主要分布在

從Figure 13可以看出,輸入偏置誤差帶來的雜散和輸入信號的幅度和頻率沒有關系,從頻域上看,均勻的分布在第一Nyquist區。由輸入偏置帶來的雜散固定的分布在公式一給出的各個頻點。

3.1.2 輸入增益誤差

假定輸入電路除增益誤差以外,其它參數都是理想的,可以看出當輸入信號幅度增大時,增益誤差也隨之變大。輸出的誤差信號類似于輸入信號的一個調幅輸出,可以得到,增益誤差導致的雜散信號出現位置如下:

![]()

從分析可以看出,由于增益誤差導致的輸出雜散幅度和輸入信號的頻率無關,但和輸入信號的幅度有關,輸入信號幅度變大時,雜散幅度增加;反之亦然。

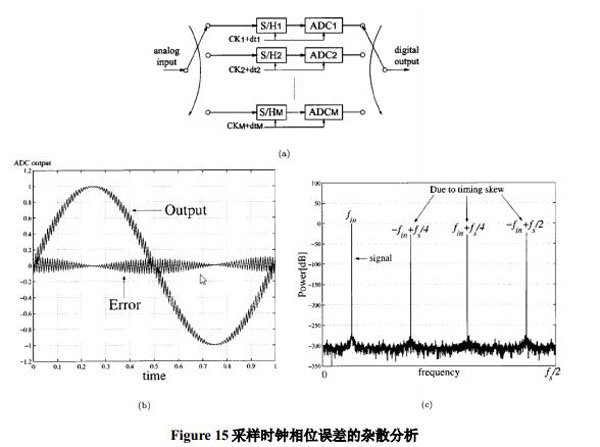

3.1.3 采樣時鐘的相位誤差

如果兩個或多個采樣時鐘之間存在相位誤差(skew),同樣會帶來雜散。由于相位誤差帶來的誤差最大出現在輸入信號壓擺率最大的地方,即過零點,即這類雜散類似于輸入信號的調頻輸出。雜散信號出現的位置在:

采樣時鐘的相位誤差和輸入增益誤差帶來的雜散位置相同,但相位誤差輸出的雜散和輸入頻率有關,當輸入頻率越高,誤差越大;而偏置誤差和增益誤差帶來的雜散和輸入頻率無關。

3.2 固定頻點雜散

相對于interleave雜散,固定頻點雜散和輸入信號的頻點無關,主要取決與系統時鐘,ADC及子ADC的采樣時鐘,數據輸出的隨路時鐘以及系統中其他時鐘源的耦合干擾。固定頻點雜散因為位置固定,應用中很容易預判這些雜散,從而在系統設計中規避這些雜散存在的頻點。

3.2.1 采樣時鐘雜散

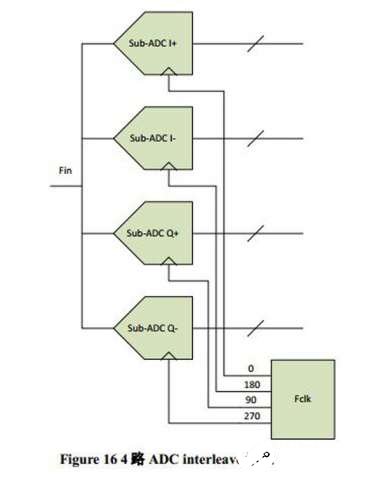

如Figure 16所示,當四個ADC工作在interleave模式下,四個ADC的采樣率都是Fclk,但相位相差90度,這樣整個ADC通道的實際采樣率為4Fclk;輸出的頻譜中,在Fclk頻點處有一個固定的采樣時鐘雜散。這個主要是時鐘的泄露,采樣時鐘從芯片內部或板上耦合到數據的輸出。

3.2.2 數據輸出的隨路時鐘

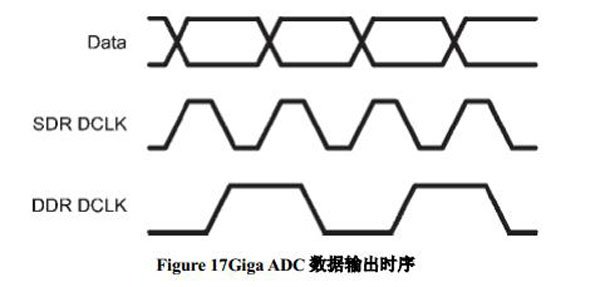

在Giga ADC中,數據的輸出是并行LVDS總線;同時這些總線可以12 Demux或者Non-demux;在Non-demux,數據速率和采樣速率是一致的;在Demux模式下,數據速率降低一倍,但數據總線增加一倍。同時,Giga ADC數據輸出的隨路時鐘可以是DDR或SDR,如下圖所示。在Demux和DDR同時使能的情況下,隨路時鐘DCLK只是采樣時鐘的14,這個時鐘雜散可能出現在Fs4的地方。

3.3 和輸入相關的雜散

前面提到,和輸入相關的雜散主要是輸入信號的奇偶次諧波混疊進入ADC的第一Nyquist區。這類雜散主要通過外部的抗混疊濾波器加以濾除以及信號輸入端的匹配,差分兩端的平衡來優化。這類雜散在傳統的ADC中已經討論很多,這里就不再贅述。

3.4 雜散信號的優化

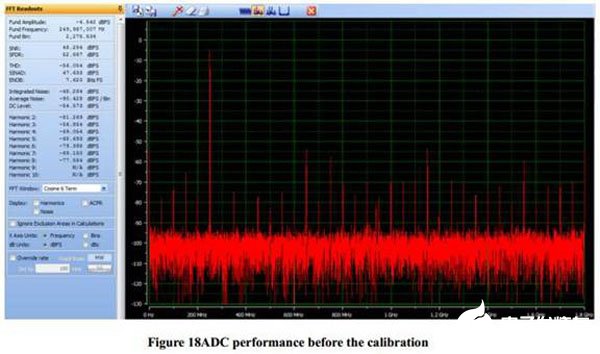

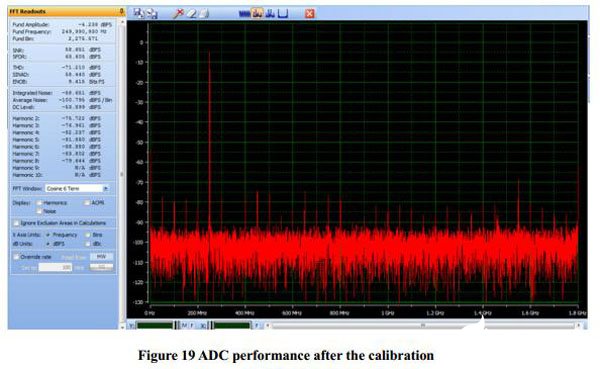

為了達到最佳的輸出雜散性能,在Giga ADC,主要采用了校準環路,來優化輸入電路的偏置誤差、增益誤差。如下圖所示,在校準前后,ADC的性能可以優化10dBc以上。

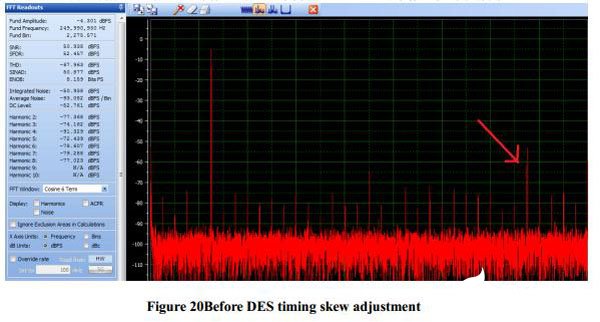

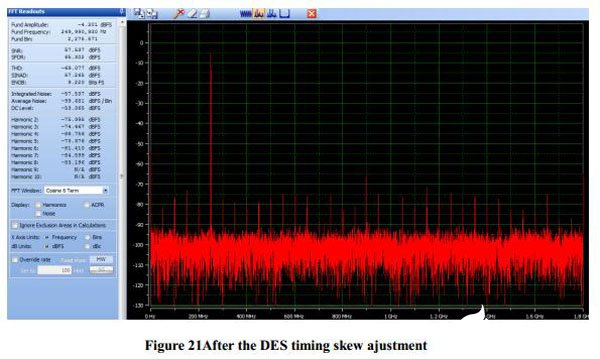

同時,當Giga ADC工作在DES mode,兩路采樣時鐘間的skew對于Fs2-fin的雜散非常重要;芯片提供了兩路采樣時鐘的skew調整功能,可以通過寄存器的配置來降低Fs2–fin的雜散,如下圖所示。

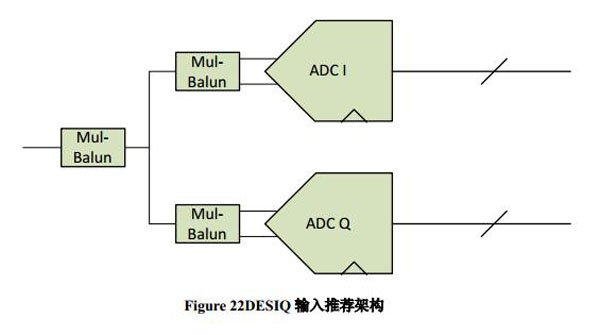

除此之外,ADC的外部輸入電路設計也需要盡量優化,確保兩路差分電路的平衡一致,阻抗的匹配。Giga ADC提供了DESI,DESQ,DESIQ,DESCLKIQ等幾種DES模式下輸入結構;綜合輸入平坦度,插入損耗和最終的ADC性能測試結果,DESIQ模式的性能最佳,并且推薦采用多層Balun和以下的輸入電路。

4、結論

本文主要介紹了TI Giga ADC采用的架構,通過這一先進的架構,TI實現了業界最高采樣率的12bit10bit ADC,并被廣泛使用到了衛星、雷達、微波等通信領域。同時本文也分析介紹了Giga ADC中的輸出雜散的形成原因,以及相應的優化措施。

責任編輯:gt

電子發燒友App

電子發燒友App

評論