給大家分享的是采樣保持電路。

主要是關于:采樣保持名詞解釋、采樣保持電路工作原理、采樣保持電路功能、采樣保持電路作用以及采樣保持電路設計。

一、采樣保持名詞解釋

采樣保持電路從模擬輸入信號中提取樣本并將它們保持特定時間段,然后輸出輸入信號的采樣部分。

采樣保持電路僅適用于對幾微秒的輸入信號進行采樣。

采樣保持電路由開關器件、電容和運算放大器組成。電容是采樣和保持電路的核心,因為它是保持采樣輸入信號并根據命令輸入將其提供到輸出端的電路。

采樣電路主要用于模數轉換器,以消除輸入信號中的某些變化,這些變化可能會破壞轉換過程。

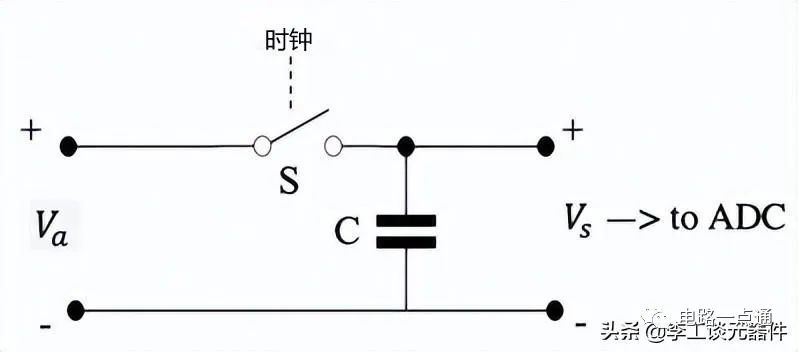

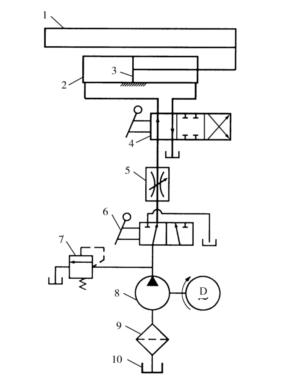

最簡單的采樣保持電路原理圖如下圖所示。

最簡單的采樣保持電路

Vs:輸出信號

C:電

S:作為開關工作的 MOS 晶體管

Va:輸入信號

二、采樣保持電路

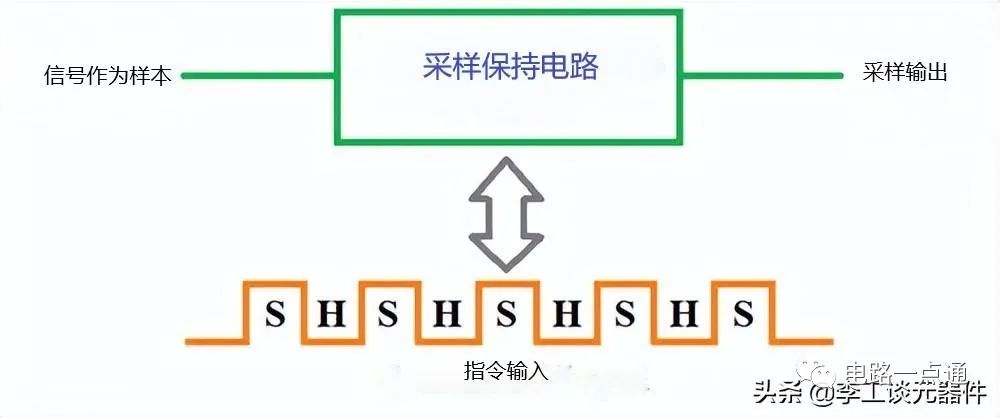

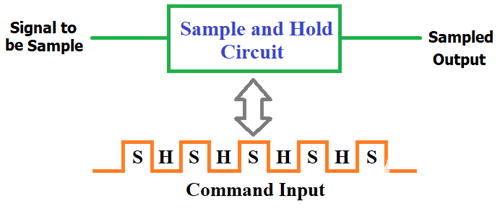

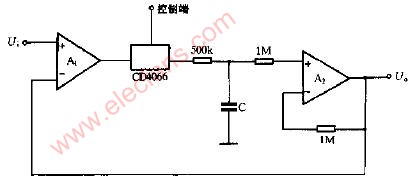

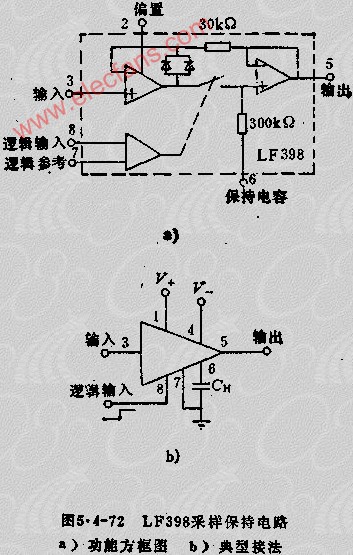

典型的采樣保持電路框圖如下:

采樣保持電路框圖

一般施加的輸入電壓信號是連續變化的模擬信號。提供命令輸入來觸發輸入信號的采樣和保持。命令輸入只不過是一個開/關信號,用于開始/停止輸入信號的采樣,一般是PWM。采樣和保持過程取決于命令輸入。

當開關閉合時,信號被采樣,當它打開時,電路保持輸出信號。開關的開/關狀態由指令輸入控制。

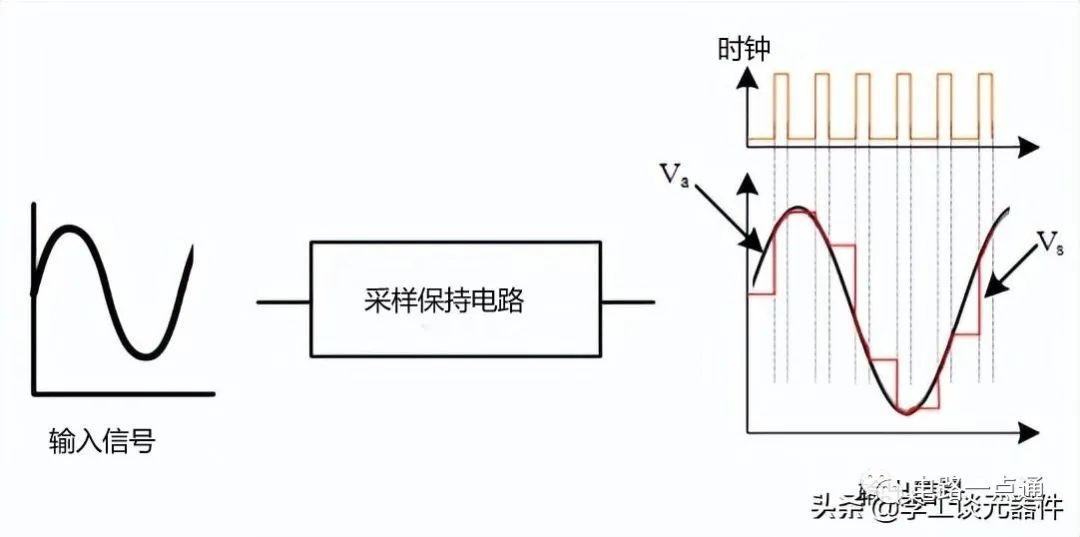

時鐘脈沖激活開關 (S)。根據時鐘脈沖,輸入信號被采樣或保持為最近采樣的值。當時鐘脈沖為高電平時對輸入信號進行采樣,并在時鐘脈沖為低電平時保留這些值。該電路可以在兩種模式下工作,這取決于采樣和保持時鐘信號的邏輯電平。時鐘切換的輸入脈沖和電路的輸出如下圖所示。

開關時鐘脈沖和電路輸出

三、采樣保持電路功能及工作原理

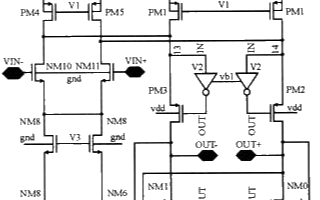

采樣保持電路的工作原理可以通過其組件的工作原理來簡單理解。構建采樣保持電路的主要部件包括一個 N 溝道增強型 MOSFET、一個電容和一個高精度運算放大器。

作為開關元件,使用了 N 溝道增強型 MOSFET。輸入電壓通過其漏極端子給出,控制電壓也通過其柵極端子給出。

當施加控制電壓的+ve 脈沖時,MOSFET將處于激活狀態。它充當閉合開關。相反,當控制電壓為零時,MOSFET 將處于停用狀態并作為打開的開關工作。

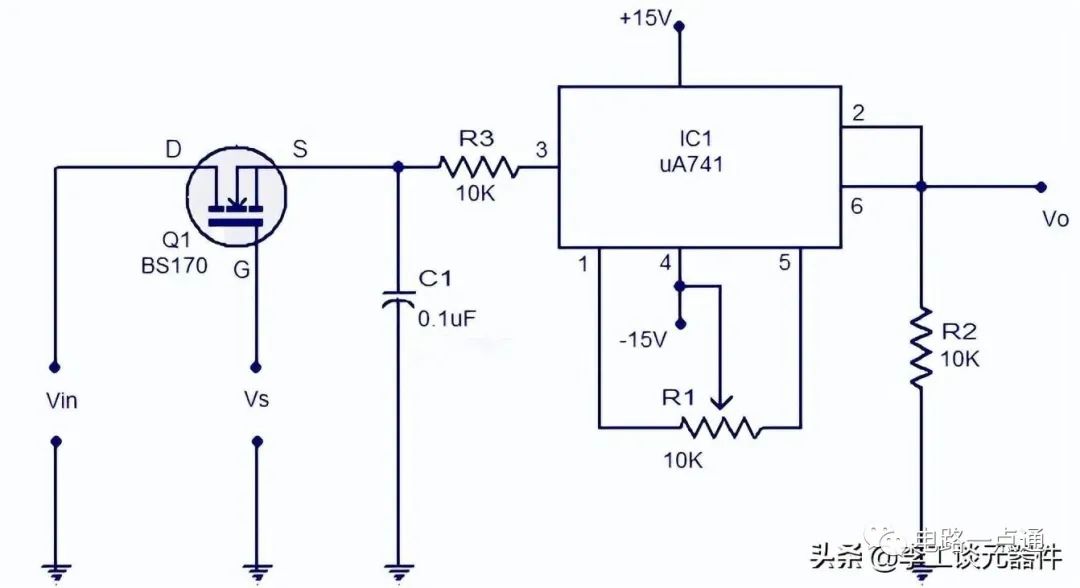

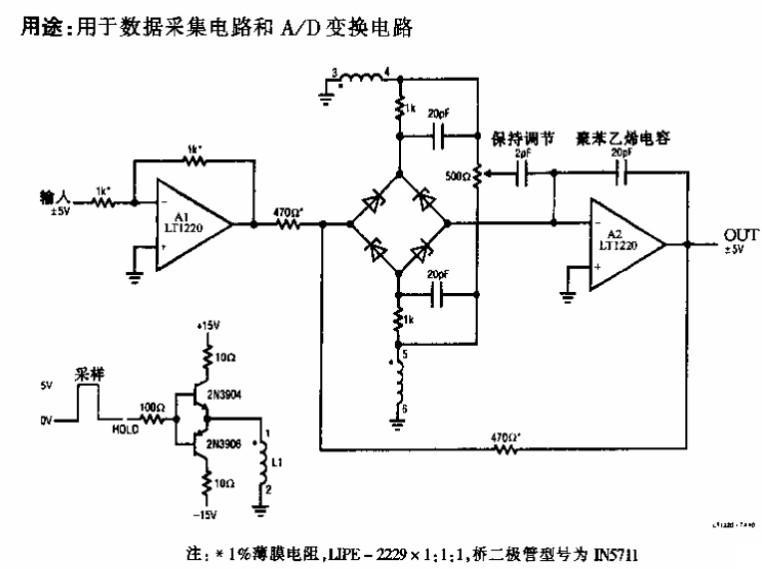

使用運算放大器的采樣和保持電路:

使用運算放大器的采樣和保持電路

當 MOSFET 作為閉合開關工作時,通過漏極端子提供給它的模擬信號將被饋送到電容器,然后電容將充電至其峰值。當釋放開關時,電容停止充電。由于電路末端連接了高阻抗運算放大器,電容將因此而產生高阻抗,因此無法放電。

指向電容將電荷保持準確的時間量,這可以稱為持有期。而產生i/p電壓樣本的時間稱為采樣周期。運算放大器在整個保持期間處理的 o/p。因此,持有期對運算放大器有影響。

四、采樣保持電路類型

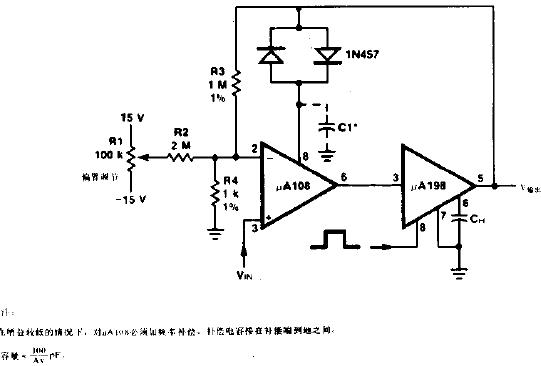

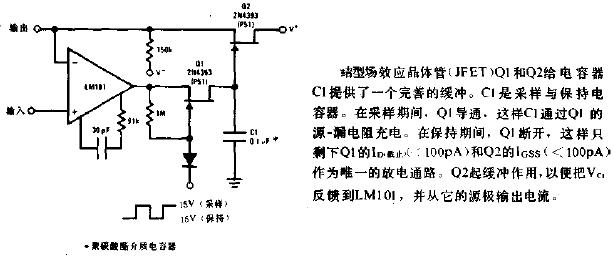

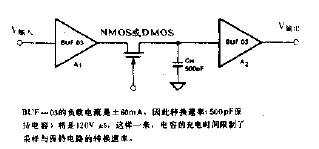

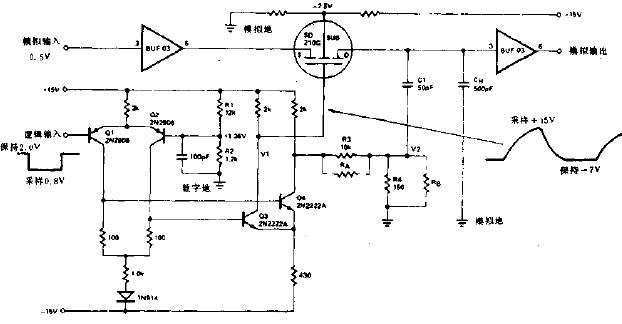

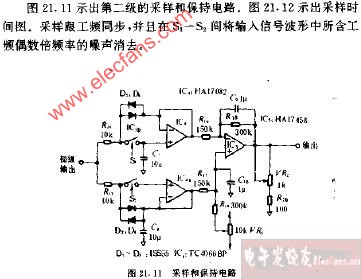

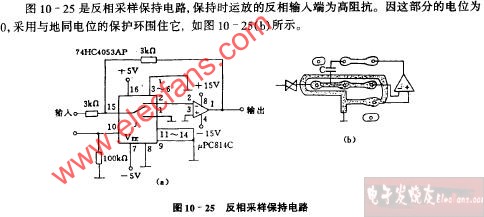

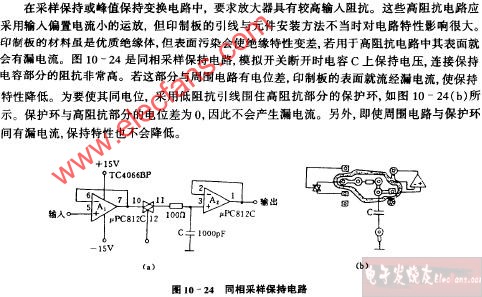

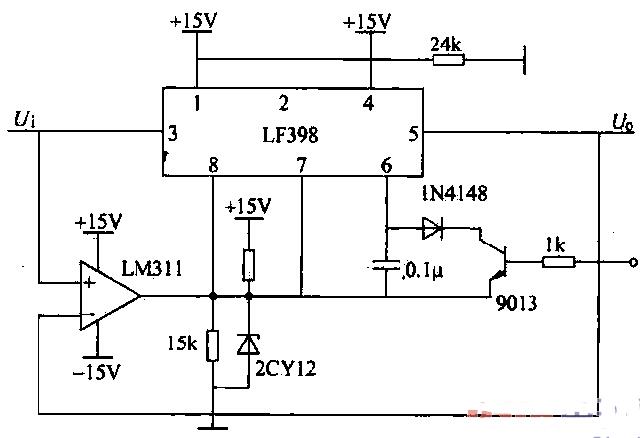

采樣保持電路有多種設計,下面將討論一些采樣保持電路,下面這些討論的電路都使用了 JFET 作為開關。

在電路中,JFET 在采樣時間內打開,在此期間保持電容中的電荷達到最大值,不能超過輸入信號。當采樣周期結束時,JFET 關斷,保持電容與輸入信號斷開。通過斷開電容,確保輸出與輸入電壓保持一致,并且不隨輸入信號的變化而變化。可能是保持電容兩端的電壓具有低壓差并且使用這兩個緩沖器來補償的情況,一個在輸出端,另一個在輸入端。

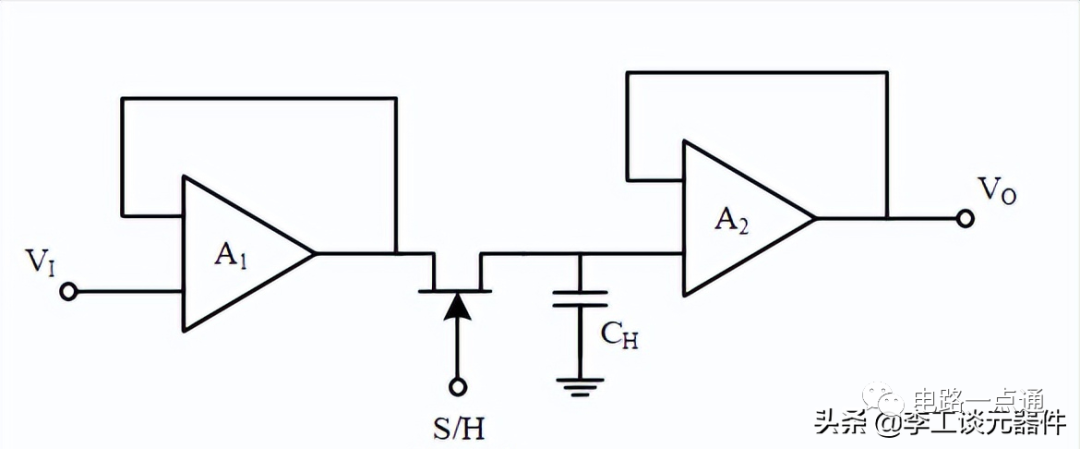

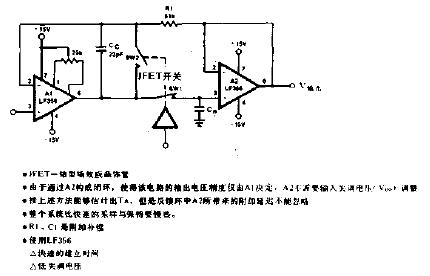

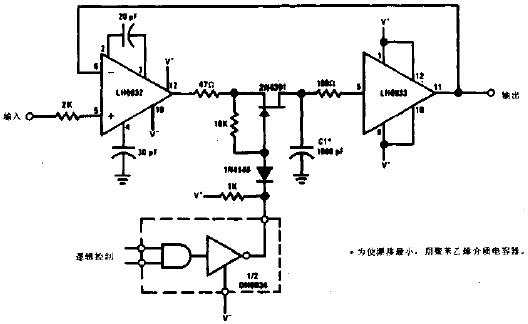

1、開環采樣保持電路

開環式采樣保持電路

由于這是一個開環電路,加上電路中沒有反饋(閉環配置),因此它比閉環電路更快。另一方面,閉環設計通過反饋產生更高的精度。對于采樣和保持電路,采集時間是一個關鍵因素,必須盡可能短。

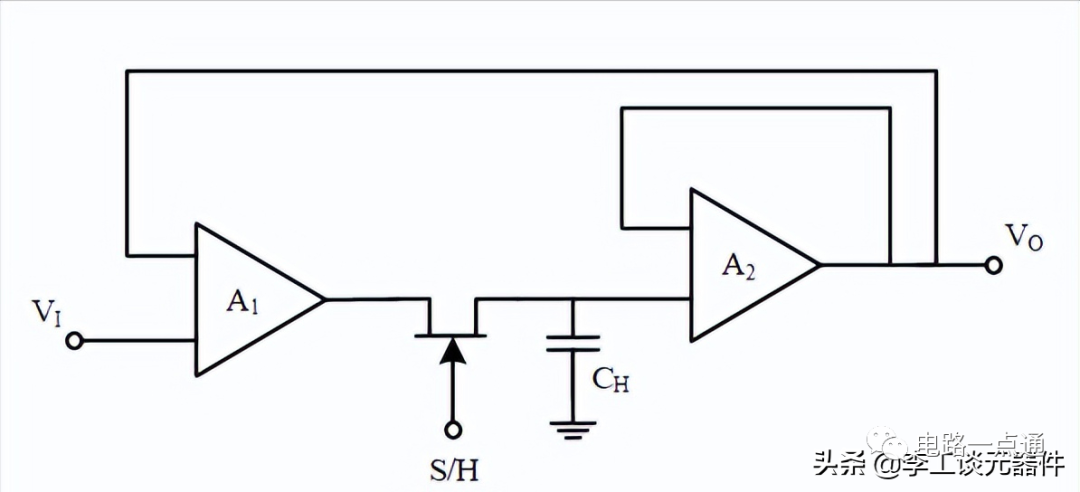

2、閉環式采樣

下面的反饋回路電路是上一個的改進變體,因為 JFET 的導通電阻包含在反饋回路中,所以其他兩個參數決定了采集時間。

閉環采樣保持電路

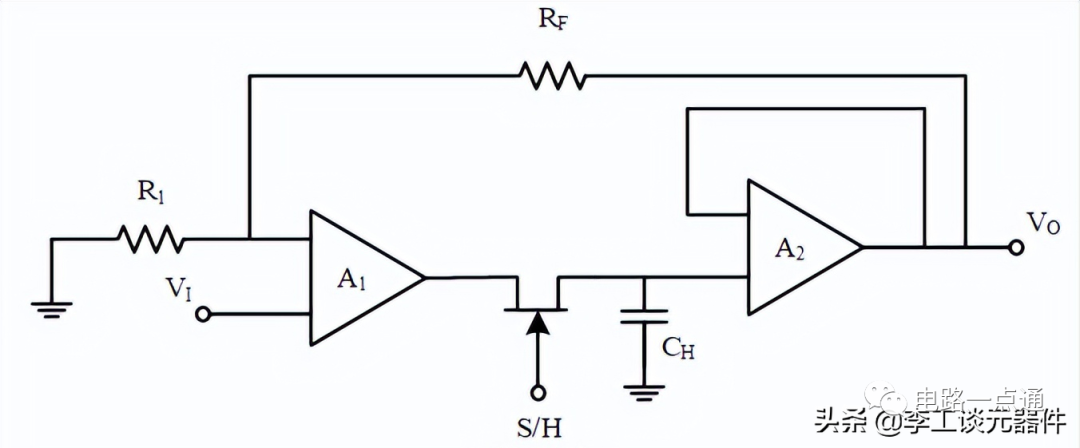

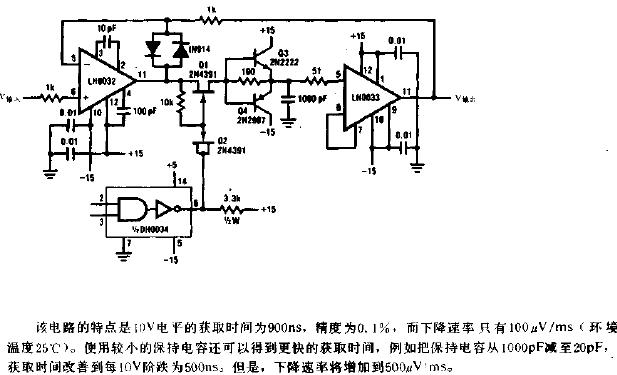

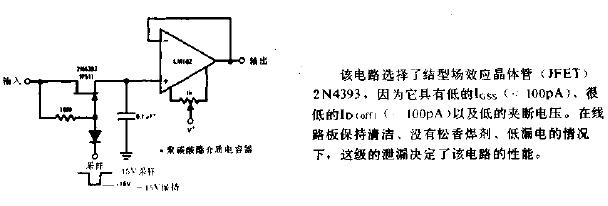

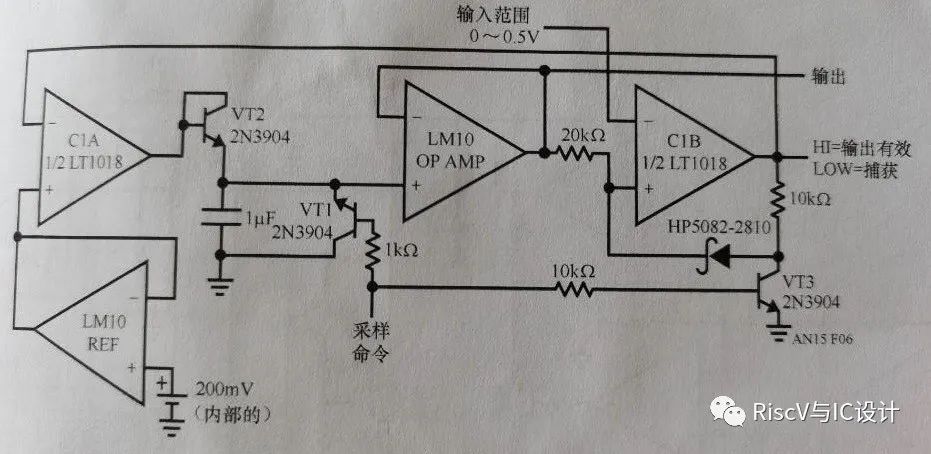

3、閉環采樣和保持電壓增益電路

通過提供電壓增益,以下電路表現就很好。要計算電路的電壓增益,可以使用反饋電阻 (Rf) 和輸入電阻 (R1)(電壓增益的公式如下所示)。A = 1 + (Rf / R1)

閉環采樣和保持電壓增益電路

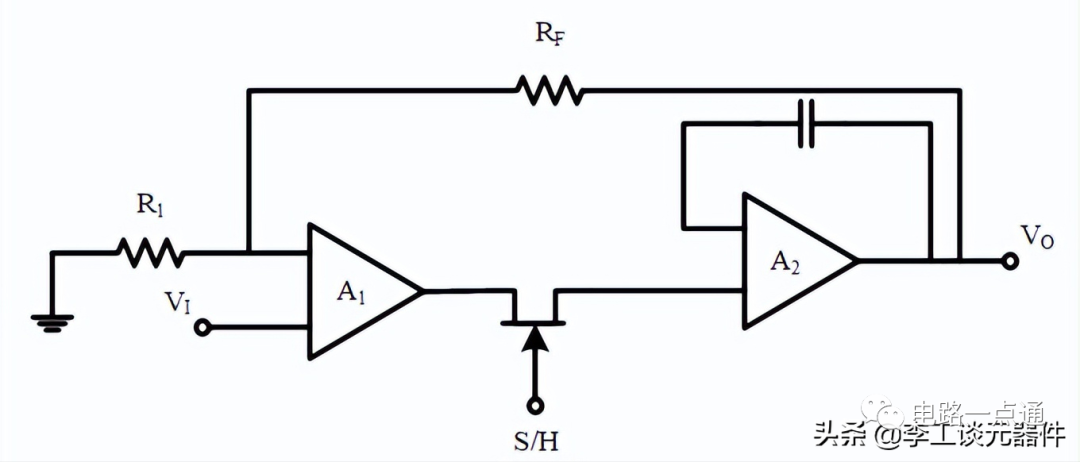

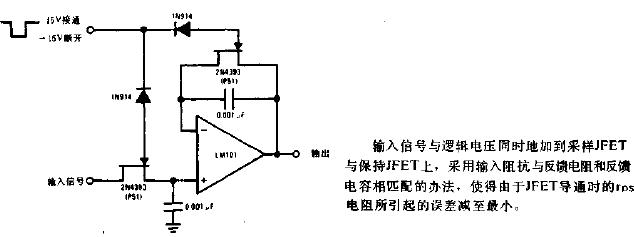

4、具有同相端子的閉環采樣和保持電壓增益電路

最后一個電路比上一個電路提供了一些優勢。最重要的變化是保持電容的位置,這導致 的同相端電壓相等,電容兩端的電壓除以放大器的增益。因此,保持電容充電更快,從而導致采集時間變得更快。

具有同相端子的閉環采樣和保持電壓增益電路

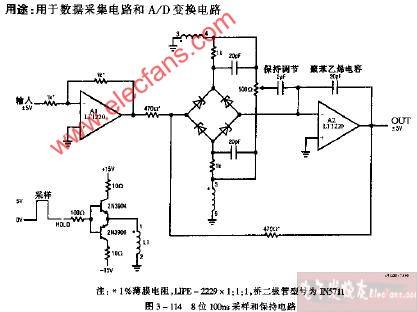

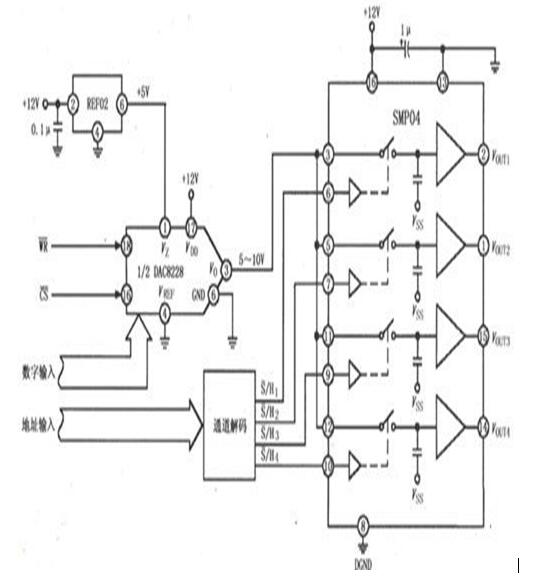

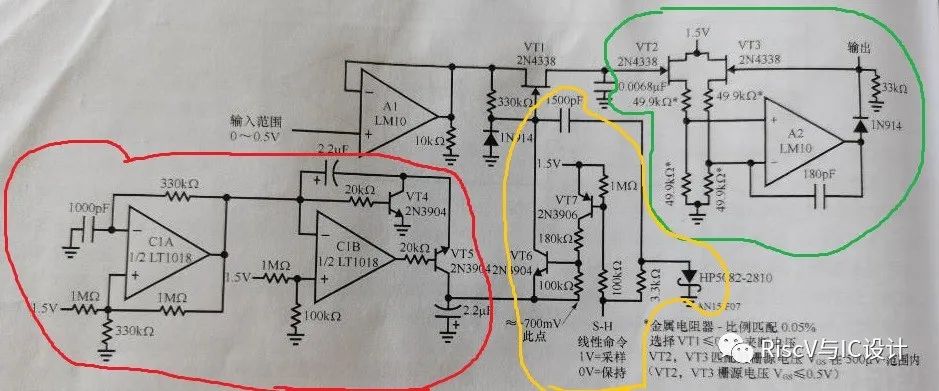

五、采樣保持電路設計

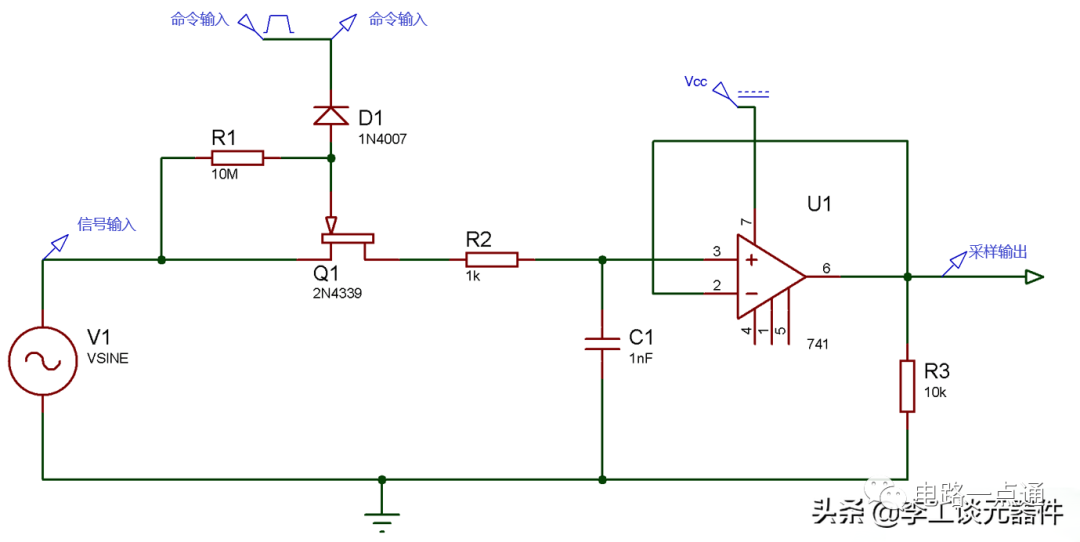

1、采樣保持電路設計所需組件

UA741運算放大器 IC

2N4339 N 溝道 JFET

模擬輸入和脈沖輸入發生器

電阻(10k、10M)

二極管 (1N4007)

電容(0.1uf - 1nos)

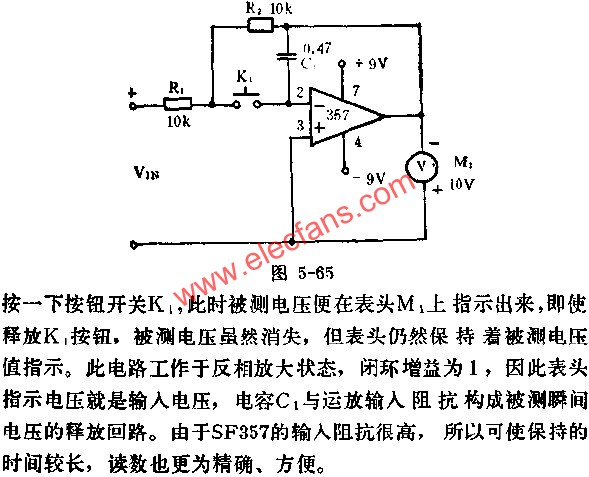

采樣保持電路

為了在輸入端提供模擬信號,你可以使用 6-0-6 降壓變壓器。而且,為了向晶體管提供脈沖或 PWM 輸入,你可以在非穩態模式下使用 555 定時器 IC。我們還需要一個直流電源來為運算放大器 IC 提供 Vcc,其范圍為 +5 至 +15V。

2、采樣保持電路設計的工作原理

你在電路上面圖中可以看到的,我們使用了 2N4339 N 溝道 JFET、一個運算放大器和一個電容。命令輸入(PWM 輸入)連接到 2N4339 晶體管的柵極端子。

將命令輸入的初始電壓設置為 -15V,脈沖電壓設置為 15V。因此,只要命令輸入電壓為負,二極管就會正向偏置,從而導致晶體管導通,反之亦然。

運算放大器741在這里用作電壓跟隨器,因為電壓跟隨器通常具有高輸入阻抗和低輸出阻抗。這在輸入信號為低電流時使用,因為電壓跟隨器可以為下一級提供足夠的電流。

因此,每當命令輸入為高電平時,晶體管就作為閉合開關工作,此時電容開始充電至其峰值并存儲輸入信號的樣本,以便晶體管處于導通狀態。

現在,當命令輸入為低電平時,晶體管作為開路開關工作,電容將經歷高阻抗,因此它無法放電并在特定時間段內保持電荷。這個時間被稱為持有期。并且,電路對輸入信號進行采樣的時間稱為采樣周期。

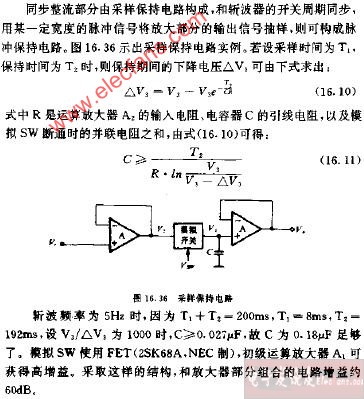

六、采樣保持電路性能參數

1、輸入輸出波形

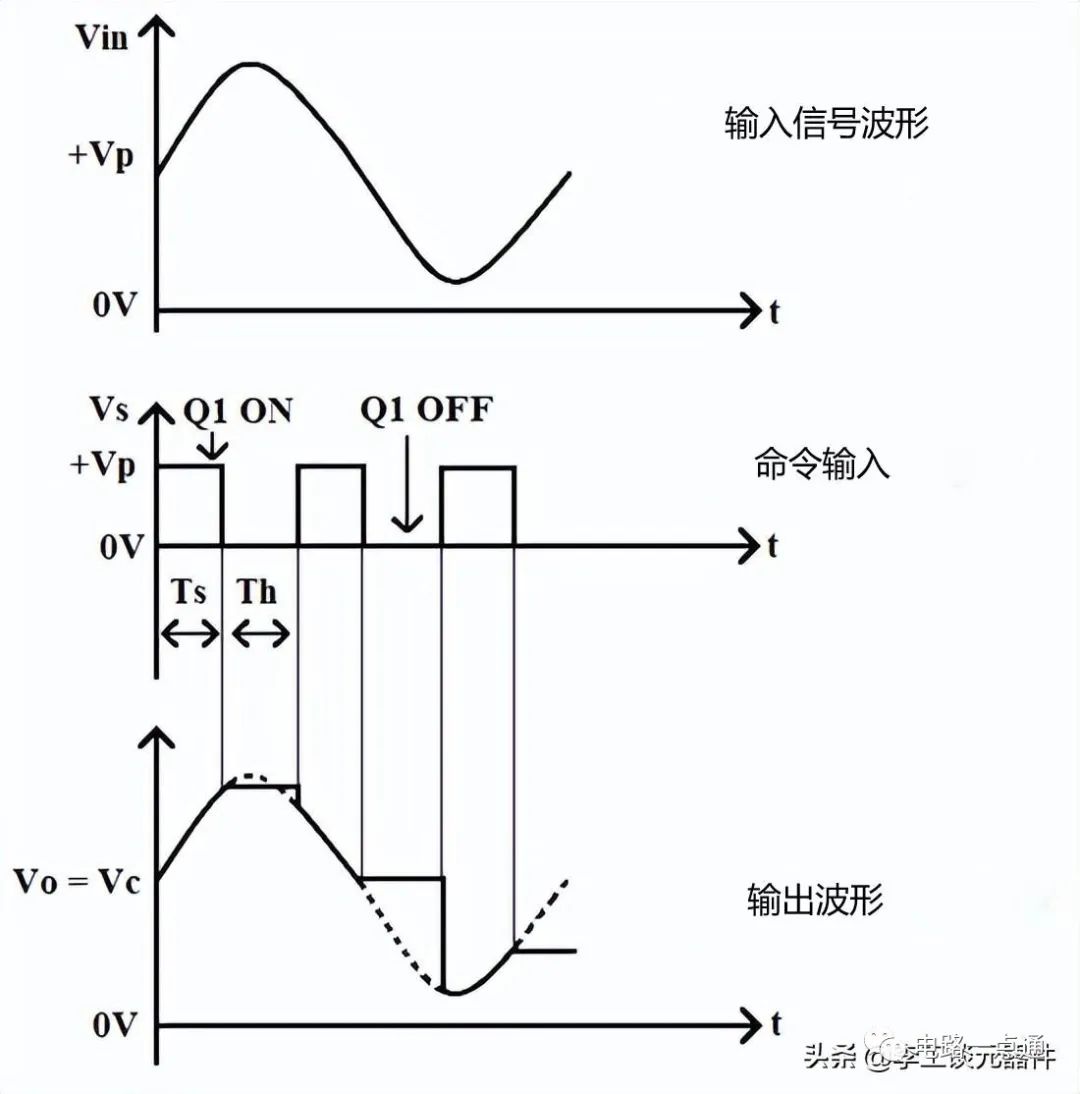

采樣保持電路輸入輸出波形

從上圖中可以清楚地看出,采樣保持電路在命令輸入為高電平時對輸入信號進行采樣,并在輸出端復制相同的采樣。當命令輸入為低電平時,它保持采樣信號的最后一個電壓電平。

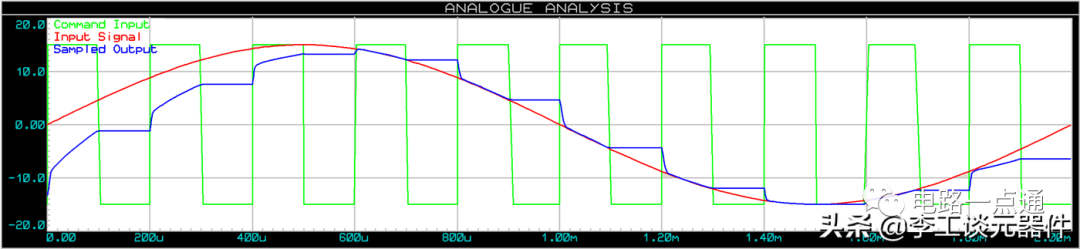

如果我們 模擬我們的采樣保持電路,我們將得到下面波形。

采樣保持電路輸入輸出波形

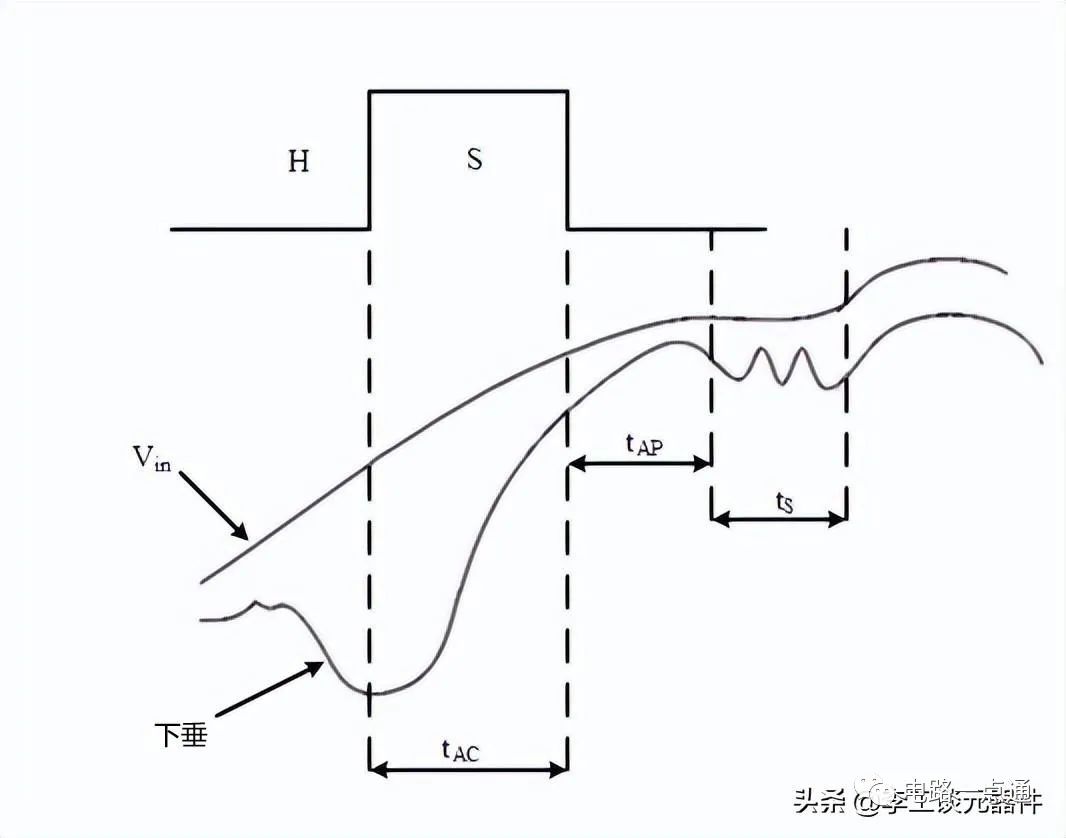

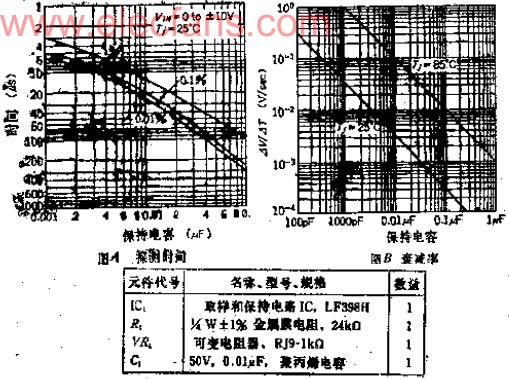

2、采集時間

在采樣期間,采集時間是保持電容中的電荷達到接近輸入電壓的水平所需的時間。采集時間受三個因素影響:

RC 時間常數,其中 C 代表保持電容,R 代表導通電阻,用于計算時間長度的常數。

運算放大器壓擺率, 是晶體管中的晶體管中的晶體管中的晶體管中的晶體管的速率。

運算最大放大器的輸出電流。

采集時間

3、光圈時間

光圈時間是保持命令開始和 VO 監控 Vi 之間的延遲。跨驅動器和開關電路的傳播延遲是這種延遲的最常見來源,保持命令必須提前一個孔徑時間啟動,以獲得最佳時序。

4、孔徑不確定度

孔徑時間并不一致,并且因樣本而異,這種類型的不確定性被稱為孔徑不確定性。這將對保持指揮部的發展產生重大影響。

5、保持模式穩定時間

應用保持命令后,輸出 (VO ) 在特定誤差帶百分比(0.01%、0.1% 或 1%)內的穩定時間稱為保持模式穩定時間。

6、保持步長

在從采樣模式切換到保持模式時,寄生電容可能會導致保持電容和開關之間發生意外的電荷轉移。這對電容電壓和輸出電壓都有影響。保持步長是輸出電壓和所需值之間的差值。

7、饋通

在保持模式下,開關的寄生電容可能會在 Vi和 Vo之間產生交流耦合。出現饋通現象,導致輸出電壓隨輸入電壓的變化而變化。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論