PCB布線設(shè)計(jì)時(shí)寄生電容的計(jì)算方法

- 電容(147007)

相關(guān)推薦

如何消除寄生電容的電路設(shè)計(jì)方案

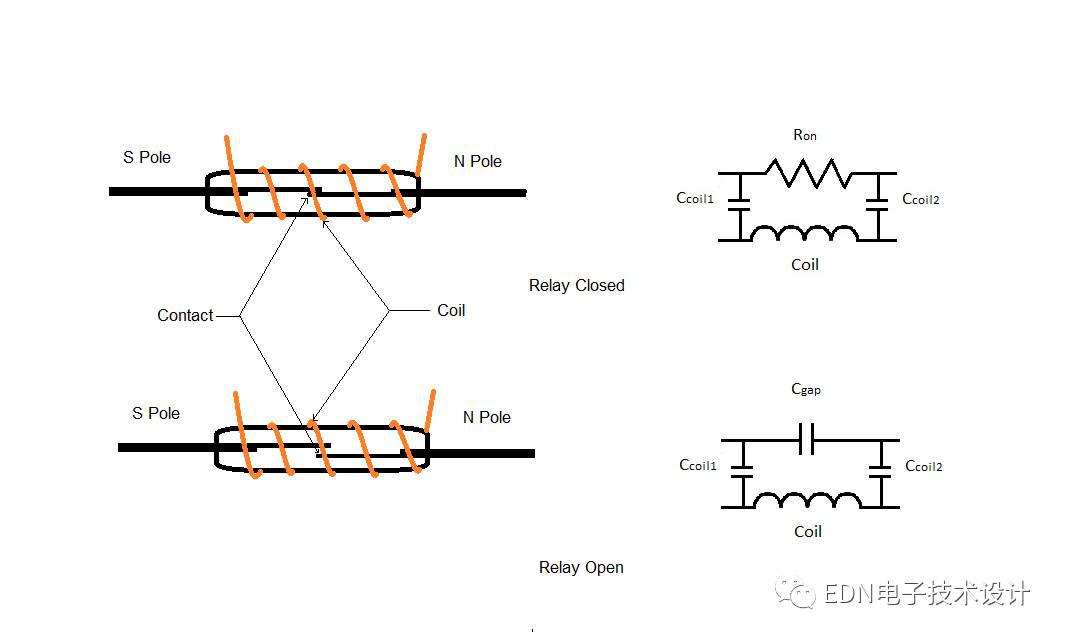

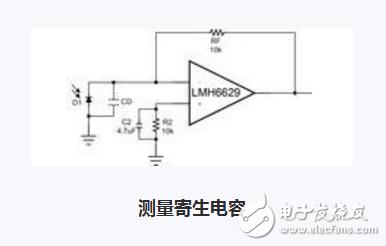

在被測(cè)點(diǎn)阻抗較高時(shí),即使該點(diǎn)僅有較小的電容,其帶寬也會(huì)受限。在基于磁簧繼電器的多路選擇器中,由于各磁簧繼電器的寄生電容會(huì)在輸出端并聯(lián),加大了輸出端的電容,使得電路的帶寬變窄。

2018-12-14 15:14:47 21352

21352

21352

21352

寄生電容對(duì)三極管產(chǎn)生怎樣的影響?

首先,我們介紹設(shè)計(jì)寄生電容對(duì)三極管產(chǎn)生的影響;然后,我們學(xué)習(xí)上拉電阻和下拉電阻的含義以及在電路中的使用方法。

2019-05-20 07:28:00 9438

9438

9438

9438

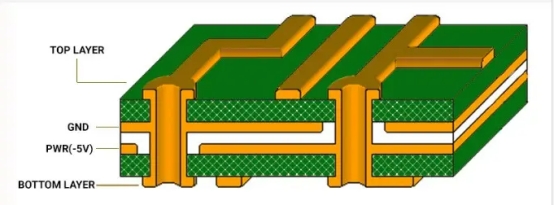

PCB布局的DC電阻,寄生電容和寄生電感

實(shí)際系統(tǒng)的很多方面都會(huì)在PCB布局,IC或任何其他電氣系統(tǒng)中產(chǎn)生意外的寄生現(xiàn)象。重要的是在嘗試使用SPICE仿真提取寄生效應(yīng)之前,請(qǐng)注意電路圖中無法考慮的內(nèi)容。

2020-12-31 12:01:41 8249

8249

8249

8249

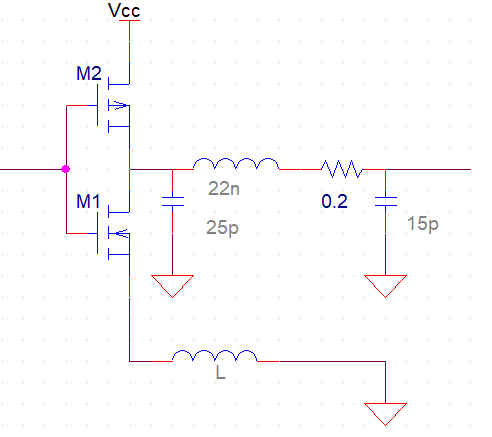

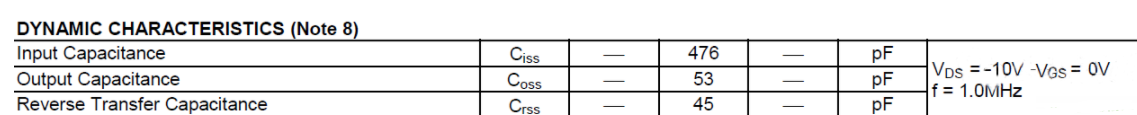

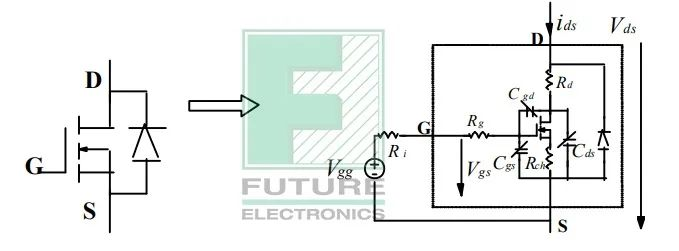

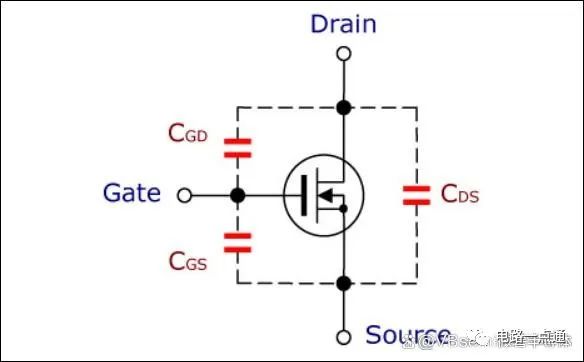

MOSFET寄生電容參數(shù)如何影響開關(guān)速度

我們應(yīng)該都清楚,MOSFET 的柵極和漏源之間都是介質(zhì)層,因此柵源和柵漏之間必然存在一個(gè)寄生電容CGS和CGD,溝道未形成時(shí),漏源之間也有一個(gè)寄生電容CDS,所以考慮寄生電容時(shí),MOSFET

2021-01-08 14:19:59 15830

15830

15830

15830

PCB雜散電容大小計(jì)算方法 PCB雜散電容怎么消除

在整個(gè)PCBA生產(chǎn)制造過程中, PCB 設(shè)計(jì)是至關(guān)重要的一部分,今天主要是關(guān)于 PCB 雜散電容、影響PCB 雜散電容的因素,PCB 雜散電容計(jì)算,PCB雜散電容怎么消除。

2023-09-11 09:41:20 770

770

770

770

PCB寄生電容的影響 PCB寄生電容計(jì)算 PCB寄生電容怎么消除

寄生電容有一個(gè)通用的定義:寄生電容是存在于由絕緣體隔開的兩個(gè)導(dǎo)電結(jié)構(gòu)之間的虛擬電容(通常不需要的),是PCB布局中的一種效應(yīng),其中傳播的信號(hào)表現(xiàn)得好像就是電容,但其實(shí)并不是真正的電容。

2024-01-18 15:36:14 866

866

866

866

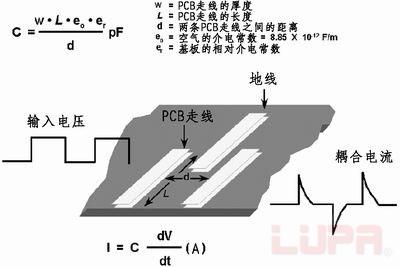

PCB布線

布線需要考慮的問題很多,但是最基本的的還是要做到周密,謹(jǐn)慎。 寄生元件危害最大的情況 印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走

2011-11-06 14:32:56

PCB布線設(shè)計(jì)(三)

PCB布線設(shè)計(jì)(三)印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走線形成;電路板上的走線、焊盤和平行走線會(huì)產(chǎn)生寄生電容;寄生電感的產(chǎn)生途徑

2017-11-10 10:02:54

PCB布線設(shè)計(jì)(三)

布線需要考慮的問題很多,但是最基本的的還是要做到周密,謹(jǐn)慎。 寄生元件危害最大的情況 印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走

2018-11-23 11:07:46

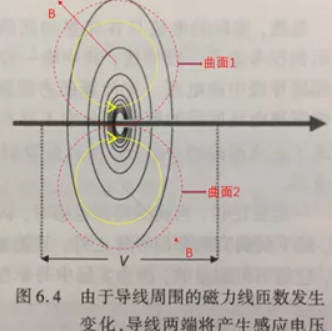

PCB布線設(shè)計(jì)-模擬和數(shù)字布線的異同

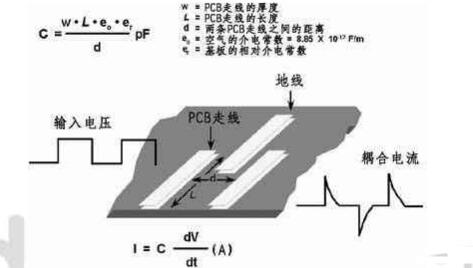

在PCB上布兩條靠近的走線,很容易形成寄生電容。由于這種電容的存在,在一條走線上的快速電壓變化,可在另一條走線上產(chǎn)生電流信號(hào) 圖6 如果不注意走線的放置,PCB中的走線可能產(chǎn)生線路感抗和互感。這種

2011-09-02 09:36:14

pcb布線規(guī)則(2)

。很顯然,在高速,高密度的PCB設(shè)計(jì)時(shí),設(shè)計(jì)者總是希望過孔越小越好,這樣板上可以留有更多的布線空間,此外,過孔越小,其自身的寄生電容也越小,更適合用于高速電路。但孔尺寸的減小同時(shí)帶來了成本的增加,而且過孔

2015-07-24 12:29:05

寄生電容器是什么?

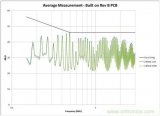

低頻下,所有三種電容器均未表現(xiàn)出寄生分量,因?yàn)樽杩姑黠@只與電容相關(guān)。但是,鋁電解電容器阻抗停止減小,并在相對(duì)低頻時(shí)開始表現(xiàn)出電阻特性。這種電阻特性不斷增加,直到達(dá)到某個(gè)相對(duì)高頻為止(電容器出現(xiàn)電感)。鋁聚合物電容器為與理想狀況不符的另一種電容器。

2019-08-15 06:33:32

寄生電容有什么含義?

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現(xiàn)出來的電容特性。實(shí)際上,一個(gè)電阻等效于一個(gè)電容,一個(gè)電感,和一個(gè)電阻的串聯(lián),在低頻情況下表現(xiàn)不是很明顯,而在高頻情況下,等效值會(huì)增大,不能忽略。

2019-09-29 10:20:26

LTC6268-10為了使寄生電容降到最低,對(duì)電路板的材料類型和厚度有什么要求嗎?

在LTC6268-10芯片手冊(cè)中,為了減小寄生反饋電容的影響,采用反饋電阻分流的方式減小寄生電容。

請(qǐng)問,在這種工作方式下,為了使寄生電容降到最低,對(duì)電路板的材料類型和厚度有什么要求嗎?

2023-11-16 06:28:44

MOSFET寄生電容對(duì)LLC串聯(lián)諧振電路ZVS的影響

MOSFET的工作波形。由于感性負(fù)載下,電流相位上會(huì)超前電壓,因此保證了MOSFET運(yùn)行的ZVS。要保證MOSFET運(yùn)行在感性區(qū),諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲(chǔ)

2018-11-21 15:52:43

MOSFET寄生電容對(duì)LLC串聯(lián)諧振電路ZVS的影響

感性負(fù)載下,電流相位上會(huì)超前電壓,因此保證了MOSFET運(yùn)行的ZVS。要保證MOSFET運(yùn)行在感性區(qū),諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲(chǔ)的電荷可以在死區(qū)時(shí)間內(nèi)被

2018-07-13 09:48:50

mos管寄生電容是什么

寄生電容是指電感,電阻,芯片引腳等在高頻情況下表現(xiàn)出來的電容特性。實(shí)際上,一個(gè)電阻等效于一個(gè)電容,一個(gè)電感,一個(gè)電阻的串聯(lián),低頻情況下表現(xiàn)不明顯,而高頻情況下,等效值會(huì)增大。在計(jì)算中我們要考慮

2021-01-11 15:23:51

【我是電子發(fā)燒友】實(shí)現(xiàn)高速PCB之布線問題探討(轉(zhuǎn))

問題的寄生源時(shí),可能用得著幾個(gè)計(jì)算上述那些寄生電容尺寸的基本公式。(公式一)是計(jì)算平行極板電容器的公式,如(圖五)。(公式一)(1)C表示電容值;(2)A表示以cm2為單位的極板面積;(3)k表示PCB

2017-06-19 16:18:30

【轉(zhuǎn)帖】PCB布線技巧

盤區(qū)。這兩部分的尺寸大小決定了過孔的大小。很顯然,在高速,高密度的PCB設(shè)計(jì)時(shí),設(shè)計(jì)者總是希望過孔越小越好,這樣板上可以留有更多的布線空間,此外,過孔越小,其自身的寄生電容也越小,更適合用于高速電路

2017-06-26 17:25:08

【高速PCB布線指南(2)】寄生效應(yīng)

的公式(參見圖8)。T表示PCB的厚度,d表示以cm為單位的通孔直徑。公式(4)示出了如何計(jì)算通孔(參見圖8)引起的寄生電容值。er表示PCB材料的相對(duì)磁導(dǎo)率。T表示PCB的厚度。D1表示環(huán)繞通孔的焊

2018-10-19 13:46:56

從實(shí)踐角度來探討高速電路布線問題

接地平面的脈沖響應(yīng)通孔是另外一種寄生源,它們能引起寄生電感和寄生電容。公式(3)是計(jì)算寄生電感的公式。公式(3)中:T表示PCB的厚度,d表示以cm為單位的通孔直徑。公式(4)是如何計(jì)算通孔

2019-12-16 09:21:50

關(guān)于車用BMS高壓電路中做絕緣電阻檢測(cè)時(shí)如何考慮高壓正負(fù)極對(duì)地的寄生電容對(duì)AD采集影響?

在高壓回路中,正負(fù)極對(duì)地會(huì)產(chǎn)生一個(gè)寄生電容,而寄生電容與回路中的電阻會(huì)組成一個(gè)RC充放電電路。在使用國(guó)標(biāo)電流橋檢測(cè)電路方法時(shí),正負(fù)極對(duì)地的寄生電容和電阻的大小會(huì)影響到AD采集。在RC充滿的時(shí)間一般為3RC以上,在此過程中如何探討RC電路充滿電壓的時(shí)間?

2020-07-27 23:14:10

再讀大牛的一篇經(jīng)典好文章——實(shí)現(xiàn)高速PCB之布線問題探討

減小寄生電感的影響。(圖七) 有接地平面和沒有接地平面的脈沖回應(yīng) 通孔是另外一種寄生源;它們能引起寄生電感和寄生電容。(公式三)是計(jì)算寄生電感的公式,請(qǐng)參考(圖八)。 (公式三)(1)T表示PCB

2018-08-10 08:56:18

如何處理好電源中的寄生電容獲得符合EMI標(biāo)準(zhǔn)的電源?

從開關(guān)節(jié)點(diǎn)到輸入引線的少量寄生電容(100毫微微法拉)會(huì)讓您無法滿足電磁干擾(EMI)需求。那100fF電容器是什么樣子的呢?在Digi-Key中,這種電容器不多。即使有,它們也會(huì)因寄生問題而提

2019-05-14 08:00:00

實(shí)現(xiàn)高速PCB之布線問題探討

源時(shí),可能用得著幾個(gè)計(jì)算上述那些寄生電容尺寸的基本公式。(公式一)是計(jì)算平行極板電容器的公式,如(圖五)。 (公式一)(1)C表示電容值;(2)A表示以cm2為單位的極板面積;(3)k表示PCB材料

2018-10-12 10:22:31

當(dāng)寄生電容直接耦合到電源輸入電線時(shí)會(huì)發(fā)生的情況分析

大部分傳導(dǎo) EMI 問題都是由共模噪聲引起的。而且,大部分共模噪聲問題都是由電源中的寄生電容導(dǎo)致的。對(duì)于該討論主題的第 1 部分,我們著重討論當(dāng)寄生電容直接耦合到電源輸入電線時(shí)會(huì)發(fā)生的情況1. 只需

2022-11-22 07:29:30

提高PCB布線的一些經(jīng)驗(yàn)

),二是鉆孔周圍的焊盤區(qū)。這兩部分的尺寸大小決定了過孔的大小。很顯然,在高速,高密度的PCB設(shè)計(jì)時(shí),設(shè)計(jì)者總是希望過孔越小越好,這樣板上可以留有更多的布線空間,此外,過孔越小,其自身的寄生電容也越小,更適合

2018-05-07 08:20:06

晶振相鄰層挖空是如何控制寄生電容Cp的呢?

貼片晶振的PCB layout需要注意哪些晶振相鄰層挖空是如何控制寄生電容Cp的呢?為什么溫度會(huì)影響晶振頻率呢?

2021-02-26 07:43:28

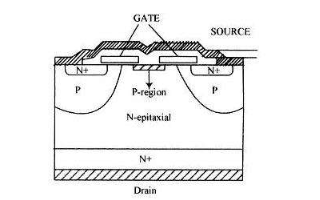

理解功率MOSFET的寄生電容

的差異相互擴(kuò)散,也會(huì)在PN結(jié)的兩側(cè)產(chǎn)生電荷存儲(chǔ)效應(yīng),這些因素作用在一起,在任何半導(dǎo)體功率器件內(nèi)部,就會(huì)產(chǎn)生相應(yīng)的寄生電容。MOSFET的寄生電容是動(dòng)態(tài)參數(shù),直接影響到其開關(guān)性能,MOSFET的柵極電荷

2016-12-23 14:34:52

磁芯對(duì)電感寄生電容的影響分析

;strong>減小電感寄生電容的方法<br/></strong>如果磁芯是導(dǎo)體,首先:&

2009-12-23 16:07:01

超強(qiáng)PCB布線設(shè)計(jì)經(jīng)驗(yàn)談附原理圖(3)

:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走線形成;電路板上的走線、焊盤和平行走線會(huì)產(chǎn)生寄生電容;寄生電感的產(chǎn)生途徑包括環(huán)路電感、互感和過孔。當(dāng)將電路原理圖轉(zhuǎn)化為實(shí)際的PCB

2008-10-28 09:26:35

飛捷教你二極管如何去降低寄生電容?

,寄生電容的影響已經(jīng)不能忽視了。在系統(tǒng)中,這些不期望的電容來自方方面面,比如PCB的材質(zhì)、厚度、板層結(jié)構(gòu)、走線平行度,這些都是影響PCB板的寄生電容,還有元器件本身的寄生電容,最可惡的是這些東西還受

2020-12-15 15:48:52

pcb布線經(jīng)驗(yàn)精華

布線需要考慮的問題很多,但是最基本的的還是要做到周密,謹(jǐn)慎。寄生元件危害最大的情況印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感

2008-07-23 17:13:40 0

0

0

0鐵氧體環(huán)形電感器寄生電容的提取

鐵氧體電感器在較高頻率時(shí)可等效為“電阻、電感”的串聯(lián)支路與一寄生電容的并聯(lián),該電容的存在對(duì)電感器的高頻性能有重要影響。本文建立了鐵氧體環(huán)形電感器2D平行平面場(chǎng)和3D

2009-04-08 15:45:17 66

66

66

66PCB布線設(shè)計(jì)3

印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走線形成;電路板上的走線、焊盤和平行走線會(huì)產(chǎn)生寄生電容;寄生

2009-10-17 15:36:29 42

42

42

42PCB板寄生元件的危害

PCB板寄生元件的危害:印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走線形成;電路板上的走線、焊盤和平行走線會(huì)

2009-11-15 22:28:47 0

0

0

0寄生電容對(duì)電磁干擾濾濾器效能的影響

寄生電容對(duì)電磁干擾濾濾器效能的影響

本文將針對(duì)交換式電源供應(yīng)器在高頻切換所帶來的傳導(dǎo)性電磁干擾(Conducted Electromagnetic Interference)問題,藉由不同繞

2010-06-19 16:30:37 54

54

54

54PCB布線設(shè)計(jì)(之三)

寄生元件危害最大的情況印刷電路板布線產(chǎn)生的主要寄生元件包括:寄生電阻、寄生電容和寄生電感。例如:PCB的寄生電阻由元件之間的走線形成;電路板上的走線、焊盤和平行

2006-09-25 14:37:59 342

342

342

342電容的串并聯(lián)計(jì)算方法

電容的串并聯(lián)計(jì)算方法

電容串聯(lián)后容量是減小了,但是這樣可以增加他的耐壓值。計(jì)算公式是:C1*C2/(C1+C2) 電容并聯(lián)后容量是增大了,并聯(lián)耐壓數(shù)值按最小的計(jì)

2008-12-13 22:24:17 119276

119276

119276

119276

一種減少VDMOS寄生電容的新結(jié)構(gòu)

一種減少VDMOS寄生電容的新結(jié)構(gòu)

0 引 言 VDMOS與雙極晶體管相比,它的開關(guān)速度快,開關(guān)損耗小,輸入電阻高,驅(qū)動(dòng)電流小,頻率特性好,跨導(dǎo)高度線性

2009-11-25 17:49:50 1002

1002

1002

1002一種減少VDMOS寄生電容的新結(jié)構(gòu)

一種減少VDMOS寄生電容的新結(jié)構(gòu)

0 引 言 VDMOS與雙極晶體管相比,它的開關(guān)速度快,開關(guān)損耗小,輸入電阻高,驅(qū)動(dòng)電流小,頻率特性好,跨

2009-11-27 09:24:23 613

613

613

613一種減少VDMOS寄生電容的新結(jié)構(gòu)

一種減少VDMOS寄生電容的新結(jié)構(gòu)

0 引 言 VDMOS與雙極晶體管相比,它的開關(guān)速度快,開關(guān)損耗小,輸入電阻高,驅(qū)動(dòng)

2010-01-11 10:24:05 1321

1321

1321

1321寄生電容,寄生電容是什么意思

寄生電容,寄生電容是什么意思

寄生的含義 寄身的含義就是本來沒有在那個(gè)地方設(shè)計(jì)電容,但由于布線構(gòu)之間總是有互容,互

2010-03-23 09:33:55 2557

2557

2557

2557傳輸線等效電容的計(jì)算方法

傳輸線等效電容的計(jì)算方法

從題目的信息可以得出兩個(gè)信息:(1)這條傳輸線是高速線,沒有特殊說明,缺省阻抗應(yīng)該是50歐姆;

2010-04-16 17:32:38 9201

9201

9201

9201甲類單端的簡(jiǎn)易計(jì)算方法

甲類單端的簡(jiǎn)易計(jì)算方法甲類單端的簡(jiǎn)易計(jì)算方法甲類單端的簡(jiǎn)易計(jì)算方法

2016-01-19 15:37:38 0

0

0

0寄生電容耦合到電源_共模EMI問題的最常見來源

電磁干擾EMI中電子設(shè)備產(chǎn)生的干擾信號(hào)是通過導(dǎo)線或公共電源線進(jìn)行傳輸,互相產(chǎn)生干擾稱為傳導(dǎo)干擾。傳導(dǎo)干擾給不少電子工程師帶來困惑,如何解決傳導(dǎo)干擾?這里,我們先著重討論當(dāng)寄生電容直接耦合到電源輸入

2018-05-18 01:17:00 2785

2785

2785

2785

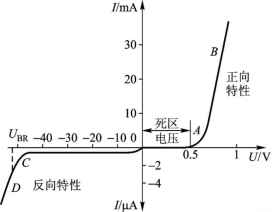

如何妙用二極管減少寄生電容

二極管以其單向?qū)щ娞匦裕谡鏖_關(guān)方面發(fā)揮著重要的作用;其在反向擊穿狀態(tài)下,在一定電流范圍下起到穩(wěn)壓效果。令人意外的是,利用二極管的反偏壓結(jié)電容,能夠有效地減少信號(hào)線上的接入寄生電容,這里將近一步討論這個(gè)運(yùn)用。

2017-03-21 11:31:30 3813

3813

3813

3813

寄生電容影響升壓變壓器的設(shè)計(jì)

升壓設(shè)計(jì)中最關(guān)鍵的部件之一像圖1是變壓器。變壓器的寄生組件,可以使他們偏離它們的理想特性和寄生電容與二次關(guān)聯(lián)可引起大共鳴開關(guān)電流前沿的電流尖峰波形。這些尖峰可以導(dǎo)致調(diào)節(jié)器顯示表現(xiàn)為義務(wù)的不穩(wěn)定的操作

2017-05-02 14:15:40 19

19

19

19一文讀懂二極管在寄生電容處理間的妙用

大家最熟悉的就是二極管的單向?qū)щ娦裕O管如何減少寄生電容。正向接入方法,二極管接在信號(hào)線與附件功能模塊之間,這表示附加功能模塊使能時(shí)是高電平輸出的。

2017-09-23 09:40:09 9649

9649

9649

9649

去耦電容的選擇、容值計(jì)算和pcb布局布線詳解

去耦電容的應(yīng)用的非常廣泛,在電路應(yīng)用過程中對(duì)于去耦電容的容值計(jì)算和PCB電路布局布線有一些我們必須要了解的技巧。

2018-01-28 18:28:00 14406

14406

14406

14406如何消除寄生電容的影響

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現(xiàn)出來的電容特性。實(shí)際上,一個(gè)電阻等效于一個(gè)電容,一個(gè)電感,和一個(gè)電阻的串連,在低頻情況下表現(xiàn)不是很明顯,而在高頻情況下,等效值會(huì)增大,不能忽略。

2018-01-31 10:09:29 21526

21526

21526

21526

什么是“寄生電容”?寄生電容與三種電容器!

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現(xiàn)出來的電容特性。實(shí)際上,一個(gè)電阻等效于一個(gè)電容,一個(gè)電感,和一個(gè)電阻的串連,在低頻情況下表現(xiàn)不是很明顯,而在高頻情況下,等效值會(huì)增大,不能忽略。

2018-01-31 10:57:56 26011

26011

26011

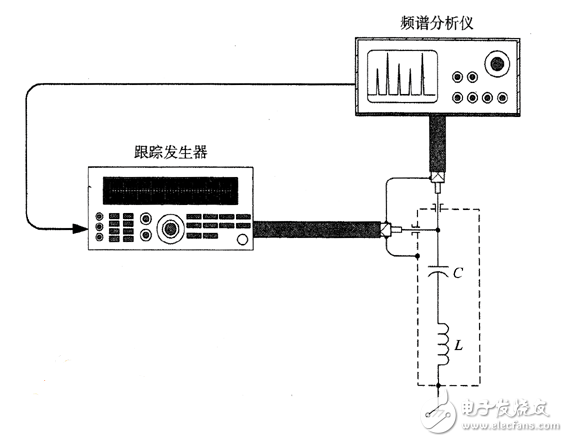

26011測(cè)量寄生電容與寄生電感

電容的寄生電感和寄生電阻主要是指它的引線和極板形成的電感和電阻,尤其是容量較大的電容更為明顯。如果你解剖過電容器,會(huì)看到它的極板是用長(zhǎng)達(dá)1米的金屬薄膜卷曲而成的,其層狀就像一個(gè)幾十、甚至上百圈的線圈

2018-01-31 13:44:55 37299

37299

37299

37299

寄生電感怎么產(chǎn)生的_寄生電感產(chǎn)生原因是什么

本文開始闡述了寄生電感的概念和和寄生元件危害,其次闡述了寄生電感測(cè)量?jī)x的設(shè)計(jì)和寄生電感產(chǎn)生原因或產(chǎn)生方式,最后介紹了PCB過孔的寄生電容和電感的計(jì)算以及使用。

2018-03-28 14:50:42 39049

39049

39049

39049

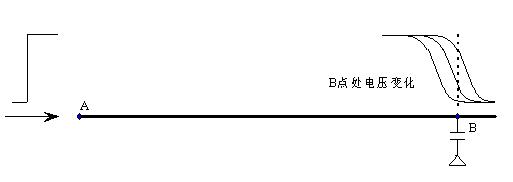

PCB電路中信號(hào)終端電容的作用介紹

信號(hào)的接收端可能是集成芯片的一個(gè)引腳,也可能是其他元器件。不論接收端是什么,實(shí)際的器件的輸入端必然存在寄生電容,接受信號(hào)的芯片引腳和相鄰引腳之間有一定的寄生電容,和引腳相連的芯片內(nèi)部的布線也會(huì)存在寄生電容,另外引腳和信號(hào)返回路徑之間也會(huì)存在寄生電容。

2019-06-21 15:57:47 3143

3143

3143

3143

為什么運(yùn)算放大器反相引腳的寄生電容會(huì)引起不穩(wěn)定

ADI公司的Matt Duff講解為什么運(yùn)算放大器反相引腳的寄生電容會(huì)引起不穩(wěn)定。

2019-06-11 06:11:00 4698

4698

4698

4698寄生電容產(chǎn)生的原因_寄生電容產(chǎn)生的危害

本文首先介紹了寄生電容的概念,其次介紹了寄生電容產(chǎn)生的原因,最后介紹了寄生電容產(chǎn)生的危害。

2019-04-30 15:39:37 28583

28583

28583

28583寄生電容與分布電容的區(qū)別

分布電容強(qiáng)調(diào)的是均勻性。寄生跟強(qiáng)調(diào)的是意外性,指不是專門設(shè)計(jì)成電容,卻有著電容作用的效應(yīng),比如三極管極間電容。單點(diǎn)說,兩條平行走線之間會(huì)產(chǎn)生分布電容,元器件間在高頻下表現(xiàn)出來的容性叫寄生電容。

2019-04-30 15:56:30 19502

19502

19502

19502

磁芯對(duì)電感寄生電容有哪些影響

減小電感寄生電容的方法

如果磁芯是導(dǎo)體,首先:

用介電常數(shù)低的材料增加繞組導(dǎo)體與磁芯之間的距離

2019-07-18 08:00:00 1

1

1

1什么是寄生電感_PCB寄生電容和電感計(jì)算

寄生電感一半是在PCB過孔設(shè)計(jì)所要考慮的。在高速數(shù)字電路的設(shè)計(jì)中,過孔的寄生電感帶來的危害往往大于寄生電容的影響。它的寄生串聯(lián)電感會(huì)削弱旁路電容的貢獻(xiàn),減弱整個(gè)電源系統(tǒng)的濾波效用。我們可以用下面的公式來簡(jiǎn)單地計(jì)算一個(gè)過孔近似的寄生電感。

2019-10-11 10:36:33 19063

19063

19063

19063什么是寄生電容_寄生電容的危害

寄生的含義就是本來沒有在那個(gè)地方設(shè)計(jì)電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容,又稱雜散電容。

2020-09-17 11:56:11 27665

27665

27665

27665mos管寄生電容是什么看了就知道

寄生電容是指電感,電阻,芯片引腳等在高頻情況下表現(xiàn)出來的電容特性。實(shí)際上,一個(gè)電阻等效于一個(gè)電容,一個(gè)電感,一個(gè)電阻的串聯(lián),低頻情況下表現(xiàn)不明顯,而高頻情況下,等效值會(huì)增大。在計(jì)算中我們要考慮進(jìn)去。

2020-10-09 12:04:17 34943

34943

34943

34943去耦電容的容值計(jì)算方法是怎樣的

量C。 ⊿U是實(shí)際電源總線電壓所允許的降低,單位為V。 I是以A(安培)為單位的最大要求電流; ⊿t是這個(gè)要求所維持的時(shí)間。 去耦電容容值計(jì)算方法:推薦使用遠(yuǎn)大于1/m乘以等效開路電容的電容值。 此處m是在IC的電源插針上所允許的電源總線電壓變化的最大百分

2021-04-06 10:59:06 2521

2521

2521

2521基于寄生電容的MOS等效模型

之間或電路模塊之間,由于相互靠近所形成的電容,是設(shè)計(jì)時(shí)不希望得到的電容特性,一般來說在低頻應(yīng)用中我們一般不考慮,但是對(duì)于MOS管驅(qū)動(dòng)電路來說,寄生電容的存在是個(gè)不可繞過的考慮因素。

2022-04-07 09:27:12 4967

4967

4967

4967

什么是寄生電容,什么是寄生電感

本來沒有在那個(gè)地方設(shè)計(jì)電容,但由于布線之間總是有互容,互容就好像是寄生在布線之間的一樣,所以叫寄生電容 寄生電容: 本質(zhì)上還是電容,滿足i=c*du/dt。 電容是用來衡量?jī)?chǔ)存電荷能力的物理量。根據(jù)

2022-07-27 14:23:55 15288

15288

15288

15288

淺談模擬和數(shù)字布線的區(qū)別

PCB設(shè)計(jì)中很容易形成可能產(chǎn)生問題的兩種基本寄生元件:寄生電容和寄生電感。設(shè)計(jì) 電路板時(shí),放置兩條彼此靠近的走線就會(huì)產(chǎn)生寄生電容。

2022-10-20 17:15:12 535

535

535

535分享一些PCB布線小知識(shí)

合理選擇PCB層數(shù)。用中間的電源層(vcclayer)和地層(Gndlayer)可以起到屏蔽作用,有效降低寄生電感和寄生電容,也可大大縮短布線的長(zhǎng)度,減少信號(hào)間的交叉干擾。

2022-10-25 10:47:08 1447

1447

1447

1447

過孔的兩個(gè)寄生參數(shù)是什么?它有什么影響?應(yīng)該怎么消除?

近似用以下公式來計(jì)算:C=1.41εTD1/(D2?D1)。 過孔的寄生電容會(huì)給電路造成的主要影響是延長(zhǎng)了信號(hào)的上升時(shí)間,降低了電路的速度。比如說,對(duì)于一塊厚度為50mil的PCB板,如果使用內(nèi)徑為10mil,焊盤直徑為20mil的過孔,焊盤與地鋪銅區(qū)的距離為32

2022-10-30 13:15:18 2725

2725

2725

2725PCB常見布線規(guī)則

合理選擇PCB層數(shù)。用中間的電源層(vcc layer)和地層(Gnd layer)可以起到屏蔽作用,有效降低寄生電感和寄生電容,也可大大縮短布線的長(zhǎng)度,減少信號(hào)間的交叉干擾。

2023-01-03 16:11:27 2000

2000

2000

2000PCB阻抗不連續(xù)解決方法分析

過孔的寄生電容可以導(dǎo)致信號(hào)上升時(shí)間延長(zhǎng),傳輸速度減慢,從而惡化信號(hào)質(zhì)量。 同樣,過孔同時(shí)也存在寄生電感,在高速數(shù)字PCB中,寄生電感帶來的危害往往大于寄生電容。

2023-01-12 15:01:27 415

415

415

415MOSFET的寄生電容及其溫度特性

繼前篇的Si晶體管的分類與特征、基本特性之后,本篇就作為功率開關(guān)被廣為應(yīng)用的Si-MOSFET的特性作補(bǔ)充說明。MOSFET的寄生電容:MOSFET在結(jié)構(gòu)上存在下圖所示的寄生電容。

2023-02-09 10:19:24 1995

1995

1995

1995

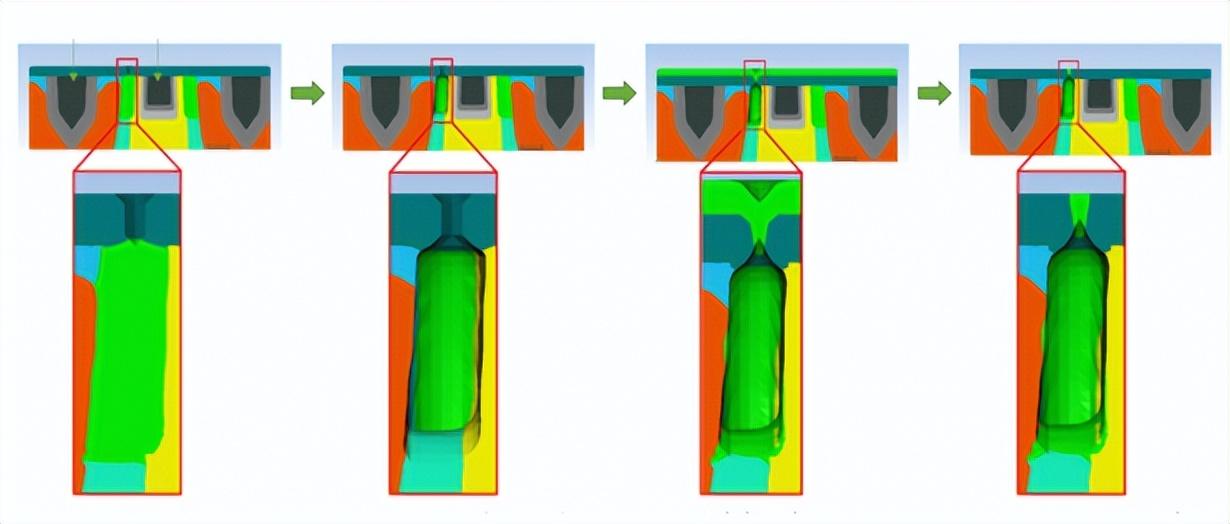

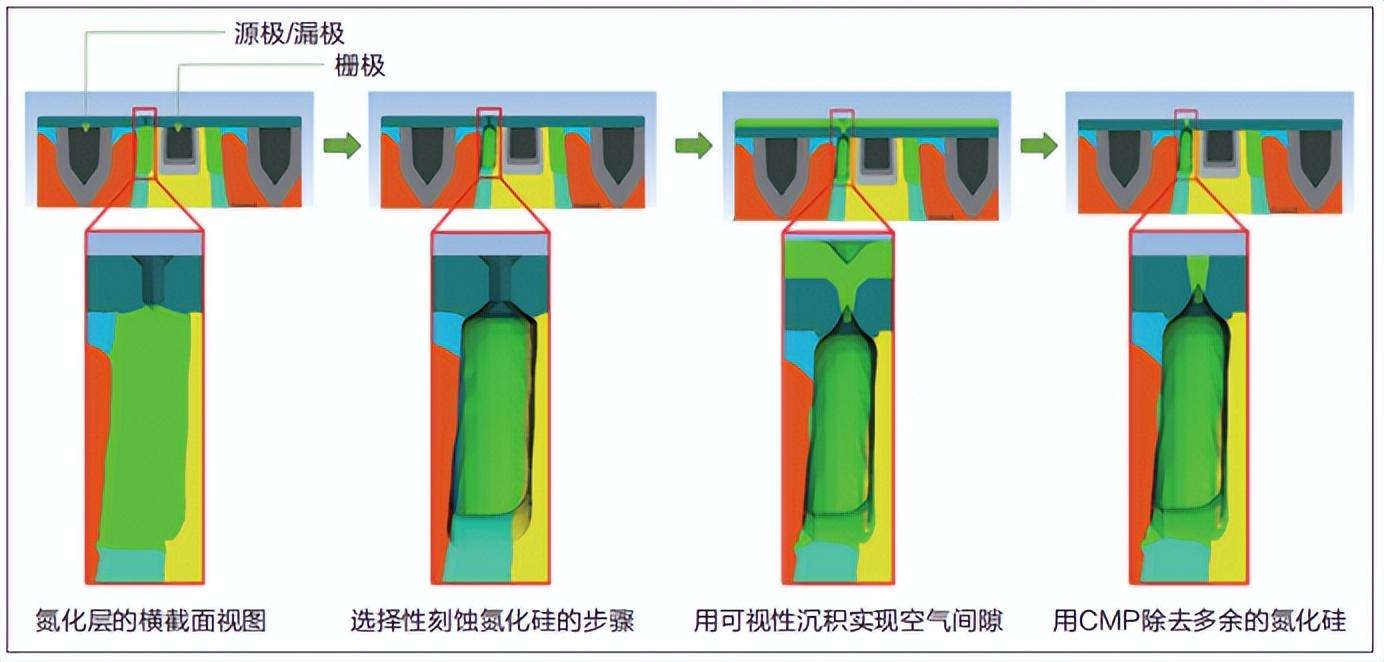

引入空氣間隙以減少前道工序中的寄生電容

可以減少器件的開關(guān)延遲。減少寄生電容的方法之一是設(shè)法降低柵極和源極/漏極之間材料層的有效介電常數(shù),這可以通過在該位置的介電材料中引入空氣間隙來實(shí)現(xiàn)。這種類型的方式過去已經(jīng)用于后道工序 (BEOL) 中,以減少金屬互連之間的電容 [1-4]。本文中,我們將專注于前道工序 (FEOL

2023-03-28 17:19:08 559

559

559

559

淺談PCB布線設(shè)計(jì)的重要參數(shù)

合理選擇PCB層數(shù)。用中間的電源層(vcc layer)和地層(Gnd layer)可以起到屏蔽作用,有效降低寄生電感和寄生電容,也可大大縮短布線的長(zhǎng)度,減少信號(hào)間的交叉干擾。

2023-04-05 06:51:00 386

386

386

386引入空氣間隙以減少前道工序中的寄生電容

和晶體管的源極/漏極接觸之間的寄生電容可以減少器件的開關(guān)延遲。減少寄生電容的方法之一是設(shè)法降低柵極和源極/漏極之間材料層的有效介電常數(shù),這可以通過在該位置的介電材料中引入空氣間隙來實(shí)現(xiàn)。這種類型的方式過去已經(jīng)用于后道工序(BEOL)中,以減少金屬互連之間的電容[1-4]。本文中,

2023-06-02 17:31:46 305

305

305

305

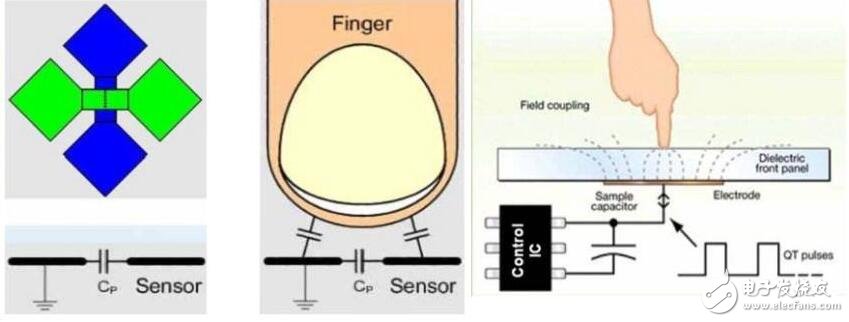

技術(shù)資訊 | 在高速設(shè)計(jì)中如何消除寄生電容?

本文要點(diǎn)寄生電容的定義寄生電容影響電路機(jī)理消除寄生電容的方法當(dāng)你想到寄生蟲時(shí),你可能會(huì)想到生物學(xué)上的定義——一種生活在宿主身上或在宿主體內(nèi)的有機(jī)體,從宿主身上吸取食物。從這個(gè)意義上說,寄生蟲可能是

2022-05-31 11:09:01 1730

1730

1730

1730

引入空氣間隙以減少前道工序中的寄生電容

使用Coventor SEMulator3D?創(chuàng)建可以預(yù)測(cè)寄生電容的機(jī)器學(xué)習(xí)模型

2023-07-06 17:27:02 187

187

187

187

PCB寄生電容的影響、計(jì)算公式和消除措施

寄生電容有一個(gè)通用的定義:寄生電容是存在于由絕緣體隔開的兩個(gè)導(dǎo)電結(jié)構(gòu)之間的虛擬電容(通常不需要的),是 PCB 布局中的一種效應(yīng),其中傳播的信號(hào)表現(xiàn)得好像就是電容,但其實(shí)并不是真正的電容。

2023-07-24 16:01:36 5431

5431

5431

5431

pcb連線寄生電容一般多少

電容可能會(huì)對(duì)電路的性能和穩(wěn)定性產(chǎn)生影響。因此,在 PCB 布線設(shè)計(jì)中,充分了解寄生電容的產(chǎn)生原因和處理方法是非常必要的。 什么是 PCB 連線寄生電容 維基百科上對(duì)于 PCB 連線寄生電容的定義是“由于 PCB 上信號(hào)線之間的相互耦合而導(dǎo)致的電容效應(yīng)”。

2023-08-27 16:19:44 1606

1606

1606

1606寄生電容對(duì)MOS管快速關(guān)斷的影響

寄生電容對(duì)MOS管快速關(guān)斷的影響 MOS(Metal Oxide Semiconductor)管是一種晶體管,它以其高性能和可靠性而廣泛應(yīng)用于許多電子設(shè)備,如功率放大器和開關(guān)電源。盡管MOS管具有

2023-09-17 10:46:58 1242

1242

1242

1242PCB的過孔該怎么做?PCB如何使用過孔?

在高速,高密度的PCB設(shè)計(jì)時(shí),設(shè)計(jì)者總是希望過孔越小越好,這樣板上可以留有更多的布線空間,此外,過孔越小,其自身的寄生電容也越小,更適合用于高速電路。

2023-10-19 12:37:15 1488

1488

1488

1488

SiC MOSFET 和Si MOSFET寄生電容在高頻電源中的損耗對(duì)比

SiC MOSFET 和Si MOSFET寄生電容在高頻電源中的損耗對(duì)比

2023-12-05 14:31:21 258

258

258

258

EMC計(jì)算方法和EMC仿真(1) ——計(jì)算方法簡(jiǎn)介

EMC計(jì)算方法和EMC仿真(1) ——計(jì)算方法簡(jiǎn)介

2023-12-05 14:56:08 383

383

383

383

詳解MOS管的寄生電感和寄生電容

寄生電容和寄生電感是指在電路中存在的非意圖的電容和電感元件。 它們通常是由于電路布局、線路長(zhǎng)度、器件之間的物理距離等因素引起的。

2024-02-21 09:45:35 245

245

245

245

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論