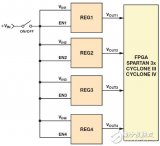

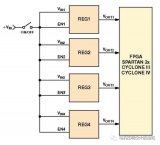

電源時序控制是微控制器、FPGA、DSP、 ADC和其他需要多個電壓軌供電的器件所必需的一項功能。##通過將衰減版本的調(diào)節(jié)器輸出端連接至待上電的下一個調(diào)節(jié)器使能引腳,可對多通道電源進行時序控制。

2014-08-05 10:15:54 3878

3878

電源時序控制是微控制器、FPGA、DSP、ADC和其他需要多個電壓軌供電的器件所必需的一項功能。##使用電阻分壓器簡化電源時序控制

2014-08-14 10:57:25 2414

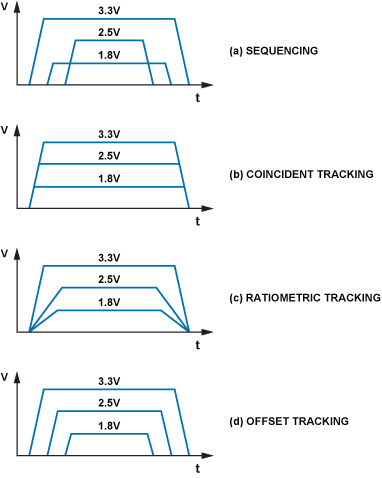

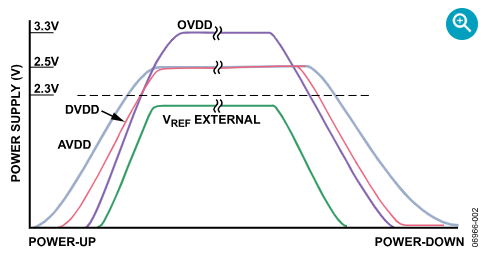

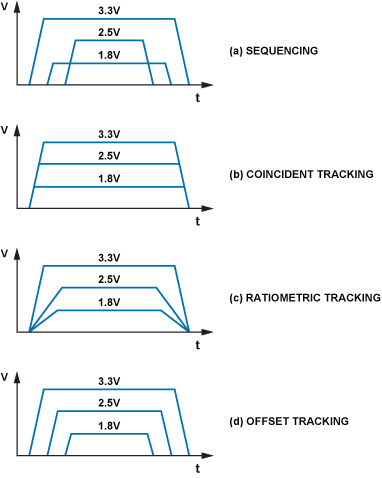

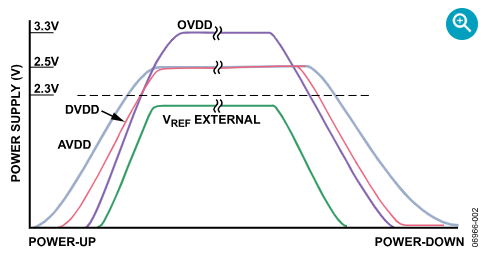

2414 本文討論如何針對FPGA或微處理器配置各種電壓輸出跟蹤和時序控制選項,來幫助實現(xiàn)靈敏多電源軌系統(tǒng)的正確啟動和關(guān)斷。

2015-07-22 17:30:27 1157

1157

表。 這4類路徑中,我們最為關(guān)心是②的同步時序路徑,也就是FPGA內(nèi)部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數(shù)據(jù)路徑和目的時鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 2767

2767

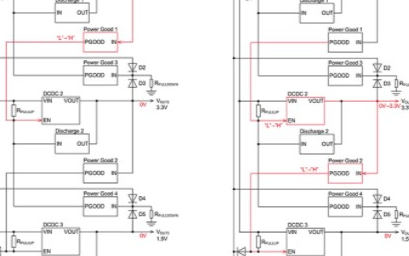

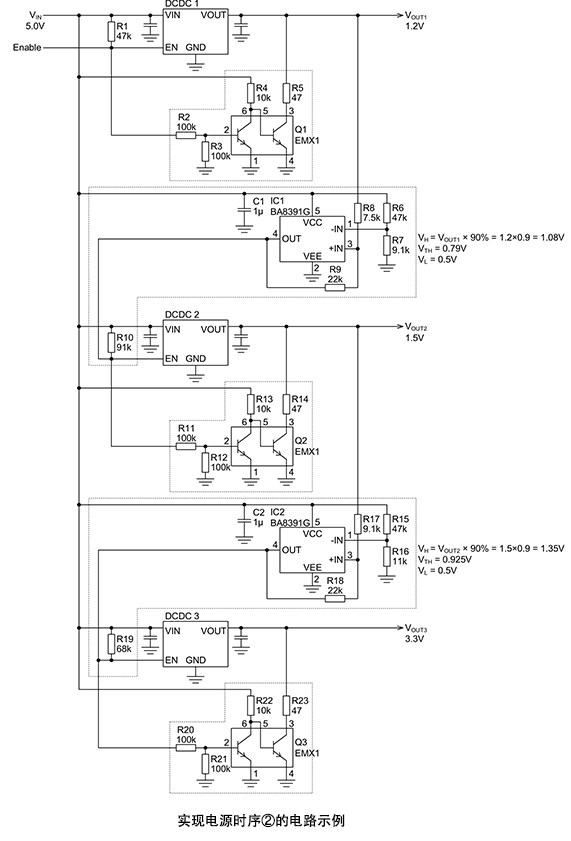

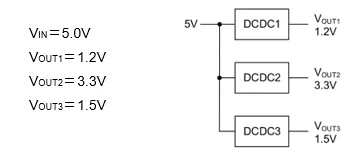

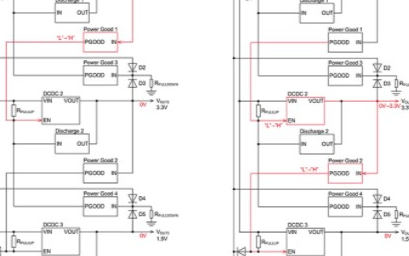

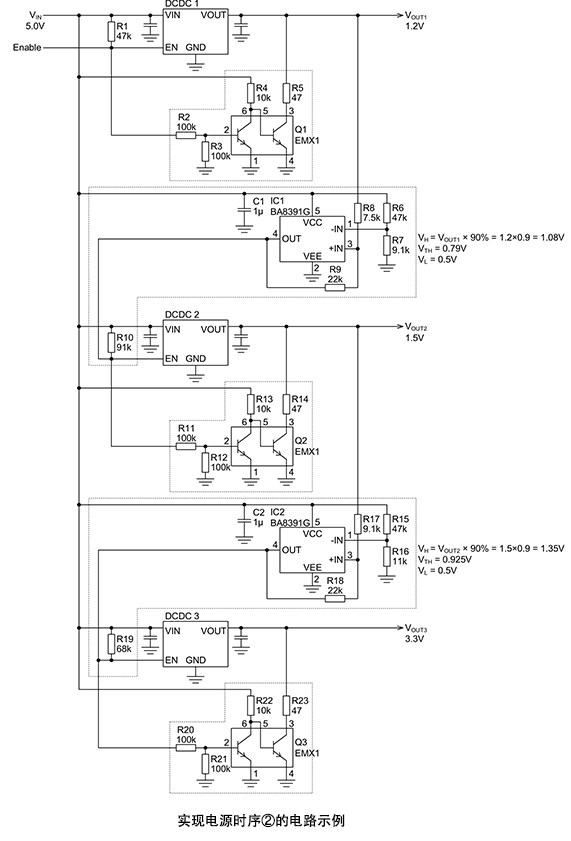

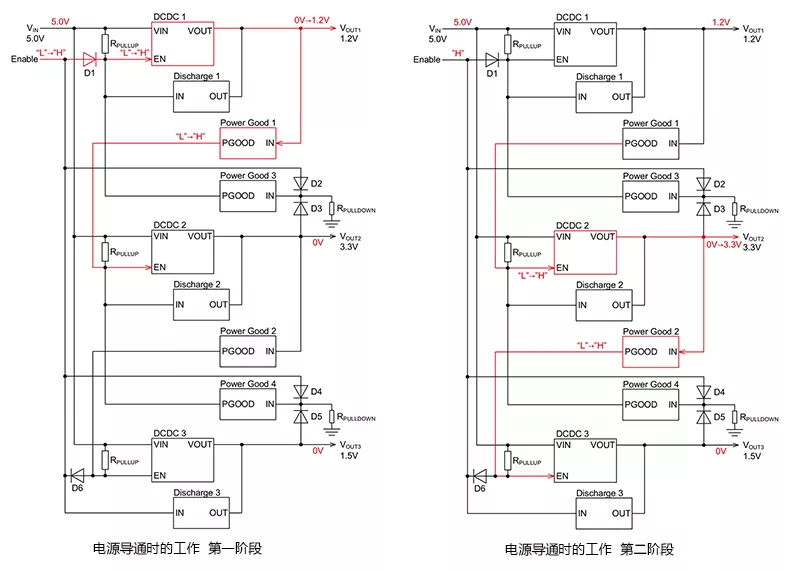

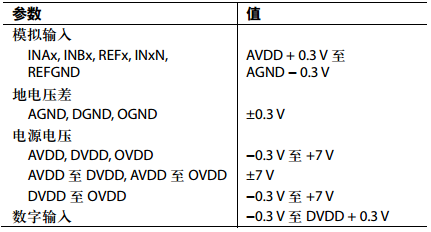

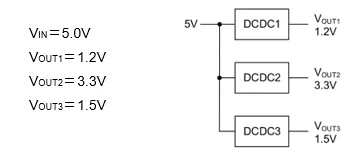

使用通用電源IC實現(xiàn)電源時序②的電路由DCDC IC×3、Power Good電路×2和放電電路×3組成。

2022-07-13 12:36:42 1302

1302 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

FPGA系統(tǒng)設(shè)計實質(zhì)上是一個同步時序系統(tǒng)的設(shè)計,理解時序概念,掌握代碼優(yōu)化與綜合技術(shù),正確完整地進行時序約束和分析是實現(xiàn)高性能系統(tǒng)的重要保證。很多同學在設(shè)計中都會碰到時序方面的問題,如何解決時序難題

2018-06-07 15:52:07

FPGA時序分析系統(tǒng)時序基礎(chǔ)理論對于系統(tǒng)設(shè)計工程師來說,時序問題在設(shè)計中是至關(guān)重要的,尤其是隨著時鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫窗口越來越小,要想在很短的時間限制里,讓數(shù)據(jù)信號從驅(qū)動端完整

2012-08-11 17:55:55

經(jīng)過兩天的惡補,特別是學習了《第五章_FPGA時 序收斂》及其相關(guān)的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據(jù)一些官方的文件對時序分析進行更系統(tǒng)、深入的學習。先總結(jié)一下之前

2011-09-23 10:26:01

。 在FPGA的最初布局和布線完成后,時序報告提供數(shù)據(jù)總線中每個時序的詳細延時信息。如果有必要,可為FPGA開發(fā)系統(tǒng)的關(guān)鍵信號設(shè)定延時路徑,TimingDesigner軟件可以提取相關(guān)信息和利用圖表更新

2017-09-01 10:28:10

fpga高手經(jīng)驗談doc文檔在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標志,在高層次設(shè)計方法中,對時序控制的抽象度也相應提高,因此在設(shè)計中較難把握,但在理解RTL電路時序模型的基礎(chǔ)上,采用合理

2012-08-11 11:30:39

多FPGA系統(tǒng)中自定義高速串行數(shù)據(jù)接口設(shè)計為方便多FPGA系統(tǒng)中主從FPGA之間的命令與數(shù)據(jù)傳輸,節(jié)省連接的引腳數(shù)量,設(shè)計了一種基于FPGA的自定義高速串行數(shù)據(jù)傳輸模塊。對主從串行模塊進行了詳盡

2012-08-11 11:49:57

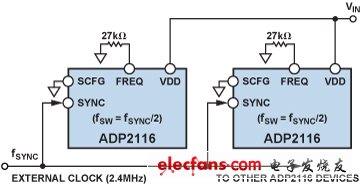

。圖6. 利用外部時鐘同步多個ADP2116結(jié)束語本文討論多電源系統(tǒng)的處理方法。時序控制器、監(jiān)控器、調(diào)節(jié)器和控制器具有非常高的功能集成度,便于設(shè)計工程師處理潛在的電源問題,而無需采用全部是分立IC

2018-10-19 10:36:04

原標題:控制電源啟動及關(guān)斷時序微處理器、FPGA、DSP、模數(shù)轉(zhuǎn)換器 (ADC) 和片上系統(tǒng) (SoC) 器件一般需要多個電壓軌才能運行。為防止出現(xiàn)鎖定、總線爭用問題和高涌流,設(shè)計人員需要按特定順序

2021-11-12 06:01:50

射頻(RF)和微波放大器在特定偏置條件下可提供最佳性能。偏置點所確定的靜態(tài)電流會影響線性度和效率等關(guān)健性能指標。雖然某些放大器是自偏置,但許多器件需要外部偏置并使用多個電源,這些電源的時序需要加以適當控制以使器件安全工作。接下來,我們主要來說說偏置時序控制要求。

2019-07-16 08:17:18

DN149-LTC1392監(jiān)控系統(tǒng)溫度和多電源電壓和電流

2019-05-31 10:07:47

HDUSec-網(wǎng)絡(luò)行為分析監(jiān)控系統(tǒng)[url=]是基于低功耗NetFPGA平臺設(shè)計開發(fā)的網(wǎng)絡(luò)行為分析監(jiān)控系統(tǒng)[/url]。本系統(tǒng)不僅能實現(xiàn)網(wǎng)絡(luò)行為的分析監(jiān)控,記錄用戶瀏覽網(wǎng)頁的信息,而且還能通過

2012-06-01 11:32:28

;航標燈其他系統(tǒng)參數(shù)檢測是否需要重啟等,程序流程如圖4所示。3 結(jié)束語介紹了一種基于Nios II軟核處理器的內(nèi)河航標監(jiān)控系統(tǒng)的設(shè)計,與傳統(tǒng)和限定的硬件組織和連接的控制系統(tǒng)方案相比,FPGA強大的邏輯

2015-01-30 11:05:50

或穩(wěn)壓器的時序和時間延遲(圖 4)。圖 4:LTC2937 最多可以控制六個電源時序,同時還可以監(jiān)控電源軌電壓。通過一根電線可以同步多個器件,最多可控制 300 個電源。(圖片來源:Analog

2019-07-30 10:43:06

了一種多通道視頻監(jiān)控系統(tǒng),通過對不同視頻通道穩(wěn)定、可靠地切換控制,實現(xiàn)監(jiān)控不同場景。該系統(tǒng)不僅彌補了傳統(tǒng)監(jiān)控視頻范圍有限的不足,而且提高了監(jiān)控資源的利用率,降低了監(jiān)控成本。

2019-06-24 07:39:08

采集、判斷、發(fā)送、告警、接收控制等功能;中心監(jiān)控器是系統(tǒng)的控制中心;傳輸網(wǎng)絡(luò)利用電信網(wǎng)的線路和交換設(shè)備。 監(jiān)控器是通信電源網(wǎng)絡(luò)監(jiān)控系統(tǒng)中最重要、最基本的組成單元,每個被監(jiān)控機房中須放置一臺。現(xiàn)場監(jiān)控

2011-11-11 17:27:51

對熱網(wǎng)終端用戶數(shù)據(jù)進行實時監(jiān)控,并具備報警、趨勢記錄、時時調(diào)峰、統(tǒng)計分析,遠程召測,故障點定位等多項功能。 項目實施效果實現(xiàn)熱網(wǎng)監(jiān)控調(diào)度中心與各換熱站的數(shù)據(jù)實時通訊控制,有效提高供熱系統(tǒng)的自動化控制水平

2019-12-05 15:35:14

DSP芯片組成并行處理系統(tǒng)。另外,為充分發(fā)揮 DSP芯片在復雜算法處理上的優(yōu)勢及FPGA在大數(shù)據(jù)量的底層算法上的優(yōu)勢,設(shè)計了一種基于FPGA控制的多DSP并行處理系統(tǒng)。1 系統(tǒng)設(shè)計基于FPGA控制的多

2019-05-21 05:00:19

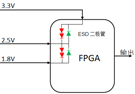

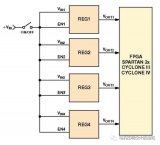

下載。一旦選擇了電源架構(gòu)和各個電壓轉(zhuǎn)換器,就需要選擇合適的無源元件來設(shè)計電源。做這件事時,需要牢記FPGA的特殊負載要求。它們分別是:各項電流需求電壓軌時序控制電壓軌單調(diào)上升快速電源瞬變電壓精度2各項

2019-05-05 08:00:00

實物測試結(jié)果圖。實測結(jié)果驗證了系統(tǒng)功能實現(xiàn)的正確性,PC端可循環(huán)發(fā)送命令,FPGA端接收并解析命令進行相應的控制(開關(guān)切換、信號采集等),然后將數(shù)據(jù)回饋到PC端,實現(xiàn)了多通道綜合測試系統(tǒng)的設(shè)計。圖 11

2018-08-07 10:08:19

什么是IBIS5-B-1300圖像傳感器?基于FPGA的CMOS控制時序該如何去設(shè)計?

2021-06-03 06:35:43

要求:該系統(tǒng)將圖像采集、顯示和存儲功能集成到FPGA平臺上,本設(shè)計采用NIOS II 設(shè)計軟核系統(tǒng),通過FPGA初始化圖像傳感器OV7670,OV7670再等待場同步,行同步,將采集的數(shù)據(jù)在TFT

2012-05-22 09:22:09

基于ARM和FPGA的智能小車監(jiān)控系統(tǒng)

2012-08-18 15:23:13

場景進行監(jiān)控,不僅視頻的視野范圍有限,而且不能對同一個物體的不同方位進行監(jiān)控。這里提出了一種多通道視頻監(jiān)控系統(tǒng),通過對不同視頻通道穩(wěn)定、可靠地切換控制,實現(xiàn)監(jiān)控不同場景。該系統(tǒng)不僅彌補了傳統(tǒng)監(jiān)控視頻范圍

2012-12-12 17:00:21

、告警的查詢分析和統(tǒng)計等功能。通信電源設(shè)備運行參數(shù)多,實時效果強,所以在監(jiān)控系統(tǒng)當中選擇功能強大的控制芯片,應用嵌入式操作系統(tǒng),采用嵌入式軟件開發(fā)技術(shù)使其盡可能地發(fā)揮出強大的控制管理功能是當前通信電源

2019-06-20 06:32:31

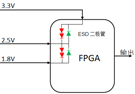

簡介 電源時序控制是微控制器、FPGA、DSP、ADC和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數(shù)字I/O軌上電前對內(nèi)核和模擬模塊上電,但有些設(shè)計可能需要采用其他序列

2018-09-30 16:01:35

本系統(tǒng)立足于利用Intemet實現(xiàn)核環(huán)境信息的遠程采集。告訴大家,如何利用FPGA和嵌入式系統(tǒng)設(shè)計遠程監(jiān)控系統(tǒng)?實現(xiàn)利用互聯(lián)網(wǎng)進行信息的傳輸。

2019-08-02 08:07:36

如何在視頻監(jiān)控系統(tǒng)中使用FPGA進行視頻處理?

2021-06-07 06:12:39

多電源系統(tǒng)的處理方法

2021-03-16 13:09:33

片上系統(tǒng)(SoC) IC的廣泛使用,對電源進行時序控制和管理變得越來越重要,今天我們來談一下這個問題?歡迎大家留言一起交流

2019-11-12 10:07:54

如何有效的管理FPGA設(shè)計中的時序問題當FPGA設(shè)計面臨到高級接口的設(shè)計問題時,EMA的TimingDesigner可以簡化這些設(shè)計問題,并提供對幾乎所有接口的預先精確控制。從簡單SRAM接口到高速

2009-04-14 17:03:52

形式進行采集和存儲,便于壓縮,分析,處理和顯示,抗干擾能力強,適合網(wǎng)絡(luò)傳輸。因此,數(shù)字化是視頻監(jiān)控系統(tǒng)的發(fā)展方向。傳統(tǒng)的視頻處理系統(tǒng)為了滿足實時性和靈活的實際接口需要,多采用FPGA+ DSP或者

2019-08-02 06:18:40

進行監(jiān)控。當所有電壓建立之后,時序控制器電路產(chǎn)生電源良好信號。模擬時序控制解決方案(如ADM1186-1)很容易使用。它們具備多電壓系統(tǒng)所需的全部功能。模擬時序控制器與數(shù)字時序控制器的不同之處在于,前者

2021-04-12 07:00:00

信息。”從而在國家標準層面上規(guī)定了消控室中需裝設(shè)消防設(shè)備電源監(jiān)控系統(tǒng),作為消防系統(tǒng)中的一種預警系統(tǒng)。而另一個關(guān)于該系統(tǒng)的產(chǎn)品標準GB 28184-2011《消防設(shè)備電源監(jiān)控系統(tǒng)》也應運而生,使得消防設(shè)備電源監(jiān)控系統(tǒng)有了相應的產(chǎn)品檢測依據(jù)。

2020-05-11 06:33:15

引言 電源時序控制是微控制器、FPGA、DSP、 ADC和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數(shù)字I/O軌上電前對內(nèi)核和模擬模塊上電,但有些設(shè)計可能需要采用其他序列

2019-07-03 08:15:19

1. FPGA時序的基本概念FPGA器件的需求取決于系統(tǒng)和上下游(upstream and downstrem)設(shè)備。我們的設(shè)計需要和其他的devices進行數(shù)據(jù)的交互,其他的devices可能是

2019-07-09 09:14:48

請問怎么用fpga驅(qū)動w5300?諸如初始化,時序控制等,能不能提供下示例代碼?謝謝!!

2018-06-04 17:31:21

: |---500ms--|---50ms--|請問如何挑選電源監(jiān)控芯片來滿足該時序,希望芯片體積盡量小,電路盡量簡單,有何芯片可推薦?

2019-04-24 13:35:49

Jess Espiritu簡介電源時序控制是微控制器、FPGA、DSP、ADC 和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數(shù)字 I/O 軌上電前對內(nèi)核和模擬模塊上電,但有

2018-10-23 14:30:34

基于LabVIEW的多功能監(jiān)控界面設(shè)計方案。此監(jiān)控界面有處理數(shù)據(jù)類型多、存儲數(shù)據(jù)量大、界面具備人性化等特點。 1 光伏電源監(jiān)控系統(tǒng) 光伏電源監(jiān)控系統(tǒng)可分為以下模塊:光伏電源數(shù)據(jù)采集與控制(DSP28035

2019-04-08 09:40:07

ADM1260 Super Sequencer?超級時序控制器是一款可配置電源監(jiān)控/時序控制器件,可針對多電源系統(tǒng)中的電源監(jiān)控和時序控制提供一種單芯片解決方案。高速片間總線(ICB)可輕松將多個器件

2023-04-03 09:28:56

ADM1068 Super Sequencer?超級時序控制器是一款可配置電源監(jiān)控/時序控制器件 , 可針對多電源系統(tǒng)中的電源監(jiān)控和時序控制提供一種單芯片解決方案。 該

2023-04-03 15:22:34

FPGA重要設(shè)計思想及工程應用之時序及同

在FPGA設(shè)計中最好的時鐘方案 是: 由專用的全局時鐘輸入引腳 動單個 主時鐘去控制設(shè)計項目中的每一個觸發(fā) 器

2010-02-09 10:29:36 51

51 時序電源控制器是本公司生產(chǎn)的具有自動按時間次序開關(guān)的電源控制切換設(shè)備。當操作員發(fā)出電源開的觸發(fā)控制命令時,控制器將按時間次序順序打開1至8路電源;當操作員發(fā)出電源

2010-10-28 00:56:39 63

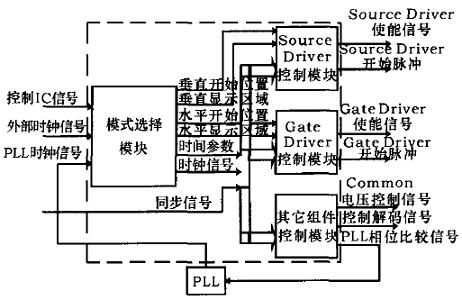

63 TFT-LCD系統(tǒng)時序控制模塊的設(shè)計

摘要:說明時序控制模塊和LCD系統(tǒng)中其它子模塊之間的關(guān)系,對時序控制模塊所要解決的時序問題進行分析。在分析問題的基礎(chǔ)上提出一種適

2008-01-16 09:54:18 4354

4354

如何有效的管理FPGA設(shè)計中的時序問題

當FPGA設(shè)計面臨到高級接口的設(shè)計問題時,EMA的TimingDesigner可以簡化這些設(shè)計問題,并提供對幾乎所有接口的預先精確控制。從簡單

2009-04-15 14:19:31 659

659

為了提高系統(tǒng)的監(jiān)控能力降低成本,提出了一種基于CMOS的多通道 視頻監(jiān)控 方案。首先基于同步信號控制各路視頻同步,保證圖像質(zhì)量。在此基礎(chǔ)上由DSP和FPGA產(chǎn)生控制切換信號,控制多

2011-08-05 15:20:33 74

74 現(xiàn)今,電子系統(tǒng)往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統(tǒng)中,尤其如此。為實現(xiàn)可靠、可重復的操作,必須監(jiān)控各電源電壓的開關(guān)時序、上升和下降

2012-10-22 17:05:14 1495

1495

當你的FPGA設(shè)計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設(shè)計從而滿足時序要求,也需要設(shè)計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1168

1168 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 基于時序路徑的FPGA時序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設(shè)計中的時序問題

2017-01-14 12:49:02 14

14 當你的FPGA設(shè)計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設(shè)計從而滿足時序要求,也需要設(shè)計者具有明確目標和診斷/隔離時序問題的能力。設(shè)計者現(xiàn)在有一些

2017-02-09 01:59:11 264

264 fpga時序收斂

2017-03-01 13:13:34 23

23 基于FPGA的新型公交監(jiān)控系統(tǒng)設(shè)計_劉智

2017-03-19 11:38:26 3

3 一個好的FPGA設(shè)計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設(shè)計中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現(xiàn)時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

現(xiàn)有的工具和技術(shù)可幫助您有效地實現(xiàn)時序性能目標。當您的FPGA 設(shè)計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現(xiàn)工具為滿足時序要求而優(yōu)化設(shè)計的能力,還取決于設(shè)計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2950

2950 FPGA設(shè)計一個很重要的設(shè)計是時序設(shè)計,而時序設(shè)計的實質(zhì)就是滿足每一個觸發(fā)器的建立(Setup)/保持(Hold)時間的要求。

2018-06-05 01:43:00 4150

4150

數(shù)據(jù)采集系統(tǒng)的總體架構(gòu)如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內(nèi)部實現(xiàn)。為實現(xiàn)多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態(tài)機控制下,完成模擬信號經(jīng)過

2018-08-28 10:16:07 12734

12734

現(xiàn)今,電子系統(tǒng)往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統(tǒng)中,尤其如此。為實現(xiàn)可靠、可重復的操作,必須監(jiān)控各電源電壓的開關(guān)時序、上升和下降速率、加電順序以及

2019-04-09 08:14:00 3558

3558

電源時序控制是微控制器、FPGA、DSP、ADC 和其他需要多個電壓軌供電的器件所必需的一項功能。

2019-06-21 15:44:53 3070

3070

微處理器、FPGA、DSP、模數(shù)轉(zhuǎn)換器 (ADC) 和片上系統(tǒng) (SoC) 器件一般需要多個電壓軌才能運行。為防止出現(xiàn)鎖定、總線爭用問題和高涌流,設(shè)計人員需要按特定順序啟動和關(guān)斷這些電源軌。此過程稱為電源時序控制或電源定序,目前有許多解決方案可以有效實現(xiàn)定序。

2019-09-15 09:22:00 647

647

電源時序器是用于控制用電設(shè)備的開啟/關(guān)閉的時序器,是各類音響工程、電視廣播系統(tǒng)、電腦網(wǎng)絡(luò)系統(tǒng)及其它電氣工程不可缺少的設(shè)備之一。

2019-12-20 09:00:03 9295

9295 現(xiàn)今,電子系統(tǒng)往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA 的系統(tǒng)中,尤其如此。為實現(xiàn)可靠、可重復的操作,必須監(jiān)控各電源電壓的開關(guān)時序、上升和下降速率、加電順序以及幅度。既定的電源系統(tǒng)設(shè)計可能包括電源時序控制、電源跟蹤、電源電壓 / 電流監(jiān)控和控制。

2020-12-30 00:26:00 12

12 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 作者:Jess Espiritu

簡介

電源時序控制是微控制器、FPGA、DSP、ADC 和其他需要多個電壓軌供電的器件所必需的一項功能。這些應用通常需要在數(shù)字 I/O 軌上電前對內(nèi)核和模擬模塊

2021-01-20 16:13:39 8

8 AN-932: 電源時序控制

2021-03-21 14:22:11 8

8 AN-781: 利用ADM1062–ADM1069 Super SequencersTM超級時序控制器監(jiān)控額外電源

2021-03-21 17:43:32 12

12 面向脈沖功率電源模塊的時序放電控制系統(tǒng)

2021-07-05 14:14:53 11

11 原標題:控制電源啟動及關(guān)斷時序微處理器、FPGA、DSP、模數(shù)轉(zhuǎn)換器 (ADC) 和片上系統(tǒng) (SoC) 器件一般需要多個電壓軌才能運行。為防止出現(xiàn)鎖定、總線爭用問題和高涌流,設(shè)計人員需要按特定順序

2021-11-07 18:37:03 10

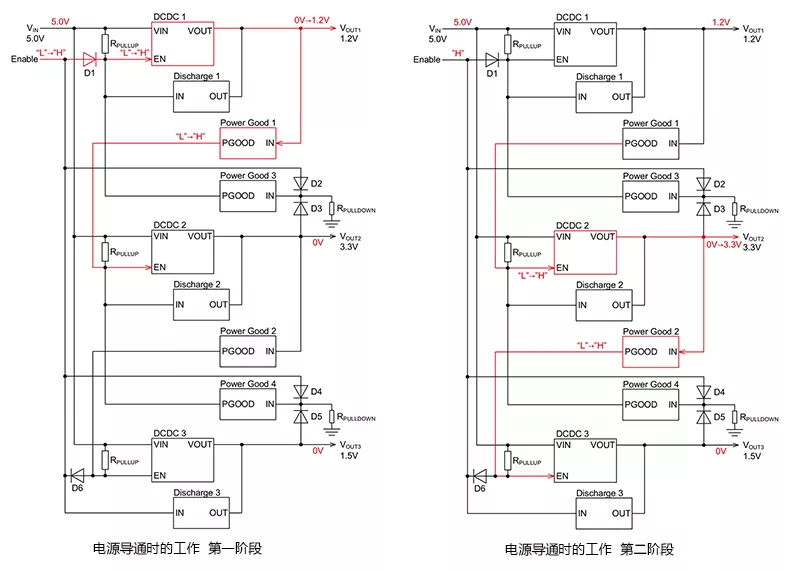

10 上一篇文章中介紹了使用通用電源IC實現(xiàn)電源時序控制電路的“電源時序規(guī)格①”的控制電路。本文先介紹使用通用電源IC實現(xiàn)電源時序控制電路中,電源導通時的時序工作。

2022-01-18 14:50:21 4422

4422

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 本文章探討一下FPGA的時序input delay約束,本文章內(nèi)容,來源于明德?lián)P時序約束專題課視頻。

2022-07-25 15:37:07 2379

2379

如何使用TI電源時序控制器在5G MIMO的應用

2022-10-31 08:23:58 0

0 “使用通用電源IC實現(xiàn)電源時序控制的電路”系列文章已經(jīng)發(fā)表了11篇,本文是使用通用電源IC實現(xiàn)電源時序控制的電路的最后一篇。

2023-02-23 10:40:58 900

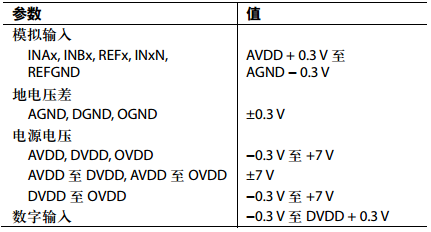

900 隨著集成電路(IC)時代的到來,許多功能模塊被集成到一個IC中,因而需要利用多個電源為這些模塊供電。這些電源的電壓有時候相同,但更多時候是不同的。市場上的片上系統(tǒng)(SoC) IC越來越多,這就產(chǎn)生了對電源進行時序控制和管理的需求

2023-06-16 16:34:03 436

436

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

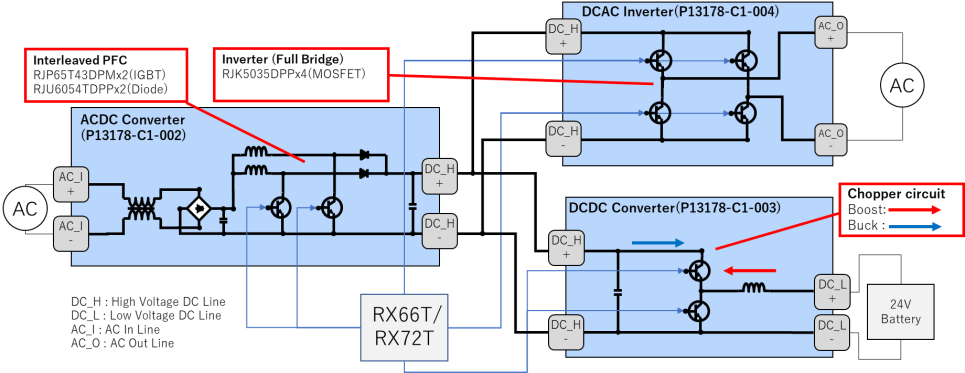

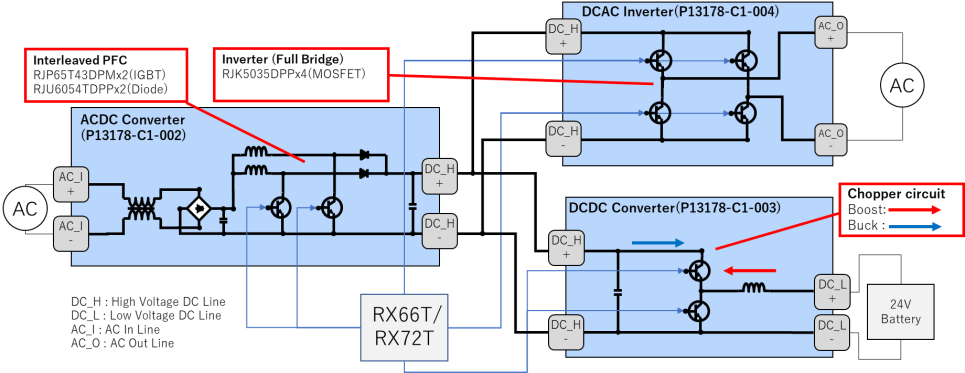

3 使用RX單片機實現(xiàn)數(shù)字電源控制的示例

2023-09-27 15:20:44 363

363

器是一種電子設(shè)備,它的作用是控制多個電源單元間的開啟和關(guān)閉時序,從而保證系統(tǒng)的穩(wěn)定性和可靠性。電源時序器通常由微控制器或者FPGA實現(xiàn),可以根據(jù)用戶需要編寫相應的程序控制電源單元的開啟和關(guān)閉時序。電源時序器通常被

2023-10-16 16:16:27 1857

1857 電子發(fā)燒友網(wǎng)站提供《多電源系統(tǒng)監(jiān)控和時序控制介紹.pdf》資料免費下載

2023-11-22 16:04:24 0

0 電子發(fā)燒友網(wǎng)站提供《電源的時序控制.pdf》資料免費下載

2023-11-23 14:30:44 4

4 電源時序規(guī)格②:電路和常數(shù)計算示例

2023-12-05 11:32:47 190

190

電源時序規(guī)格:電源導通時的時序工作

2023-12-08 18:21:43 326

326

電源時序控制的正確方法,你掌握了嗎?

2023-12-15 09:27:10 579

579

電源時序規(guī)格及控制框圖

2023-12-15 09:31:51 248

248

電子發(fā)燒友App

電子發(fā)燒友App

評論