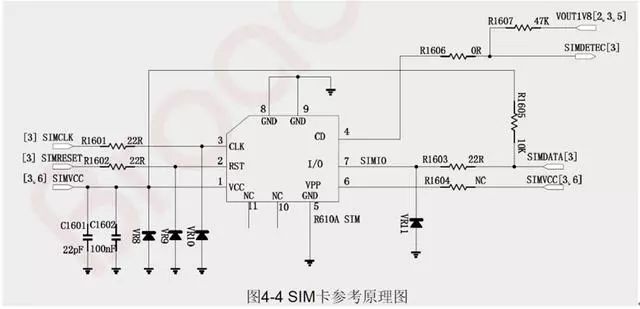

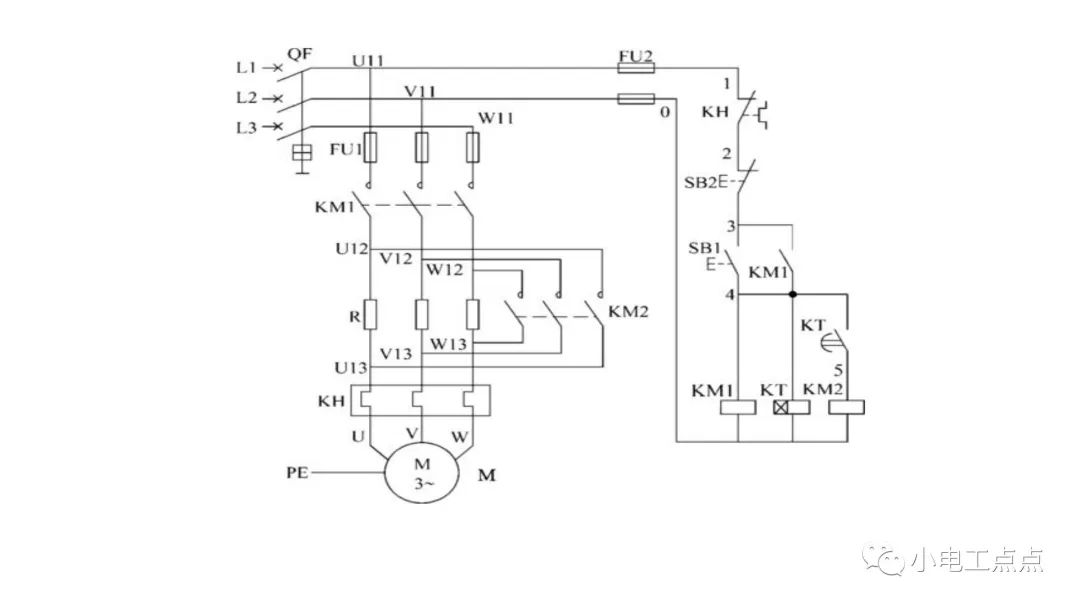

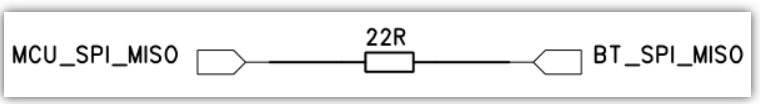

我們在看原理圖時,經常看到串一些小電阻,如22歐姆,但有時也不是一定要串。

同樣的應用中,有的串電阻,有的不串。這是什么原因?如果是高速信號線上串小電阻,那就應該是終端阻抗匹配。

簡單的例子:一個串口通訊的提示信號,當接上串口時,因為瞬間的插拔產生了一個很窄的電壓脈沖,如果這個脈沖直接打到GPIO口,很可能打壞芯片,但是串了一個小電阻,很容易把能力給消耗掉。如果脈沖是5mA 5.1V,那么過了30ohm后就是5v左右了。

高速信號線中才考慮使用這樣的電阻。在低頻情況下,一般是直接連接。這個電阻一般有有兩個作用,第一是阻抗匹配。

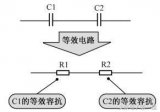

因為信號源的阻抗很低,跟信號線之間阻抗不匹配,串上一個電阻后,可改善匹配情況,以減少反射。第二是可以減少信號邊沿的陡峭程度,從而減少高頻噪聲以及過沖等。因為串聯電阻,和信號線的分布電容以及負載的輸入電容會形成一個RC等效濾波電路,這樣就會降低信號邊沿的陡峭程度。

學過高速信號理論的都應該知道,如果高速傳輸信號的邊沿很陡峭,其中就會含有大量的高頻成分,將會造成輻射干擾,另外,也容易產生過沖。

在SIM卡電路中,其實不加這個電阻也是不會影響SIM卡正常工作的。這個電阻主要是因為終端入網需要做SIM卡接口測試。SIM卡接口測試最容易出的問題就是CLK信號線上面過沖偏大。

增加小電阻可以消弱過沖。其實不一定要33R,換成47R,100R也都OK的。SIM卡的CLK頻率不會太高,一般不用串電阻來防止對外輻射影響其他信號,所以SIM卡CLK信號在LAYOUT時也沒有要求四面包地處理。

另外串聯小電阻可以增強ESD防護作用,TVS一般是利用瞬間導通釋放靜電來防護的,在TVS后面加小電阻可以起到“堵”的作用,當靜電夠猛的時候,有時候TVS還不能起到防護作用,而串聯的小電阻像是一面墻,將靜電堵住。

敏感信號線上面采用TVS加串聯小電阻的方式做ESD防護效果還不錯,深受各工程師喜愛。

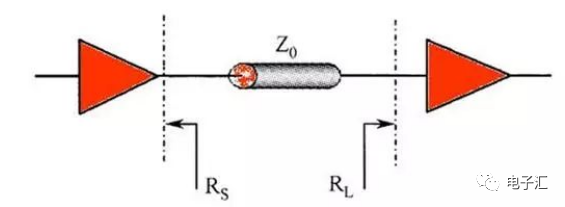

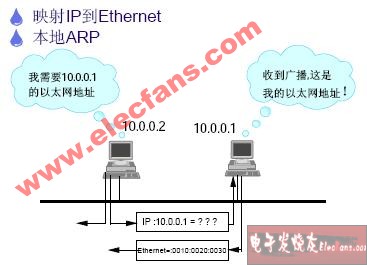

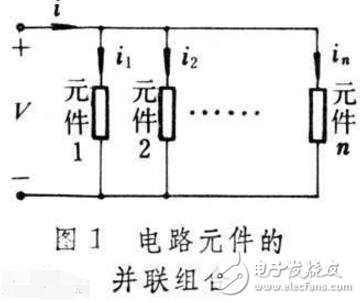

信號源內阻與所接傳輸線的特性阻抗大小相等且相位相同,或傳輸線的特性阻抗與所接負載阻抗的大小相等且相位相同,分別稱為傳輸線的輸入端或輸出端處于阻抗匹配狀態,簡稱為阻抗匹配。

否則,便稱為阻抗失配。阻抗匹配impedance matching)是指信號源或者傳輸線跟負載之間的一種合適的搭配方式,主要用于傳輸線上,以此來達到所有高頻信號無損耗傳遞至負載的目的。

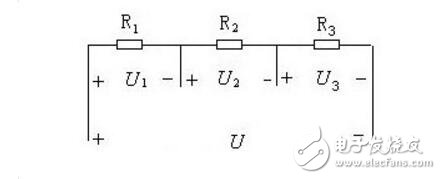

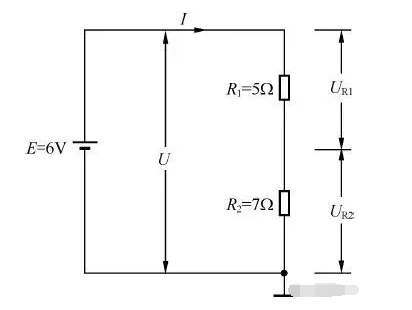

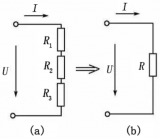

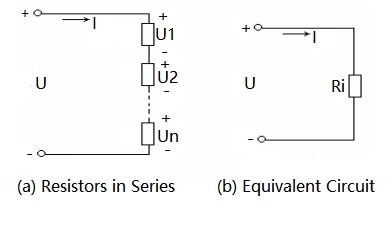

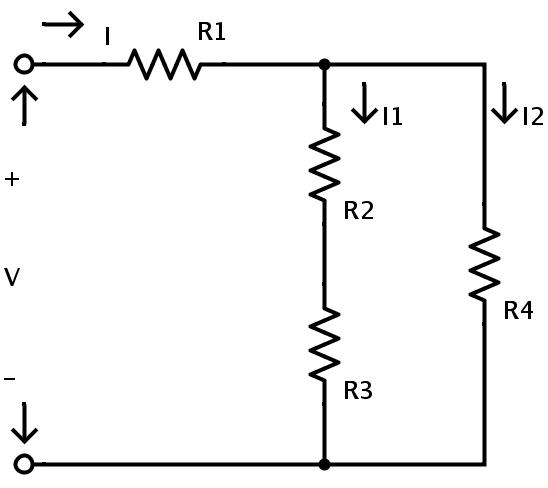

先從直流電壓源驅動一個負載入手。任何實際的電壓源,都是有等效內阻的,所以我們可以把一個實際電壓源,等效成一個理想的電壓源跟一個電阻r串聯的模型。

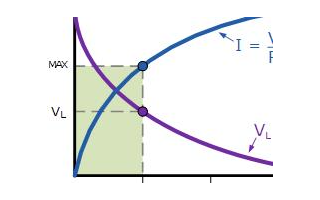

假設負載電阻為R,電源電動勢為U,內阻為r,那么我們可以計算出流經電阻R的電流為:I=U/(R+r),可以看出,負載電阻R越小,則輸出電流越大。

負載R上的電壓為:Uo=IR=U/[1+(r/R)]。

可以看出,負載電阻R越大,則輸出電壓Uo越高。最后再來計算一下電阻R消耗的功率為:

P = I2×R=[U/(R+r)]2×R = U2×R/(R2+2×R×r+r2)

= U2×R/[(R-r)2+4×R×r]

= U2/{[(R-r)2/R]+4×r}

對于一個給定的信號源,其內阻r是固定的,而負載電阻R則是可選擇的。

我們可以看到式中[(R-r)2/R],當R=r時,[(R-r)2/R]可取得最小值0,這時負載電阻R上可獲得最大的輸出功率Pmax=U2/(4×r)。

即,當負載電阻跟信號源內阻相等時,負載可獲得最大的輸出功率,這就是我們常說的阻抗匹配。

當交流電路中含有容性或感性阻抗時,結論有所改變,就是需要信號源與負載阻抗的的實部相等,虛部互為相反數,這叫做共扼匹配。

在低頻電路中,我們一般不考慮傳輸線的匹配問題,只考慮信號源跟負載之間的情況,因為低頻信號的波長相對于傳輸線來說很長,傳輸線可以看成是“短線”,反射可以不考慮(可以這么理解:因為線短,即使反射回來,跟原信號還是一樣的)。

從以上分析我們可以得出結論:如果我們需要輸出電流大,則選擇小的負載R;如果我們需要輸出電壓大,則選擇大的負載R;如果我們需要輸出功率最大,則選擇跟信號源內阻匹配的電阻R。

在高頻電路中,我們還需要考慮反射的問題。當信號的頻率很高時,則信號的波長就很短,當波長短得跟傳輸線長度可以比擬時,反射信號就會疊加在原信號上,從而會改變原信號的形狀。

如果傳輸線的特征阻抗跟負載阻抗不相等(即不匹配)時,那么在負載端就會產生反射。為什么阻抗不匹配時會產生反射以及特征阻抗的求解方法,牽涉到二階偏微分方程的求解,在這里我們不細說了,有興趣的可參考電磁場與電磁波方面書籍中的傳輸線理論。

在這里需要強調一點的是,特性阻抗跟我們通常理解的電阻不是一個概念,它與傳輸線的長度無關,也不能通過使用歐姆表來測量。

為了不產生反射,負載阻抗跟傳輸線的特征阻抗應該相等,這就是傳輸線的阻抗匹配。如果阻抗不匹配會有什么不良后果呢?

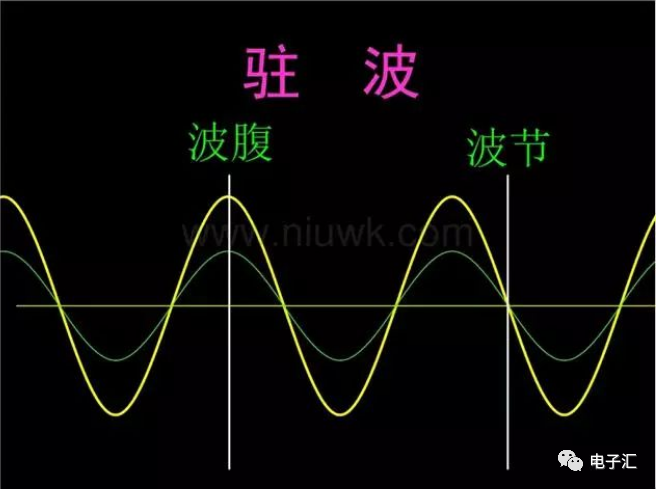

如果不匹配,則會形成反射,造成能量不能完全傳遞過去,導致功耗增加、效率降低;會在傳輸線上形成駐波(頻率相同、傳輸方向相反的兩種波。

簡單點說,就是有些地方信號強,有些地方信號弱),從而導致傳輸線的有效功率容量降低;功率發射不出去,甚至會損壞發射設備。

如果是電路板上的高速信號線與負載阻抗不匹配時,會產生震蕩,輻射干擾,EMC等等。

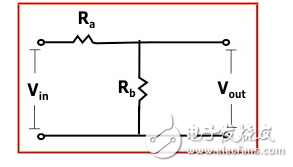

當阻抗不匹配時,有哪些辦法讓它匹配呢?第一,我們可以考慮使用串聯/并聯電容或電感的辦法,這也是在射頻調試時常用手段。第二,可以考慮使用串聯/并聯電阻的辦法。

一些驅動器的阻抗比較低,可以串聯一個合適的電阻來跟傳輸線匹配,例如高速信號線,有時會串聯一個幾十歐姆到二三十歐姆的電阻。而一些接收器的輸入阻抗則比較高,可以使用并聯電阻的方法,來跟傳輸線匹配。

例如,485總線接收器,常在數據線終端并聯120歐的匹配電阻。

為了幫助大家理解阻抗不匹配時的反射問題,舉兩個例子:假設你在練習拳擊—打沙包。如果是一個重量合適的、硬度合適的沙包,你打上去會感覺很舒服。但是,如果哪一天我把沙包做了手腳,例如,里面換成了鐵沙,你還是用以前的力打上去,你的手可能就會受不了了。

這就是負載過重的情況,會產生很大的反彈力。相反,如果我把里面換成了很輕很輕的東西,你一出拳,則可能會撲空,手也可能會受不了——這就是負載過輕的情況。

淺談四層板和22歐電阻

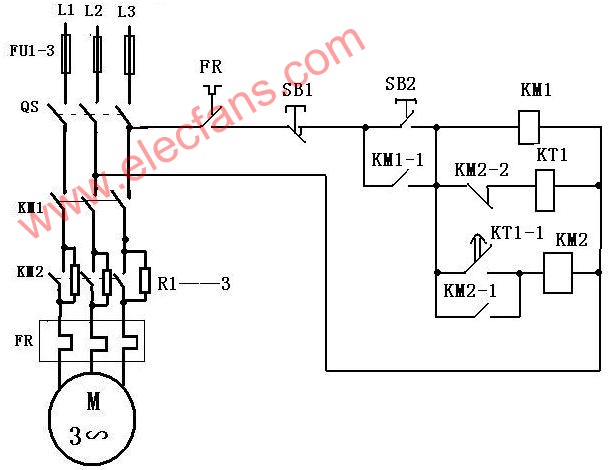

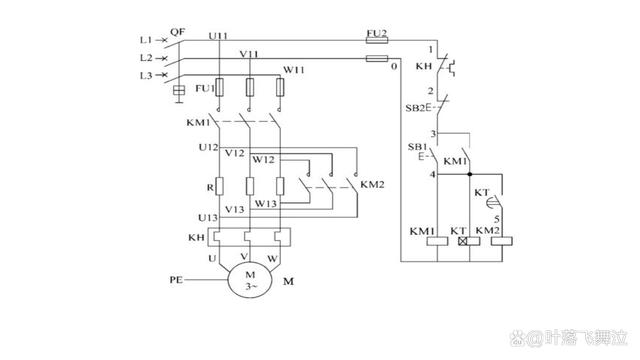

選用四層板不僅是電源和地的問題,高速數字電路對走線的阻抗有要求,二層板不好控制阻抗,22歐電阻一般加在驅動器端,也是起阻抗匹配作用的。布線時要優先布數據、地址線,和需要保證的高速線。

在高頻的時候,PCB板上的走線都要看成傳輸線,傳輸線是有其特征阻抗的,學過傳輸線理論的都應該知道,當傳輸線上某處出現阻抗突變(不匹配)時,信號通過就會發生反射,反射對原信號造成干擾,嚴重時就會影響電路的正常工作。

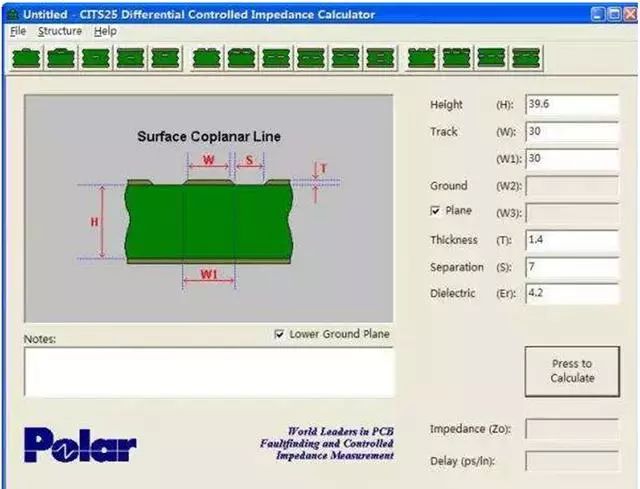

采用四層板時,通常外層走信號線,中間兩層分別為電源和地平面,這樣一方面隔離了兩個信號層,更重要的是外層的走線與它們所靠近的平面形成稱為“微帶”(microstrip) 的傳輸線,它的阻抗比較固定,而且可以計算,而對于兩層板就比較難以做到這樣效果。

傳輸線阻抗主要與走線的寬度、阻抗線到參考平面的距離、敷銅的厚度以及介電材料的特性有關,有許多現成的公式和工具可供計算。

22歐電阻通常串連放在驅動的一端(其實不一定22歐,從幾歐到五、六十歐都有,視具體電路而定) ,其作用是與發送器的輸出阻抗串連后與走線的阻抗匹配,使反射回來(假設解收端阻抗沒有匹配) 的信號不會再次反射回去(吸收掉),這樣接收端的信號就不會受到影響接收端也可以作匹配。

這里所說的高頻,不一定是時鐘頻率很高的電路,是不是高頻不止看頻率,更重要是看信號的上升下降時間通常可以用上升(或下降) 時間估計電路的頻率。

一般取上升時間倒數的一半,比如如果上升時間是1ns,那么它的倒數是1000MHz,也就是說在設計電路是要按500MHz的頻帶來考慮有時候要故意減慢邊緣時間,許多高速IC其驅動器的輸出斜率都是可調的。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論