電子發(fā)燒友網(wǎng)站提供《基于FPGA的PCI硬件加解密卡的設(shè)計(jì)方案.pdf》資料免費(fèi)下載

2023-10-18 11:18:03 0

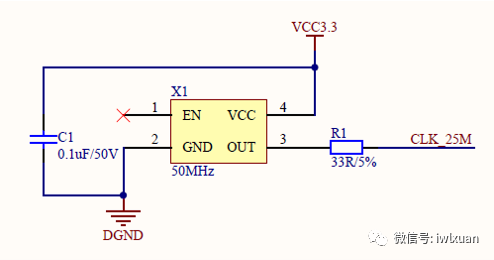

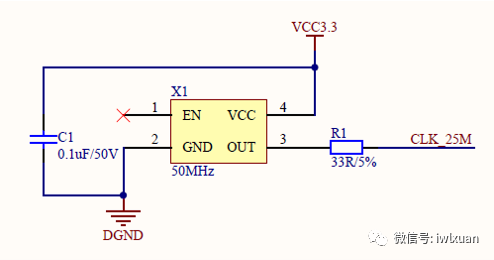

0 小編在本節(jié)介紹FPGA芯片外圍電路設(shè)計(jì)規(guī)范和配置過程,篇幅比較大,時(shí)鐘的設(shè)計(jì)原則就有17條,伙伴們耐心讀一讀。

2023-08-15 16:18:11 1405

1405

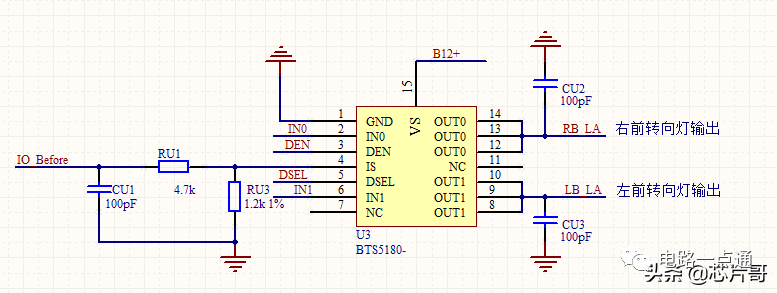

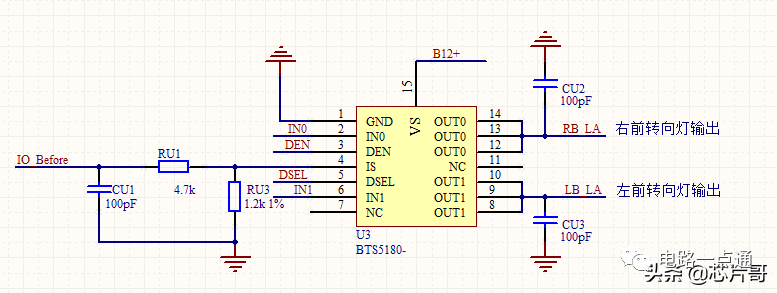

汽車日趨平民化,已被越來越多的家庭選為自己的代步工具;行車安全引起了社會(huì)廣泛的關(guān)注每當(dāng)我們駕駛汽車行駛路口,在左轉(zhuǎn)彎或者右轉(zhuǎn)彎的時(shí)候需要打方向燈,常常聽到“滴答滴答”的聲音;作為硬件研發(fā)工程師,電路一點(diǎn)通帶領(lǐng)小伙伴們一起去研究下這個(gè)汽車大燈的硬件電路設(shè)計(jì)方案,讓我們對汽車有更充分的了解與認(rèn)識。

2023-06-19 09:16:12 1015

1015

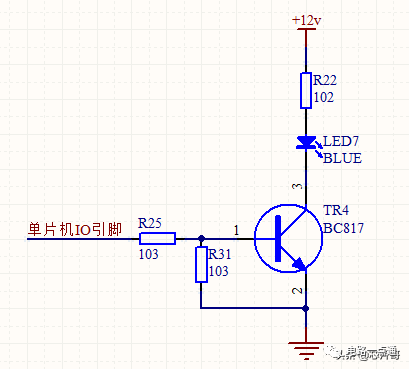

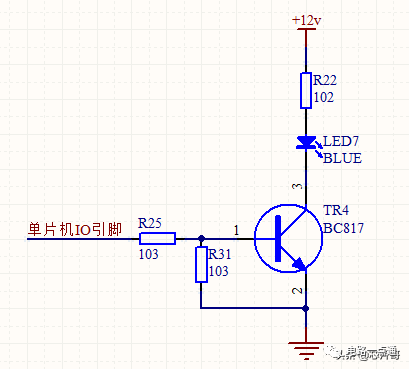

硬件研發(fā)工程師,在項(xiàng)目開發(fā)的時(shí)候,或多或少會(huì)遇到LED驅(qū)動(dòng)的電路設(shè)計(jì)問題;針對LED驅(qū)動(dòng)電路設(shè)計(jì),電路一點(diǎn)通給各位小伙伴們分享下不同類型的LED驅(qū)動(dòng)電路方案,后續(xù)項(xiàng)目設(shè)計(jì)研發(fā)可以參考選用,避免了一些冗余的方案選擇問題,方便你的電路設(shè)計(jì)工作。

2023-06-19 09:08:38 867

867

一般情況下,要重新配置一個(gè)FPGA需要使其處于復(fù)位狀態(tài),并通過外部控制器重新加載一個(gè)新設(shè)計(jì)到器件中。而局部重配置技術(shù)允許在FPGA內(nèi)部或外部的控制器在加載一個(gè)局部設(shè)計(jì)到一個(gè)可重配置模塊中時(shí)

2023-03-17 14:03:39 1305

1305 分享一些硬件電路的設(shè)計(jì)方案和心得,供一些剛學(xué)嵌入式的朋友參考,大神和老鳥請忽略哈。

2023-01-07 13:42:51 1256

1256 脈沖。將高壓整流濾波電路產(chǎn)生的高壓直流電變成高頻脈沖直流電,送到主變壓器降壓,變成低頻脈沖直流電。開關(guān)電路設(shè)計(jì)方案開關(guān)電路在單片機(jī)電路設(shè)計(jì)中經(jīng)常用到,一般有兩個(gè)作用

2022-09-13 10:33:49 584

584

電流/電壓轉(zhuǎn)換電路設(shè)計(jì)方案在工業(yè)控制中各類傳感器常輸出標(biāo)準(zhǔn)電流信號4~20mA,為此,常要先將其轉(zhuǎn)換成±10V;的電壓信號,以便送給各類設(shè)備進(jìn)行處理。這種轉(zhuǎn)換電路以4mA 為滿量程的0%對應(yīng)-10V

2009-12-17 09:55:16

高頻感應(yīng)加熱電源驅(qū)動(dòng)電路設(shè)計(jì)方案就目前國內(nèi)的感應(yīng)加熱電源研發(fā)現(xiàn)狀而言,高頻感應(yīng)加熱電源是主流的研發(fā)設(shè)計(jì)方向,也是很多工程師的工作重點(diǎn)。在今天的文章中,我們將會(huì)為大家分享一種基于IR2llO芯片的高頻

2021-11-06 14:36:01 78

78 小信號放大電路設(shè)計(jì)方案匯總

2021-09-14 15:01:12 121

121 智融SW3523車載快充電路設(shè)計(jì)方案

2021-08-14 11:01:10 83

83 AC24V接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

2021-07-12 11:16:36 30

30 AC110V/220V EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

2021-07-12 11:14:25 91

91 AC380V EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

2021-07-12 10:54:06 48

48 AV接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

2021-07-12 10:52:08 28

28 CAN總線接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

2021-07-12 10:45:28 188

188 Partial Reconfiguration(部分重配置)在現(xiàn)在的FPGA應(yīng)用中越來越常見,我們這次的教程以Project模式為例來說明部分重配置的操作過程。

2021-07-05 15:28:24 2799

2799

三相智能電表的RS-485通訊電路設(shè)計(jì)方案

2021-06-26 16:32:05 50

50 基于電流傳輸器的檢測電路設(shè)計(jì)方案

2021-06-15 10:52:22 41

41 SSS1530電路設(shè)計(jì)方案免費(fèi)下載。

2021-06-10 16:22:57 26

26 帶NFC管理的移動(dòng)通信終端電路設(shè)計(jì)方案

2021-06-07 10:17:16 30

30 利用FPGA的在系統(tǒng)下載或重新配置功能,可以在電路設(shè)計(jì)和調(diào)試時(shí)改變整個(gè)電路的硬件邏輯關(guān)系,而不需要改變印制電路板的結(jié)構(gòu)。

2021-05-12 10:46:10 25

25 卡拉OK人聲增效電路設(shè)計(jì)方案

2021-03-25 11:06:33 7

7 電子發(fā)燒友網(wǎng)站提供(溫度傳感器電路設(shè)計(jì)方案)資料免費(fèi)下載。

2020-11-11 12:00:26 104

104 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的硬件電路設(shè)計(jì)教程和FPGA平臺(tái)資料簡介包括了:FPGA技術(shù)概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設(shè)計(jì);V4LX160 FPGA平臺(tái)介紹;

2020-07-06 18:11:22 152

152 485接口EMC電路設(shè)計(jì)方案!

2020-02-05 12:53:27 3778

3778 完成電子電路設(shè)計(jì)方案的過程大致分幾個(gè)步驟?需要注意什么?

2019-04-12 17:45:52 13438

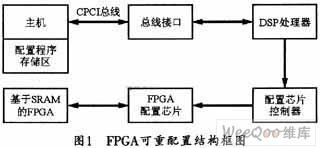

13438 關(guān)鍵詞:PLD , SRAM , 可重配置電路 由于SRAM的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動(dòng)態(tài)改變運(yùn)行電路中PLD的邏輯功能創(chuàng)造了條件。PLD使用SRAM單元來保存字的配置

2019-02-23 14:30:01 551

551

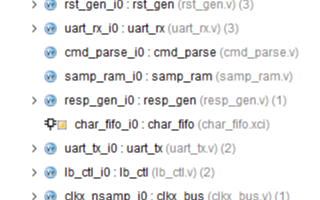

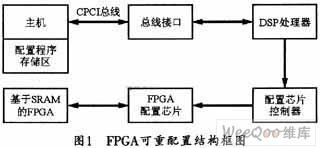

結(jié)合對FPGA重配置方案的軟硬件設(shè)計(jì),本文通過PC機(jī)并通過總線(如PCI總線)將配置數(shù)據(jù)流下載到硬件功能模塊的有關(guān)配置芯片,從而完成配置FPGA的全過程。該方法的軟件部分基于Visual C++的開發(fā)環(huán)境,并用C++語言開發(fā)動(dòng)態(tài)連接庫,以用于軟件設(shè)計(jì)應(yīng)用程序部分的調(diào)用。

2018-12-30 09:26:00 2204

2204

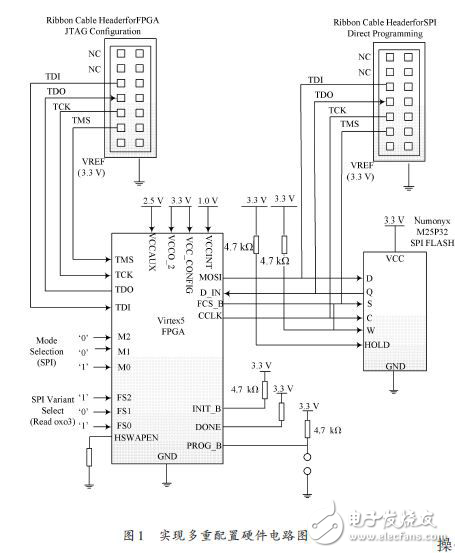

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據(jù)不同時(shí)刻的需求,可以從FLASH 中貯存的多個(gè)比特文件選擇加載其中的一個(gè),實(shí)現(xiàn)系統(tǒng)功能的變換。

2018-12-04 08:37:00 4253

4253

本視頻介紹了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介紹了對部分重配置的更廣泛的訪問權(quán)限

2018-11-20 06:25:00 3629

3629 介紹了采用CPLD和Flash器件對FPGA 實(shí)現(xiàn)快速并行配置,并給出了具體的硬件電路設(shè)計(jì)和關(guān)鍵模塊的內(nèi)部編程思路。

2018-10-24 15:15:49 7

7 應(yīng)用而設(shè)計(jì)的基于FPGA的賽靈思可重配置加速堆棧,包括庫、框架集成、開發(fā)板并支持OpenStack。通過賽靈思FPGA,該可重配置加速堆棧方案提供了業(yè)界最高的計(jì)算效率:比x86服務(wù)器CPU高出40倍;比競爭型FPGA方案高出6倍。

2018-07-31 09:08:00 665

665 的應(yīng)用。在主流的FPGA中,絕大多數(shù)都采用了SRAM來存放配置數(shù)據(jù),稱為SRAM FPGA。這種FPGA的突出優(yōu)點(diǎn)是可以進(jìn)行多次配置。通過給FPGA加載不同的配置數(shù)據(jù),即可令其實(shí)現(xiàn)不同的邏輯功能.FPGA這種可重配置的能力將給數(shù)字系統(tǒng)的設(shè)計(jì)帶來很大的方便。

2018-07-18 12:50:00 2191

2191

基于FPGA的調(diào)焦電路設(shè)計(jì)方案資料下載

2018-05-07 15:53:08 9

9 WiFi產(chǎn)品的一般射頻電路設(shè)計(jì)方案資料

2018-04-17 10:04:37 30

30 本文主要介紹了電流檢測電路設(shè)計(jì)方案匯總(六款模擬電路設(shè)計(jì)原理圖詳解),采用差分運(yùn)放進(jìn)行高端電流檢測的電路更便于使用,因?yàn)榻谕瞥隽嗽S多種集成電路解決方案。專用高端檢流電路內(nèi)部包含了完成高端電流檢測

2018-02-06 11:31:39 320822

320822

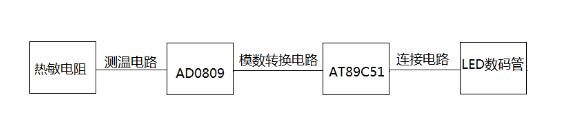

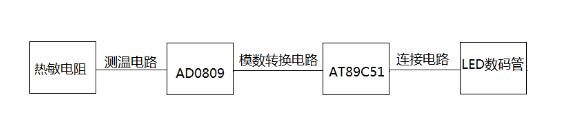

熱電阻是基于電阻的熱效應(yīng)進(jìn)行溫度測量的,即電阻體的阻值隨溫度的變化而變化的特性。本文主要介紹了四款熱敏電阻測溫電路設(shè)計(jì)方案詳情。

2018-02-02 14:54:56 46935

46935

本文主要介紹了計(jì)數(shù)報(bào)警器電路設(shè)計(jì)方案匯總(多款模擬電路設(shè)計(jì)原理圖詳解),方案二主要由直流電源電路(整流、濾波、穩(wěn)壓電路)和計(jì)數(shù)報(bào)警電路(計(jì)數(shù)電路、譯碼電路、顯示電路、聲光報(bào)警電路)組成,:聲光報(bào)警功能用蜂鳴器和LED燈實(shí)現(xiàn),控制LED報(bào)警十秒,蜂鳴器報(bào)警10秒。

2018-01-29 10:30:07 22300

22300

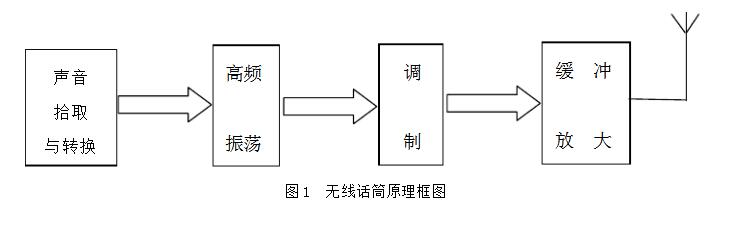

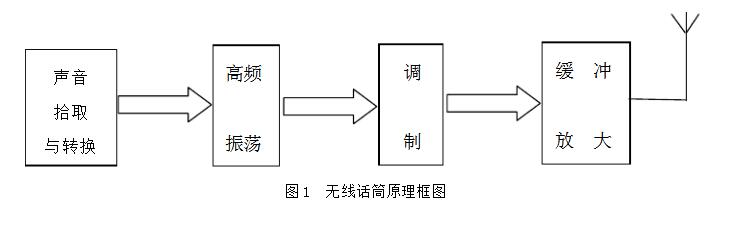

本文介紹了無線話筒電路設(shè)計(jì)方案及原理圖等。無線話筒電路由聲音拾取電路、聲音轉(zhuǎn)換電路、高頻振蕩器、調(diào)制電路、緩沖放大電路和電源組成。

2018-01-25 15:14:55 28711

28711

本文為大家?guī)砦蹇钗迦吮頉Q器電路設(shè)計(jì)方案。

2018-01-18 09:18:07 93932

93932

本文為大家?guī)砭趴畈煌某ㄟ\(yùn)算電路設(shè)計(jì)方案,包括這九款模擬電路設(shè)計(jì)的原理及設(shè)計(jì)過程。

2018-01-17 18:24:49 46006

46006

本文為大家介紹五款乘法器電路設(shè)計(jì)方案,包括五款模擬電路設(shè)計(jì)原理及仿真程序分享,以供參考。

2018-01-17 18:03:30 50165

50165

本文為大家?guī)砦宸N減法器電路設(shè)計(jì)方案介紹。

2018-01-17 11:29:44 83406

83406

對視頻等時(shí)序關(guān)鍵型應(yīng)用,采用純硬件解決方案可提升賽靈思 FPGA 的運(yùn)行能力。我們采一款基于小型狀態(tài)機(jī)的純硬件解決方案,并采用內(nèi)部配置訪問端口 (ICAP)接口加載比特流。這種方法具有多種優(yōu)勢

2017-11-22 17:08:56 1326

1326 視頻、影像和電信市場的標(biāo)準(zhǔn)推動(dòng)了異構(gòu)可重配置DSP硬件平臺(tái)的使用。在本文中這些平臺(tái)包括DSP處理器和FPGA,它們提供的現(xiàn)成硬件解決方案可以解決視頻、影像和電信設(shè)計(jì)中的重大難題,同時(shí)又不失差異化

2017-11-06 13:59:42 2

2 FPGA 動(dòng)態(tài)局部重配置技術(shù)是近幾年才發(fā)展起來的一項(xiàng)新技術(shù)。這項(xiàng)技術(shù)可以使 FPGA運(yùn)行時(shí),通過 JTAG或 SelectMAP(ICAP)動(dòng)態(tài)重配置部分區(qū)域,而不影響非重配置區(qū)域的正常工作。 在

2017-10-18 16:38:59 4

4 工作效率。通過FPGA 的多重配置可以有效地精簡控制結(jié)構(gòu)的設(shè)計(jì),同時(shí)可以用邏輯資源較少的FPGA 器件實(shí)現(xiàn)需要很大資源才能實(shí)現(xiàn)的程序。以Virtex5系列開發(fā)板和配置存儲(chǔ)器SPIFLASH為基礎(chǔ),從硬件電路和軟件設(shè)計(jì)兩個(gè)方面對多重配置進(jìn)行分析,給出了多

2017-10-12 17:57:08 15

15 在論壇里有人發(fā)帖子,問關(guān)于FPGA的硬件電路問題,我想涉及到這個(gè)問題的基本都是硬件工程師或者在讀學(xué)生,所以我介紹一下我是怎么學(xué)習(xí)FPGA的硬件電路設(shè)計(jì)的吧!

2017-02-11 12:55:11 24118

24118 基于FPGA技術(shù)的RS232接口時(shí)序電路設(shè)計(jì)方案

2017-01-26 11:36:55 29

29 數(shù)字電路設(shè)計(jì)方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 精密光電檢測電路設(shè)計(jì)方案

2016-12-15 18:25:41 63

63 fpga電源設(shè)計(jì)方案

2016-11-15 17:36:01 16

16 這里要列出一個(gè)市面上最常見的spartan-3的xc3s400的配置電路,所有spartan-3的FPGA配置電路的鏈接方式都是一樣的。

2015-02-04 09:47:57 3095

3095

通過FPGA的多重配置可以有效地精簡控制結(jié)構(gòu)的設(shè)計(jì),同時(shí)可以用邏輯資源較少的FPGA器件實(shí)現(xiàn)需要很大資源才能實(shí)現(xiàn)的程序。以Virtex5系列開發(fā)板和配置存儲(chǔ)器SPI FLASH為基礎(chǔ),從硬件電路

2014-01-24 14:17:22 13013

13013

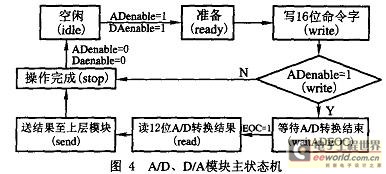

為了研究數(shù)字化γ能譜儀,本文提出一種基于FPGA的數(shù)字核脈沖分析器硬件設(shè)計(jì)方案,該方案采用現(xiàn)場可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設(shè)計(jì)。用QuartusⅡ軟件在FPGA平臺(tái)上完成了數(shù)字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 1742

1742

為了降低CCD驅(qū)動(dòng)電路的功耗,提出了基于共模扼流圈的CCD驅(qū)動(dòng)電路設(shè)計(jì)方案。該方案采用CCD驅(qū)動(dòng)器產(chǎn)生低電壓的驅(qū)動(dòng)信號,然后利用共模扼流圈進(jìn)行電壓幅度的放大。

2013-10-24 15:54:48 3242

3242

為了同時(shí)實(shí)現(xiàn)計(jì)算機(jī)對FPGA進(jìn)行在線配置和高速數(shù)據(jù)傳輸,提出了一種基于CY7C68013A芯片的USB2.0接口設(shè)計(jì)方案。介紹了以CY7C68013A芯片為核心的系統(tǒng)硬件電路設(shè)計(jì)和軟件編程,詳細(xì)分析了

2013-09-23 17:57:41 174

174 本文介紹了XiLinx FPGA中DCM的結(jié)構(gòu)和相關(guān)特性,提出了一種基于XiLinx FPGA的DCM動(dòng)態(tài)重配置的原理方法,并給出了一個(gè)具體的實(shí)現(xiàn)系統(tǒng)。系統(tǒng)僅通過外部和......

2012-05-25 13:42:50 39

39 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 基于 FPGA 的 RCS 有幾項(xiàng)值得注意的設(shè)計(jì)事項(xiàng)與優(yōu)勢。其核心部分是我們連接在一起以構(gòu)成單個(gè)計(jì)算系統(tǒng)的數(shù)個(gè)FPGA。在我們的可重配置系統(tǒng)中,我們使用了正交通信系統(tǒng),將 FPGA 布置在矩

2011-09-20 08:57:32 27

27 為了滿足對分?jǐn)?shù)階 信號變換 進(jìn)行實(shí)時(shí)計(jì)算的要求,提出一種基于Altera St ratix II FPGA 平臺(tái)的可重配置分?jǐn)?shù)階信號變換處理器的硬件實(shí)現(xiàn)方案. 根據(jù)角度分解的算法,設(shè)計(jì)了一種通用的硬件框

2011-07-04 15:13:03 33

33 FPGA的全局動(dòng)態(tài)可重配置技術(shù)主要是指對運(yùn)行中的FPGA器件的全部邏輯資源實(shí)現(xiàn)在系統(tǒng)的功能變換,從而實(shí)現(xiàn)硬件的時(shí)分復(fù)用。提出了一種基于System ACE的全局動(dòng)態(tài)可重配置設(shè)計(jì)方法,

2011-01-04 17:06:01 54

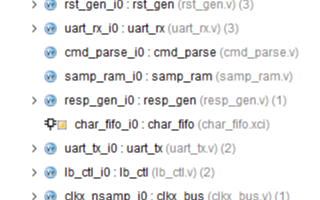

54 實(shí)現(xiàn)了一種用于上位機(jī)和FPGA處理板之間通信的可重配置接口,詳細(xì)介紹了該接口的包格式設(shè)計(jì)和FPGA邏輯設(shè)計(jì)。仿真結(jié)果表明,該可重配置接口能根據(jù)信令,實(shí)現(xiàn)準(zhǔn)實(shí)時(shí)在線參數(shù)配置

2010-11-22 15:15:28 12

12 本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內(nèi)嵌的增強(qiáng)型可重配置PLL在不同的輸入時(shí)鐘頻率之間的動(dòng)態(tài)適應(yīng),其目的是通過提供PLL的重配置功能,使得不需要對

2010-11-02 15:17:24 27

27 介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺(tái)設(shè)計(jì)方法。給出了系統(tǒng)設(shè)計(jì)的硬件結(jié)構(gòu)和重要接口, 提出了由ARM微處理器通過JTAG在系統(tǒng)配置FPGA的方法, 以滿足重配置系統(tǒng)中軟件

2010-09-14 16:40:09 21

21 ISE12.2設(shè)計(jì)套件強(qiáng)化了其部分可重配置技術(shù)設(shè)計(jì)流程,并通過智能時(shí)鐘門控技術(shù)降低24% 的 BRAM 功耗。賽靈思部分可重配置技術(shù),是目前唯一經(jīng)行業(yè)驗(yàn)證的可重配置FPGA

2010-07-31 12:39:03 408

408 基于FPGA的兩相步進(jìn)電機(jī)細(xì)分驅(qū)動(dòng)電路設(shè)計(jì)摘要:在采用步進(jìn)電機(jī)驅(qū)動(dòng)的機(jī)構(gòu)中,為了提高定位精度,提出了一種基于FPGA 的兩相步進(jìn)電機(jī)細(xì)分驅(qū)動(dòng)電路的設(shè)計(jì)方案。

2010-05-11 16:09:41 50

50 采用VC++程序的FPGA重配置設(shè)計(jì)方案利用現(xiàn)場可編程邏輯器件FPGA的多次可編程配置特點(diǎn),通過重新下載存儲(chǔ)于存儲(chǔ)器的不同系統(tǒng)數(shù)據(jù)

2010-04-14 15:14:57 541

541

基于FPGA的光電抗干擾電路設(shè)計(jì)方案

光電靶的基本原理是:當(dāng)光幕內(nèi)的光通量發(fā)生足夠大的變化時(shí),光電傳感器會(huì)響應(yīng)這種變化而產(chǎn)生電信號。這就

2010-02-09 10:31:20 601

601 基于FPGA的PCB測試機(jī)硬件電路設(shè)計(jì)研究

引言

PCB 光板測試機(jī)基本的測試原理是歐姆定律,其測試方法是將待測試點(diǎn)間加一定的測試電壓,用譯碼電路選中PCB

2010-01-04 09:12:33 913

913

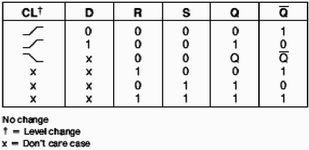

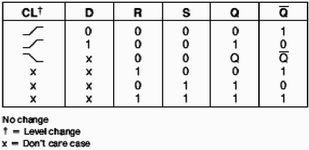

自動(dòng)開/關(guān)機(jī)電路設(shè)計(jì)方案

摘要:本文介紹了一種結(jié)構(gòu)簡單、使用方便可靠的開/關(guān)機(jī)電路。電路使用一個(gè)D觸發(fā)器,配合軟件上的處理實(shí)現(xiàn)單鍵

2009-12-24 15:07:15 1513

1513

基于SRAM的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動(dòng)態(tài)改變運(yùn)行電路中PLD的邏輯功能創(chuàng)造了條件。PLD使用SRAM單元來保存字的配置數(shù)據(jù)決

2009-06-20 11:05:37 821

821

電子發(fā)燒友App

電子發(fā)燒友App

評論