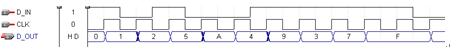

GM3043雙鍵工作時序電路圖

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電子技術(shù)>電路圖>光電傳輸電路>GM3043雙鍵工作時序電路圖

相關(guān)推薦

155

155

680

680

10208

10208

423

423

5679

5679

15

15 3

3 13

13 5

5 3992

3992 5677

5677

3787

3787

1993

1993

1943

1943

868

868 24417

24417 4359

4359 12

12 12890

12890

25

25 17763

17763

34

34 20

20 51

51 14

14 6

6 20

20 15

15 21

21 34

34 8

8 1903

1903

5554

5554

評論