傳感器和物聯(lián)網(wǎng) (IoT) 技術(shù)正迅速擴(kuò)展到工業(yè)、商業(yè),甚至是消費(fèi)領(lǐng)域中。隨著這種技術(shù)擴(kuò)展,越來(lái)越需要確保來(lái)自相關(guān)傳感器及其前端接口電路的數(shù)據(jù)保持完整性。

當(dāng)單個(gè)接口IC支持多個(gè)傳感器時(shí),數(shù)據(jù)完整性的潛在問(wèn)題會(huì)變得更加嚴(yán)重,因?yàn)閱蝹€(gè)IC的問(wèn)題可能會(huì)損壞一組讀數(shù)。這可能會(huì)進(jìn)而導(dǎo)致對(duì)感測(cè)情況評(píng)估不正確,造成不合適甚至危險(xiǎn)的系統(tǒng)操作。

本文將介紹傳感器到處理器的信號(hào)鏈中,軟硬(瞬態(tài))故障以及傳感器讀數(shù)不準(zhǔn)確的各種根源。

傳感器到處理器的信號(hào)路徑

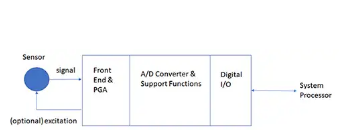

最終影響任何傳感器讀數(shù)完整性的因素都始于圖1中所示信號(hào)鏈的三個(gè)主要功能塊。這些功能塊是:

傳感器及其引線

信號(hào)調(diào)節(jié)IC中的模擬前端,以模數(shù)轉(zhuǎn)換器 (ADC) 為中心

連接到系統(tǒng)處理器的數(shù)字I/O

傳感器到處理器的基本信號(hào)路徑圖

圖 1:傳感器到處理器的基本信號(hào)路徑在原則上只包含一些基本功能,但實(shí)用的接口 IC 提供了許多附加功能和特性。

在多通道系統(tǒng)中,通常混合了各種類型的傳感器,如熱電偶、電阻溫度檢測(cè)器 (RTD) 和壓力傳感器。當(dāng)然,傳感器可能會(huì)發(fā)生故障,或者其互連引線可能會(huì)形成開(kāi)路,或者與相鄰的引線、電源軌或接地形成短路。

根據(jù)傳感器的類型,其引線的故障可能會(huì)立即表現(xiàn)為讀數(shù)“偏離標(biāo)度”。相反,某些故障模式會(huì)導(dǎo)致不準(zhǔn)確但看起來(lái)合理的信號(hào)。此外,某些傳感器(如 RTD)需要外部激勵(lì)電流,而此電流必須在設(shè)定范圍內(nèi)才能提供有效讀數(shù)。鑒于這些原因,可取的做法是:測(cè)試傳感器與模擬前端之間信號(hào)路徑的連續(xù)性,并檢查信號(hào)是否保持在允許的最小和最大限值之間,但最好使用不受 ADC 潛在問(wèn)題影響的模擬電路。

這不僅提供準(zhǔn)確的讀數(shù),而且還能使系統(tǒng)決策算法在運(yùn)行時(shí)根據(jù)這些讀數(shù),采用可信度極高的源數(shù)據(jù)。

但是,所有這些額外的檢查和平衡會(huì)增加額外的元器件,需要更大的占用空間和額外的設(shè)計(jì)時(shí)間。

自詢問(wèn)式 IC 確保傳感器數(shù)據(jù)的完整性

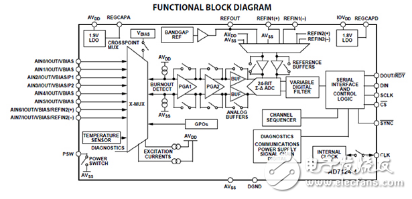

為了滿足對(duì)高完整性數(shù)據(jù)的需求,同時(shí)對(duì)設(shè)計(jì)時(shí)間和占用空間的影響最小,Analog Devices 推出了 AD7124-8BCPZ-RL7,這是一種以傳感器為中心的 ADC 和接口,其功能遠(yuǎn)遠(yuǎn)超出了基本的信號(hào)調(diào)節(jié)和轉(zhuǎn)換。該產(chǎn)品包括多種信號(hào)和自診斷功能,以確保數(shù)據(jù)完整性。

Analog Devices 的 AD7124 以傳感器為中心的 ADC 和接口示意圖

圖 2:AD7124 是以傳感器為中心的 ADC 和接口,其功能遠(yuǎn)超基本的信號(hào)調(diào)節(jié)和轉(zhuǎn)換,包括多種信號(hào)和自診斷功能,用于確保數(shù)據(jù)的完整性。

AD7124 是一款四通道、低噪聲、低功耗、24 位、三角積分 (Σ-Δ) 型器件。采樣率范圍從略高于每秒 1 個(gè)樣本(對(duì)多種傳感器及其應(yīng)用來(lái)說(shuō)已經(jīng)足夠)到每秒 19,200 個(gè)樣本。在最低采樣率下,該器件耗電 255 微安 (μA)。由于其設(shè)計(jì)強(qiáng)調(diào)低噪聲(低于 25 納伏 (nV) rms),以及內(nèi)部電壓基準(zhǔn)的低漂移 (10 ppm/°C),該器件的讀數(shù)精度得到了提升。

AD7124 本身采用 32 引線 LFCSP 和 24 引線 TSSOP 封裝。其靈活的數(shù)字 I/O 支持 3 線和 4 線 SPI、QSPI、MICROWIRETM 和 DSP 兼容接口。

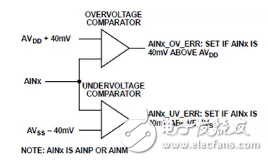

AD7124 采用兩種技術(shù)解決了前面提到的傳感器引線問(wèn)題:信號(hào)限制警報(bào)和燒毀電流測(cè)試。信號(hào)限制警報(bào)使用過(guò)壓/欠壓警報(bào)監(jiān)視器,來(lái)檢查四對(duì)模擬輸入連接中每一對(duì)的絕對(duì)電壓(圖 3)。該電壓必須在規(guī)定的范圍內(nèi),以滿足規(guī)格書(shū)中的規(guī)格。

傳感器基本驗(yàn)證示意圖

圖 3:使用信號(hào)限制警報(bào)對(duì)傳感器引線進(jìn)行基本驗(yàn)證時(shí),可采用基于硬件且設(shè)置了固定最小值/最大值的比較器。

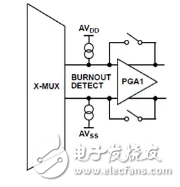

燒毀電流測(cè)試使用一對(duì)互補(bǔ)的可編程電流阱和電流源。通過(guò)在傳感器引線中灌拉一對(duì)預(yù)定義的電流,AD7124 可以驗(yàn)證其完整性(圖 4)。全開(kāi)或全關(guān)的電流將轉(zhuǎn)換為所選的待測(cè)模擬輸入線對(duì)。

灌拉一對(duì)預(yù)定義電流的示意圖

圖 4:通過(guò)在傳感器引線中灌拉一對(duì)預(yù)定義的電流,AD7124 可以驗(yàn)證其完整性。

滿量程讀數(shù)(或接近值)可能意味著前端傳感器處于開(kāi)路狀態(tài)。如果測(cè)得的電壓為 0 伏,則可能表明傳感器已短路。錯(cuò)誤寄存器中會(huì)設(shè)置相應(yīng)的標(biāo)志位,以指示錯(cuò)誤的發(fā)生和類型。

最后,對(duì)于用戶提供外部基準(zhǔn)而非使用內(nèi)部基準(zhǔn)(通常使用 RTD 或應(yīng)變片完成)的應(yīng)用,AD7124 會(huì)檢查所有外部轉(zhuǎn)換基準(zhǔn)電壓是否正確無(wú)誤。

驗(yàn)證前端和 ADC

雖然外部傳感器及其引線出現(xiàn)問(wèn)題的可能性最大,但驗(yàn)證前端/轉(zhuǎn)換 IC 本身的性能仍然至關(guān)重要。可能超出規(guī)格或完全失效的功能包括:

內(nèi)部 ADC 電壓基準(zhǔn)

可編程增益放大器 (PGA),用于放大輸入信號(hào)以匹配 ADC 量程,從而實(shí)現(xiàn)最高分辨率

低壓差穩(wěn)壓器 (LDO),用于提供所需的傳感器激勵(lì)

IC 的內(nèi)部電源軌

ADC 本身

為了測(cè)試信號(hào)鏈的模擬部分,AD7124 會(huì)調(diào)用基于硬件和固件的自檢。隨后產(chǎn)生 20 毫伏 (mV) 信號(hào),而該信號(hào)可在內(nèi)部傳送到四個(gè)差分輸入通道中的任一個(gè),然后進(jìn)行數(shù)字化。這樣做有多個(gè)目的:驗(yàn)證輸入通道多路復(fù)用器和 ADC 的基本操作;還可以通過(guò)更改 PGA 的增益設(shè)置并檢查得到的 ADC 讀數(shù),對(duì) PGA 進(jìn)行評(píng)估。

ADC 也是潛在問(wèn)題的根源之一。AD7124 采用完善的 Σ-Δ 轉(zhuǎn)換器架構(gòu),內(nèi)含 1 位調(diào)制器和必需的數(shù)字濾波器。ADC 性能的全面測(cè)試同時(shí)采用模擬和數(shù)字技術(shù)。

在 AD7124 中,如果調(diào)制器輸出包含 20 個(gè)連續(xù)的 1 或 0,則表示調(diào)制器的一個(gè)軌或另一個(gè)軌已飽和,并且會(huì)設(shè)置錯(cuò)誤標(biāo)志位。同樣,IC 在自啟動(dòng)偏移校準(zhǔn)之后,檢查 ADC 偏移系數(shù)是否在 0x7FFFF 和 0xF80000 之間。如果系數(shù)超出此范圍,則會(huì)設(shè)置另一個(gè)錯(cuò)誤標(biāo)志位。最后,在滿量程校準(zhǔn)期間,數(shù)字濾波器的任何溢出都會(huì)設(shè)置另一個(gè)錯(cuò)誤標(biāo)志位。

內(nèi)外部電源和電源軌也是潛在的問(wèn)題來(lái)源。許多傳感器需要少量激勵(lì)功率,而這通常由模擬前端 IC 內(nèi)的小型、低噪聲 LDO 提供。

AD7124 以兩種方式檢查其 LDO 輸出。首先,LDO 的輸出可以在內(nèi)部路由至 ADC,并與預(yù)期值進(jìn)行比較。其次,獨(dú)立于 ADC 的硬件比較器會(huì)持續(xù)監(jiān)測(cè) LDO 相對(duì)于 IC 基準(zhǔn)值的變化。如果低于預(yù)設(shè)閾值,則會(huì)設(shè)置錯(cuò)誤標(biāo)志位。因此,可以在初始化期間評(píng)估 LDO,也可以持續(xù)進(jìn)行評(píng)估,而不會(huì)不斷消耗處理器資源。

為了進(jìn)一步確信,可以(在一定程度上)檢查用于監(jiān)測(cè)電源的測(cè)試電路,方法是將測(cè)試電路的輸入接地(標(biāo)稱 0 伏),然后檢查數(shù)字讀數(shù)。AD7124 通過(guò)檢查所需的 0.1 微法 (μF) 去耦電容器是否存在并已連接,進(jìn)一步確保數(shù)據(jù)的完整性。方法是指示 AD7124 通過(guò)其內(nèi)部開(kāi)關(guān)物理斷開(kāi)去耦電容器,然后檢查 LDO 輸出。如果 LDO 電壓下降,則去耦電容器未通電。同樣,這也會(huì)設(shè)置錯(cuò)誤標(biāo)志位。

當(dāng)然,每個(gè) IC 都具有最高溫度額定值,超出該值將超出規(guī)格,甚至?xí)⒓匆l(fā)故障。因此,AD7124 內(nèi)置一個(gè)傳感器,可隨時(shí)提供芯片溫度讀數(shù),典型精度為 ±0.5°C。

數(shù)字錯(cuò)誤怎么辦?

到目前為止,我們已經(jīng)了解了如何確保模擬傳感器或轉(zhuǎn)換功能的性能和精度。但是,在部署了許多此類傳感器的惡劣電氣工業(yè)環(huán)境中,存在影響數(shù)字電子設(shè)備的噪聲、EMI/RFI 和瞬變問(wèn)題。因此,必須確保內(nèi)部數(shù)字電路的性能,以及系統(tǒng)處理器的接口連接,以確保數(shù)據(jù)以及任何讀寫(xiě)操作的穩(wěn)健性。

AD7124 從以下操作和特性開(kāi)始,通過(guò)多管齊下的方式實(shí)現(xiàn)這一點(diǎn):

檢查主時(shí)鐘的性能。在設(shè)置輸出數(shù)據(jù)速率、濾波器建立時(shí)間以及濾波器陷波頻率時(shí),需要使用主時(shí)鐘。主時(shí)鐘由獨(dú)立且可隨時(shí)回讀的向上計(jì)數(shù)寄存器進(jìn)行檢查。

通過(guò)特殊時(shí)鐘計(jì)數(shù)器,檢查每個(gè) SPI 讀寫(xiě)操作中使用的 SCLK 脈沖數(shù)。該數(shù)值應(yīng)為 8 的倍數(shù)(所有 SPI 操作均使用 8、16、32、40 或 48 個(gè)時(shí)鐘脈沖)。

AD7124 檢查讀寫(xiě)操作是否僅對(duì)有效的寄存器地址進(jìn)行尋址。

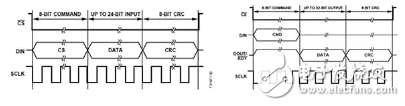

這些步驟處理內(nèi)部操作,但不能確保處理器接口及其數(shù)據(jù)的完整性。為了提供極高的數(shù)據(jù)可信度,用戶可以指示 AD7124 實(shí)施循環(huán)冗余校驗(yàn) (CRC) 多項(xiàng)式校驗(yàn)和算法。校驗(yàn)和確保只將有效數(shù)據(jù)寫(xiě)入寄存器,并允許驗(yàn)證從寄存器讀取的數(shù)據(jù)(圖 5)。請(qǐng)注意,校驗(yàn)和是一種高可信度技術(shù),甚至能夠檢測(cè)單比特錯(cuò)誤,但無(wú)法糾正這些錯(cuò)誤。

將基于多項(xiàng)式的 CRC 校驗(yàn)和添加到 SPI 寫(xiě)入和 SPI 讀取事務(wù)的示意圖(點(diǎn)擊放大)

圖 5:將基于多項(xiàng)式的 CRC 校驗(yàn)和添加到 SPI 寫(xiě)入(左)和 SPI 讀取(右)事務(wù),以檢測(cè)單比特錯(cuò)誤。

啟用后,此操作將計(jì)算數(shù)據(jù)塊的校驗(yàn)和,并將其附加到每個(gè)讀寫(xiě)事務(wù)的末尾。為了確保寄存器寫(xiě)入成功,需要回讀寄存器,以驗(yàn)證存儲(chǔ)的校驗(yàn)和與根據(jù)數(shù)據(jù)計(jì)算得出的校驗(yàn)和是否相符。

在惡劣的電氣環(huán)境中,即使是存儲(chǔ)器也可能出現(xiàn)比特錯(cuò)誤。為了對(duì)片載寄存器中的此類錯(cuò)誤進(jìn)行高級(jí)校驗(yàn),AD7124 每次都會(huì)針對(duì)以下情況的一系列操作計(jì)算校驗(yàn)和:

存在寄存器寫(xiě)入周期時(shí)

存在偏移/滿量程校準(zhǔn)時(shí)

器件執(zhí)行單個(gè)轉(zhuǎn)換周期,ADC 在轉(zhuǎn)換完成后進(jìn)入待機(jī)模式時(shí)

退出連續(xù)讀取模式時(shí)

為了增強(qiáng)穩(wěn)健性,還會(huì)評(píng)估內(nèi)部只讀存儲(chǔ)器 (ROM)。上電時(shí),所有寄存器均初始化為存儲(chǔ)在 ROM 中的默認(rèn)值。此時(shí)會(huì)對(duì) ROM 內(nèi)容執(zhí)行 CRC 計(jì)算。如果計(jì)算出來(lái)的值與存儲(chǔ)的 CRC 結(jié)果不同,則表示存在至少一個(gè)單比特錯(cuò)誤。

AD7124 還可為多種類型的傳感器提供激勵(lì),并可通過(guò)放大器和 PGA 對(duì)傳感器輸出信號(hào)進(jìn)行調(diào)節(jié)和縮放。為了提供極高的穩(wěn)健性,AD7124 包含許多內(nèi)部寄存器,用于初始化、建立所需的功能模式和參數(shù),以及標(biāo)記各種錯(cuò)誤和故障。

使用 AD7124 評(píng)估板快速啟動(dòng) AD7124 設(shè)計(jì)

AD7124 是一個(gè)復(fù)雜的系統(tǒng),具有許多設(shè)計(jì)可能性和性能。它并非簡(jiǎn)單的“即插即用型”傳感器接口 IC。為了便于學(xué)習(xí),并使設(shè)計(jì)人員能夠快速熟悉各種潛在功能,Analog Devices 還提供了 EVAL-CN0376-SDPZ 評(píng)估板(圖 6)。

Analog Devices 的 EVAL-CN0376-SDPZ 評(píng)估板圖片

圖 6:EVAL-CN0376-SDPZ 評(píng)估板可加快設(shè)計(jì)導(dǎo)入的速度,并允許全面運(yùn)用 AD7124 的眾多功能和特性。

該評(píng)估板包含所需的電源和外部元器件,以便將 AD7124 連接到各種實(shí)際使用的傳感器以及處理器。該板由基于 Windows PC 的 CN-0376 評(píng)估軟件提供支持,該軟件通過(guò) USB 端口進(jìn)行通信,以配置和捕獲評(píng)估板中的數(shù)據(jù)。

總結(jié)

許多關(guān)鍵決策都是由嵌入系統(tǒng)處理器中的高級(jí)算法做出,如今這種決策方式在很多情況下因人工智能 (AI) 而得到改善。這些算法運(yùn)行、得出結(jié)論并采取行動(dòng)所依據(jù)的原始數(shù)據(jù)必須具有高度的完整性,這一點(diǎn)比以往任何時(shí)候都更為重要。AD7124 等 IC 可顯著提高數(shù)據(jù)的可信度,確保信號(hào)鏈中的每個(gè)鏈路(從引線和傳感器接口到自身的性能和功能)都按預(yù)期運(yùn)行且未受損壞。

來(lái)源;電子說(shuō)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論