電子發燒友網訊: 本文主要講述了TAKUMI公司的圖象IP核參考設計可用于S2C原型驗證平臺。S2C宣布,一家總部位于日本的高級圖形知識產權(IP)供應商,TAKUMI 公司,已成功在S2C基于FPGA的快

2012-07-03 13:50:45 1548

1548 Cadence宣布業內首個DDR4 Design IP解決方案在28納米級芯片上得到驗證

2012-09-10 09:53:24 1403

1403 Cadence設計系統公司公布一個新版的尖端功能驗證平臺與方法學,擁有全套最新增強功能,與之前發布的版本相比,可將SoC驗證效率提高一倍。 Incisive ?12.2提供了兩倍性能,全新Incisive調試分析器產品,全新低功耗建模,以及當今復雜IP與SoC高效驗證所需的數百種其他功能。

2013-01-27 10:44:38 1437

1437

OVM驗證方法學的Cookbook大家喜歡看英文版?還是中文版?了解一下 大家都在看什么版本的?都是什么口味?{:soso_e120:}

2012-01-11 10:41:45

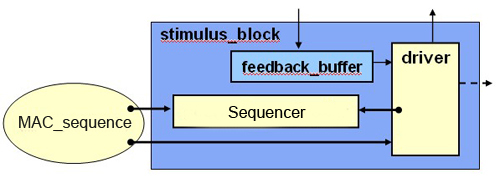

。 OVM 是一個開源 SystemVerilog 類庫和方法,它定義了可重用驗證 IP (VIP) 和測試的框架。它是 100% IEEE 1800SystemVerilog,并提供構建塊(對象)和一組

2022-02-13 17:03:49

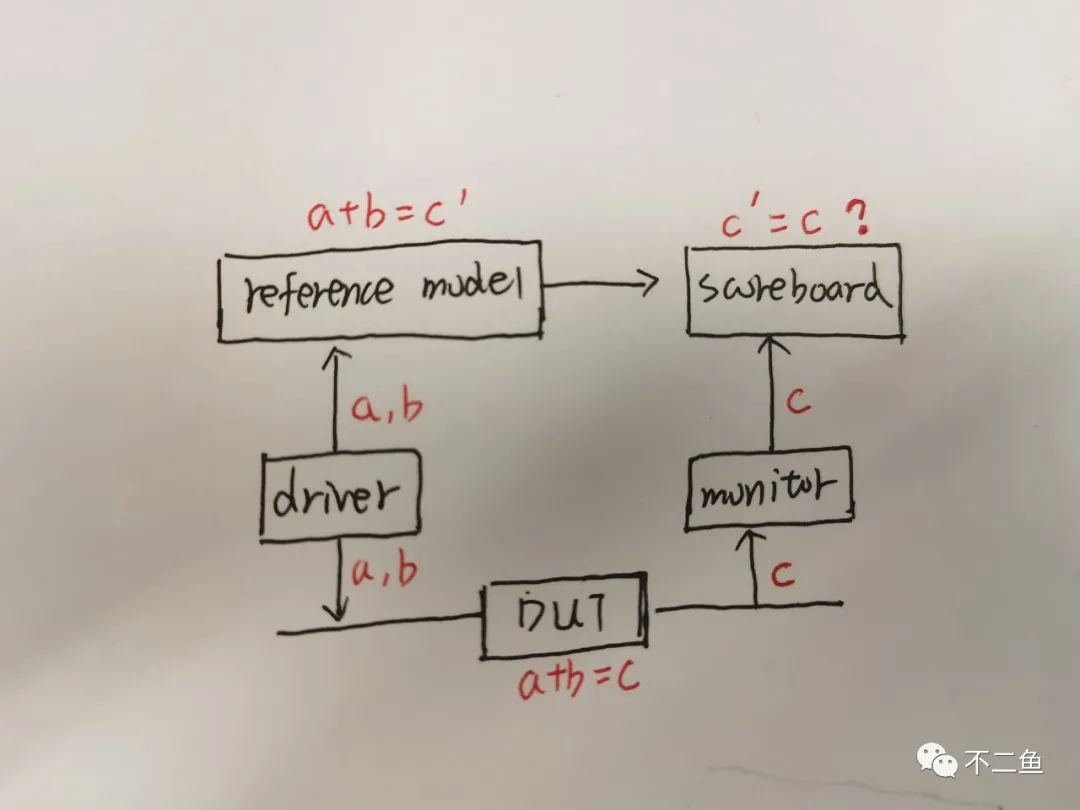

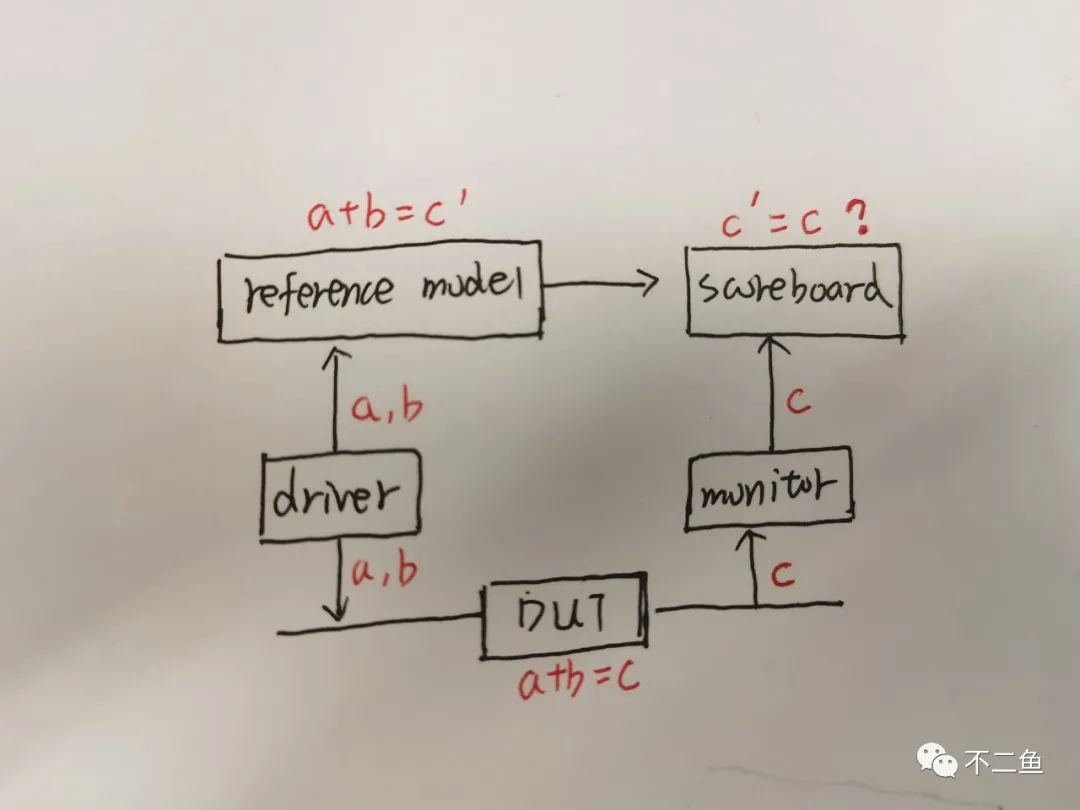

驗證用于找出DUT中的bug,這個過程通常是把DUT放入一個驗證平臺中來實現的。一個驗證平臺要實現如下基本功能:驗證平臺要模擬DUT的各種真實使用情況,這意味著要給DUT施加各種激勵,有正常的激勵

2020-12-02 15:21:34

加入factory機制 上一節《IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(五)》給出了一個只有driver、使用UVM搭建的驗證平臺。嚴格來說這根本就不算是UVM驗證

2020-12-08 12:07:21

本帖最后由 IC那些事兒 于 2020-12-4 15:50 編輯

上次更新完《IC驗證"UVM驗證平臺"組成》后本打算不再更新......但有人反映要繼續更新...繼續

2020-12-04 15:48:19

目前市面上基于SystemVerilog的驗證主要有三種:VMM(Verification Methodology Manual),這是Synopsys在2006年推出的,在初期是閉源的。當OVM

2020-12-01 15:09:14

IC驗證平臺

2021-08-09 07:39:47

在上一節中,**《IC驗證"UVM驗證平臺加入factory機制"(六)》**雖然輸出了“main_phase is called”,但是“data is drived”并沒有

2020-12-09 18:28:15

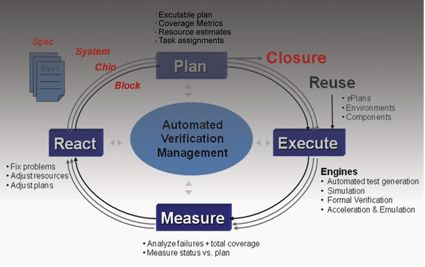

第二章 驗證flow驗證的Roadmap驗證的目標UVM驗證方法學ASIC驗證分解驗證策略和任務的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗證的Roadmap1.ASIC芯片項目流程市場需求

2021-11-01 06:28:47

Languages)”的一部分,又屬于“半導體IP核-不僅僅是設計(SemiconductorIP Core – Not Just Design)”書系列的“驗證用IP核和IP核驗證(VerificationIP

2022-11-03 13:07:24

SoC芯片的規模一般遠大于普通的ASIC,同時深亞微米工藝帶來的設計困難等使得SoC設計的復雜度大大提高。仿真與驗證是SoC設計流程中最復雜、最耗時的環節,約占整個芯片開發周期的50%~80%,采用

2019-10-11 07:07:07

機的協商,保持接口參數同步;數據通道驗證在該接口參數下的功能和性能,實現了接口的功能和性能驗證的自動化,大大提高了測試效率,保證測試用例的覆蓋率。該工具適用于多種平臺下的UART和SPI接口驗證。0

2019-06-21 05:00:09

隨著現代集成電路技術的發展,尤其是IP的大量使用,芯片的規模越來越大,系統功能越來越復雜,普通的EDA和FPGA仿真在速度和性能上已經無法勝任芯片仿真驗證的要求,功能驗證已經成為大規模芯片設計的一個

2010-05-28 13:41:35

我用quartus II調用modelsim仿真fft ip核,仿真結束后我想驗證下數據是否正確,結果是:我用matlab生成同樣的整形數據,然后用modelsim仿出的結果txt文件與用

2012-09-20 12:48:37

,本科5年數字芯片驗證工程師崗位要求:1、熟悉systemverilog 語言,熟練掌握UVM/VMM/OVM驗證方法學,獨立完成過中等規模以上模塊的驗證開發2、熟悉數字芯片驗證流程,三年以上相關工作經驗3、碩士3年,本科5年聯系方式:ucollide@163.com一八五八3907八零五

2018-03-13 09:27:17

免費的 I3C 從屬 IP 芯片是否經過驗證?

2023-05-05 07:16:21

本文介紹一種通用的UART自動驗證平臺,可用于自動測試UART接口的所有方面。

2021-04-30 06:46:31

隨著集成電路的規模和復雜度不斷增大,驗證的作用越來越重要。要在較短的時間內保證芯片最終能正常工作,需要將各種驗證方法相結合,全面充分地驗證整個系統。FF-DX是一款高性能定點DSP,為了在提升芯片

2011-12-07 17:40:14

、OVM等等,并對仿真方法有自己的深刻理解; 4.具有系統驗證和調試經驗,能夠根據數據通信產品的特點確定仿真驗證和仿真測試點; 5.具有3年以上仿真驗證經驗; 6.具有仿真平臺(硬件平臺和軟件平臺

2015-07-16 11:04:49

)。為此.我們利用VHDL設計一種嵌入式RISC8微處理器及應用芯片.設計后的IP核下載到FPGA(Field Programmable Gate Array.現場可編程門陣列)芯片上做驗證,并在

2021-09-01 19:32:45

的軟件模擬器作為驗證的第一站。Mentor Graphics驗證IP(VIP)是一個可復用組件庫,無縫集成到使用UVM、OVM、Verilog、VHDL和SystemC構建的測試平臺,也可與第三方軟件

2017-04-05 14:17:46

尋找一個現成的PMSM控制算法驗證平臺,幫我做控制算法的驗證實驗。拜謝各位前輩了!我的情況說明:我目前已經在simulink中搭建好控制算法,并且仿真出來了,但沒有驗證的平臺。因為時間比較急,我希望

2019-12-23 16:25:38

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優越性。

2021-05-06 07:20:48

SoC系統驗證平臺總體框架是怎樣的?SoC系統驗證平臺如何去構建?

2021-04-28 07:13:41

驗證碼與打碼平臺的對抗講起。何為打碼平臺?打碼平臺的基本原理是利用人工智能技術實現對驗證碼設計原理的突破。其工作流程如下圖所示:以前黑灰產要想獲取數據,首先會向自己想要獲取的數據頁面發送請求,若該數據頁面

2022-11-01 15:21:22

SoC與IP有什么關系?如何去驗證IP?

2021-04-28 06:02:37

講述兩個內容,芯片驗證以及驗證計劃。首先來看看芯片驗證在芯片設計當中的地位。芯片驗證是在一個芯片設計的過程當中,驗證各個轉化階段是否正確的執行的過程,一個芯片的設計涉及到多個階段的轉化。首先,分析市場需求

2021-01-21 15:59:03

請教一下基于FPGA的通信系統基帶驗證平臺該怎樣去設計?

2021-04-28 06:59:45

硬件驗證方法簡明介紹本書“硬件驗證方法簡明介紹”是“半導體 IP 核——不僅僅是設計”系列叢書中“驗證 IP 和 IP 核驗證”的一部分。本書調查、處理和介紹了 IC 驗證中涉及的一些關鍵方法、工具

2022-11-26 20:43:20

芯片的驗證平臺,用的主要技術 手段是SC/SV+OVM.平心而論,本人決非所謂高手、牛人。所謂的高手是什么,舉個例子,IC行業用TCL語言的人不少,這個語言的發明人覺得研究中用C不爽,干脆自己寫一個

2012-01-11 10:51:00

該IP核驗證平臺采用ALTERA Cyclone系列FPGA,型號為EP1C12Q240C8,提供超過30萬門系統資源和240k bit的內部高速FIFO, 以及內部兩個高速PLL,可以合成

2019-06-20 05:00:02

PCB設計,使用獨立的外部時鐘同步芯片,可以為PCI及其它接口提供穩定的零延遲時鐘系統電路,滿足PCI總線的時鐘要求,使驗證平臺高速,穩定,可靠的工作。 S1500硬件驗證板照片以下為IP核驗證平臺提供

2019-06-12 05:00:07

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。

2019-06-18 07:43:00

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。1、RFID芯片的FPGA

2019-05-29 08:03:31

探討了IP 核的驗證與測試的方法及其和VHDL 語言在IC 設計中的應用,并給出了其在RISC8 框架CPU 核中的下載實例。關鍵詞:IP 核;片上系統;驗證

2009-06-15 10:59:14 32

32 研究40Gb/s 交換IP 軟核的驗證和測試方法。通過建立SDH 芯片驗證平臺和SDH 芯片測試平臺, 實現IP 軟核的功能仿真、時序仿真和芯片性能測試。使得IP 軟核質量優良、性能穩定, 適應性

2009-11-27 14:30:16 6

6 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,業界第一個基于SystemVerilog、通用開放的驗證方法學;其基于事務交易級的方法學,基于Factory Pattern 的對象生

2010-07-04 11:43:22 7

7 無線溫度驗證系統 溫度壓力一體 溫度驗證儀分有線系統與無線系統。有線的溫度驗證系統精度低,價格相對于無線產品的價格要低廉的多,無線驗證系統操作方便,節省時間,而有線布線特別麻煩。所以在某些全封閉

2023-12-20 10:10:23

提出了基于事務斷言驗證技術,用屬性說明語言(Property Specification Language,PSL)描述系統的屬性,用事務進行系統的驗證,通過編程語言接口機理和工具控制語言來控制驗證中PSL斷

2010-08-02 17:26:35 0

0 IP驗證增量仿真技術的運用

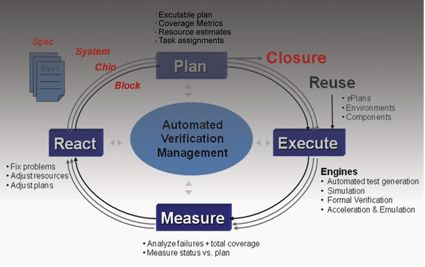

驗證涉及每個階段的迭代循環:仿真、檢查結果,改變激勵或設計或調試設置,重新仿真并不斷重復。在系統調

2009-01-27 17:58:24 834

834 隨著深亞微米工藝技術日益成熟,基于IP復用的IC設計方法廣泛采用,集成電路芯片的規模越來越大,這對集成電路驗證技術和方法學提出了很大的挑戰。就如芯片

2009-04-04 10:58:40 1360

1360

Cadence為PCI Express 3.0推出首款驗證解決方案

Cadence設計系統公司宣布其已經開發了基于開放驗證方法學(OVM)的驗證IP(VIP)幫助開發者應用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 針對數字信號處理器的不同仿真和驗證要求,提出了一種可測性軟硬件協同仿真和驗證平臺的設計. 采用可配置IP 模塊和總線結構,實現了硬件平臺可配置性和可重用性;采用在線仿真模塊

2011-06-09 17:54:21 39

39 IP核驗證平臺采用6層板PCB設計,使用獨立的外部時鐘同步芯片,可以為PCI及其它接口提供穩定的零延遲時鐘系統電路,滿足PCI總線的時鐘要求,使驗證平臺高速,穩定,可靠的工作。

2012-01-17 14:02:19 1501

1501

本文利用Altera公司的FPGA開發工具對皋于國產龍芯I號處理器IP核的SoC芯片進行ASIC流片前的系統驗證,全實時方式運行協同設計所產生的硬件代碼和軟件代碼,構建一個可獨立運行、可現場

2012-04-21 15:22:01 3161

3161

電子設計創新企業Cadence設計系統公司,今天宣布使用ARM AMBA協議類型的Cadence驗證IP(VIP)實現多個成功驗證項目,這是業界最廣泛使用的AMBA協議系列驗證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

997 無MCU的USB2.0設備控制器IP設計與驗證

2013-09-23 17:18:17 40

40 Mentor Graphics 公司(納斯達克代碼:MENT)今日宣布推出面向 ARM AMBA 5 AHB 片上互連規范的驗證 IP (VIP)。該新 VIP 在 Mentor? 企業驗證平臺

2015-11-12 11:28:11 1132

1132 SoC基于IP設計的特點使驗證項目中多語言VIP(Verification IP)協同驗證的需求不斷增加,給驗證工作帶來了很大的挑戰。為了解決多語言VIP在SoC驗證環境靈活重用的問題。提出了一種

2015-12-31 09:25:13 12

12 基于UVM的CPU卡芯片驗證平臺_錢一文

2017-01-07 19:00:39 4

4 基于UVM的驗證平臺設計研究_王國軍

2017-01-07 19:00:39 4

4 基于IEEE1500標準的IP核測試殼的設計與驗證_馮燕

2017-01-07 19:00:39 23

23 北京亞科鴻禹電子有限公司在北京發布一款針對2K/4K超高清視頻驗證的原型驗證開發平臺-VeriTiger-M2000T。此平臺作為亞科鴻禹”All-In-One”家族的最新成員,主要為廣大的視音頻SOC/IP的硬件/軟件驗證客戶提供完整的解決方案。

2017-02-11 16:49:11 1406

1406 基于OVM的32位微處理器驗證_吳勇昊

2017-03-17 08:00:00 3

3 參數化的IP是可配置的,這意味著在不同的SOC中IP設計可以有不同的設計參數,設計參數可以對應到協議、端口號、端口名稱、以及內部邏輯。大量的IP設計參數非常影響驗證環境的構建,比如testbench

2017-09-15 14:37:34 6

6 功能驗證正成為IP 驗證的瓶頸,并影響到整個設計團隊。設計工程師想方設法提高驗證效率,以實現整個芯片設計的最佳利益。在這里,我們提供10 個簡單技巧,顯著提升您的IP 驗證效率。 1.參與驗證計劃

2017-10-19 09:17:23 8

8 技術方法,驗證了SoC系統、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設計,提高了設計效率。

2017-11-17 03:06:01 13138

13138

隨著集成電路設計技術的發展和芯片集成度的提高,驗證已經成為芯片設計流程中的主要瓶頸。本文設計了一個基于FPGA的智能卡驗證平臺,并對驗證方法做了詳細闡述。本文對于雙界面智能卡芯片驗證的成功實踐

2017-11-17 16:25:01 1037

1037 利用Xilinx的FPGA設計了一個FPGA原型驗證平臺,用于無源高頻電子標簽芯片的功能驗證。主要描述了驗證平臺的硬件設計,解決了由分立元件實現模擬射頻前端電路時存在的問題,提出了FPGA器件選型

2017-11-18 08:42:22 1938

1938

,并應用到包交換芯片的仿真驗證中。仿真結果顯示,新設計的驗證平臺能通過修改隨機信號約束條件和產生隨機信號的權重值,使芯片的功能覆蓋率達到100%。

2018-01-12 11:28:24 2379

2379

復旦大學微電子學院某國家重點實驗室內部教學視頻:基于ZYNQ FPGA與PC的IP設計與驗證方案。

關鍵詞:IP設計,IP驗證,AXI總線協議,ARM,UDP傳輸,PYTHON

2019-08-06 06:16:00 1968

1968

驗證 SmartMesh IP 對于工業物聯網應用的數據可靠性

2021-03-20 11:16:15 8

8 第二章 驗證flow驗證的Roadmap驗證的目標UVM驗證方法學ASIC驗證分解驗證策略和任務的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗證的Roadmap1.ASIC芯片項目流程市場需求

2021-10-25 12:36:01 22

22 基于高通方案,羅德與施瓦茨使用R&S CMX500 5G無線綜測儀平臺驗證了10 Gbps端到端(E2E) IP數據性能。

2021-10-27 16:28:21 1755

1755

歷時4月,可支持18億門SoC全芯片驗證的英諾達硬件驗證云平臺成都中心一期成功實現滿載運行,圓滿達成云平臺一期運營所有目標!英諾達的云平臺,不同于傳統的IDC機房,機器要求高、運營復雜、專業要求極高

2021-12-17 13:54:49 1771

1771 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 種新的驗證 IP(VIP)解決方案,助力工程師迅速有效地驗證設計,以滿足最新標準協議的要求。

2022-06-06 11:18:21 2665

2665 芯片驗證就是采用相應的驗證語言,驗證工具,驗證方法,在芯片生產之前驗證芯片設計是否符合芯片定義的需求規格,是否已經完全釋放了風險,發現并更正了所有的缺陷,站在全流程的角度,它是一種防范于未然的措施。

2022-07-25 11:48:49 5263

5263 ASIC設計服務暨IP研發銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日發布FPGA-Go-ASIC驗證平臺。

2022-07-29 10:08:16 784

784 近期疫情嚴重,身為社畜的我只能在家中繼續鉆研技術了。之前寫過一篇關于搭建FIFO驗證平臺的博文,利用SV的OOP特性對FIFO進行初步驗證,但有很多不足之處,比如結構不夠規范、驗證組件類不獨立于DUT等問題。此次嘗試驗證更復雜的IP,并利用SV的更多高級特性來搭建層次化驗證平臺。

2022-08-10 11:14:49 2229

2229 半導體各領域的發展難度與日俱增,驗證可能是整個發展過程中最具挑戰性的階段。多年來,研究顯示在驗證上投入的時間和資源所占的百分比會隨著新時代芯片的出現而增加。因此整體上,驗證的快速成長超過芯片開發

2022-11-18 10:40:07 673

673 百度百科對UVM的釋義如下:通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平臺開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和接口的功能驗證環境。

2022-11-30 12:47:00 1060

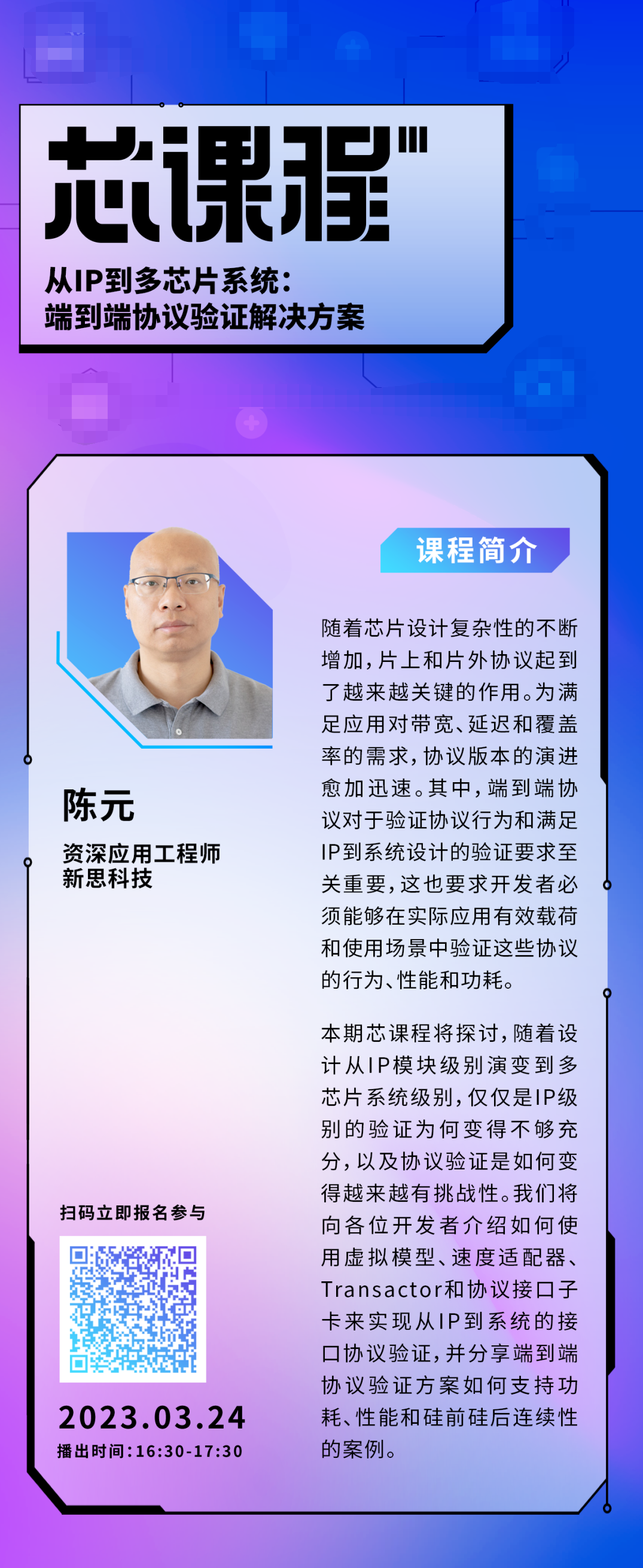

1060 ? ? ? ? 原文標題:從IP級到多芯片系統,這個驗證解決方案“一鍋端”了 文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

2023-03-17 03:35:03 304

304

在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854 在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

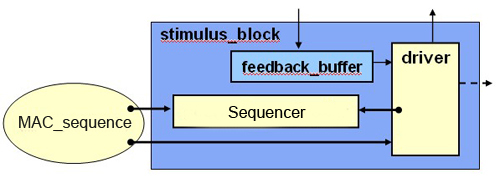

本文介紹了從一組可重用的驗證組件中構建測試平臺所需的步驟。UVM促進了重用,加速了測試平臺構建的過程。 首先對 測試平臺集成者(testbench integrator) 和 測試編寫者(test

2023-06-13 09:14:23 326

326

驗證平臺顧名思義就是為了驗證而存在的。普通意義上來說,如果是IP驗證,當驗證人員拿到設計的某模塊的RTL代碼(DUT,Design Under Test),設計文檔之后,就會根據文檔,基于自己的理解去著手寫驗證計劃,提取功能點

2023-06-15 18:12:04 745

745

IP核的開發過程中,面臨著許多關鍵技術,比如IP核的規格定義、基于接口的設計、IP核測試存取結構標準、IP核的驗證與打包等。對于IP核的驗證,主要是建立參照模型和測試平臺,然后進行回歸測試和形式驗證

2022-06-10 11:50:16 373

373

IP核的開發過程中,面臨著許多關鍵技術,比如IP核的規格定義、基于接口的設計、IP核測試存取結構標準、IP核的驗證與打包等。對于IP核的驗證,主要是建立參照模型和測試平臺,然后進行回歸測試和形式驗證

2022-06-13 11:47:03 317

317

相信很多人已經接觸過驗證。如我以前有篇文章所寫驗證分為IP驗證,FPGA驗證,SOC驗證和CPU驗證,這其中大部分是采用動態仿真(dynamic simulation)實現,即通過給定設計(design)端口測試激勵,結合時間消耗判斷設計的輸出結果是否符合預期。

2023-07-21 09:53:24 4285

4285

國芯科技(688262)。sh) 8月2日的投資者在互動平臺(interface),公司目前正在與合作伙伴一起流片驗證相關chiplet芯片高性能互聯IP技術,和上下游合作廠家積極開展包括HBM技術在內的芯片的設計與封裝技術的研究正在積極進行。”

2023-08-02 12:01:33 643

643 基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現網絡交換芯片的驗證,包括四個FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片驗證任務,多任務功能驗證。

2023-08-24 10:58:23 476

476

ic驗證是封裝與測試么?? IC驗證是現代電子制造過程中非常重要的環節之一,它主要涉及到芯片產品的驗證、測試、批量生產以及質量保證等方面。 IC驗證包含兩個重要的環節,即芯片設計驗證和芯片生產驗證

2023-08-24 10:42:13 464

464 隨著半導體技術的快速發展,集成電路芯片的復雜度日益增加,芯片設計中的驗證工作變得越來越重要。驗證的目的是確保芯片在各種工況下的功能正確性和性能穩定性。在這個過程中,testcase(測試用例)扮演著關鍵角色。本文將簡要介紹 testcase 的基本概念、設計方法和在芯片驗證中的作用。

2023-09-09 09:32:31 547

547 在芯片設計流程中,驗證環節是至關重要的一環。它直接關系到芯片的性能、可靠性和成本。

2023-09-11 09:58:49 1192

1192 任何芯片都需要把芯片劃分成更便于管理的小模塊/特性進行驗證。

2023-10-07 14:41:31 322

322 當設計的規模動輒幾十億門,系統驗證時間不斷的增加,硬件驗證系統幾乎是驗證工程師不可或缺的利器,因此對高性能硬件驗證系統提出了更多的需求。

2024-01-05 10:06:47 254

254 FPGA驗證和UVM驗證在芯片設計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區別。

2024-03-15 15:00:41 94

94 FPGA原型驗證平臺與硬件仿真器在芯片設計和驗證過程中各自發揮著獨特的作用,它們之間存在明顯的區別。

2024-03-15 15:07:03 131

131

電子發燒友App

電子發燒友App

評論