楷登電子今日正式發布Cadence? Virtuoso?定制 IC設計平臺的技術升級和擴展,進一步提高電子系統和 IC設計的生產力。新技術涉及Virtuoso 系列幾乎所有產品,旨在為系統工程師提供更穩健的設計環境和生態系統,助其實現并分析復雜芯片、封裝、電路板和系統。

2018-04-11 16:40:16 9290

9290 一套基于PSA規范的全新物聯網解決方案——Arm SDK-700系統設計套件,以用于加速安全SoC的開發。

2018-04-25 09:12:09 7015

7015 這是一個業界用于打造差異化定制芯片的領先平臺,可借助生成式 AI 技術顯著提升設計生產力; Virtuoso Studio 與 Cadence 最前沿的技術和最新的底層架構集成,助力設計工

2023-04-20 15:52:13 508

508

各位大佬好,我正在學習IC設計,對于Cadence Virtuoso這個軟件有一些入門級的小問題:我從AnaglogLib拷貝NMOS管和PMOS管到自己的library下面,打開他們的CDF參數看

2017-10-16 00:26:33

Allegro PCB信號與電源完整性軟件的又一個重點,它提供了一個全新的用戶界面,并為預布線分析環境增加了疊層感知功能。通過對本地IBIS與SPICE模型包括Cadence Virtuoso? Spectre

2018-09-10 16:37:20

不斷增加的復雜度難題的流程和方法學,從而樹立了全新PCB設計典范。 Cadence Allegro平臺是基于物理和電氣約束驅動的領先PCB版圖和互連系統。它經過升級,現在已包含了針對物理和空間約束

2018-11-23 17:02:55

板設計。Cadence 在仿真、電路圖設計、自動布局布線、版圖設計及驗證等方面有著絕對的優勢。Cadence 包含的工具較多幾乎包括了EDA 設計的方方面面。對于初學者來說,cadence的步驟確實

2019-01-22 15:47:53

介紹Cadence軟件的入門學習,包括原理圖的創建,仿真,畫版圖及后仿真等一套過程,詳細列出了步驟和圖,適合初學者

2012-03-31 21:49:31

作為流行的EDA工具之一,Cadence一直以來以其強大的功能受到廣大EDA工程師的青睞。Cadence可以完成整個IC設計流程的各個方面,如電路圖輸入(Schematic Input)、電路仿真

2012-01-04 14:56:14

SiP設計工藝快速并順暢的被采用。這個套件與Cadence之前發布的CadenceRFDesignMethodologyKit一起拓展了Cadence在無線領域RF設計方面的產品線

2008-06-27 10:24:12

Cadence工具VirtusoDracula入門介紹Cadence工具Virtuso/Dracula入門介紹.... 21.使用 Virtuso/Diva/Dracula之前的準備

2012-08-10 18:39:06

經過升級,現在已包含了針對物理和空間約束的最先進的布線技術和全新方法學。它使用了Cadence 約束管理系統,那是在整個PCB流程中提供約束管理的通用控制臺。其他升級包括支持先進串行連接設計的算法建模

2018-08-28 15:28:45

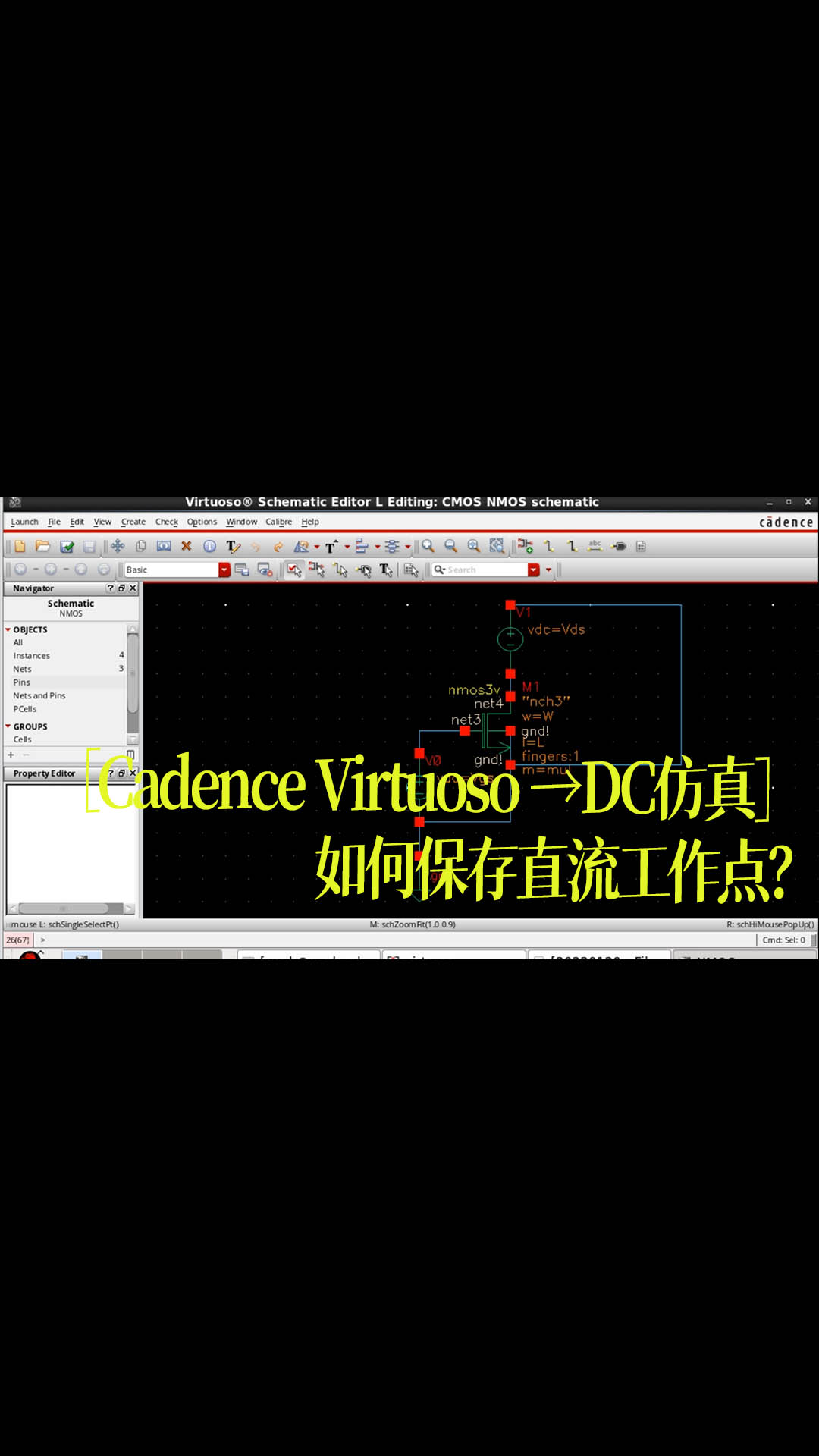

電路工作到了后期需要匯報或者寫文章需要設計原圖 ,這里整理一下Cadence設計原理圖常用導出方案。 前期工具用的好,后期處理沒煩惱,Cadence自帶工具其實很強大,只是你沒嘗試用。 仿真環境:虛擬機Linux下Cadence617 原理圖繪制工具:virtuoso

2021-01-15 07:48:05

cadence virtuoso教程? 1990-2006 Cadence Design Systems, Inc. All rights reserved.Printed

2012-08-10 18:37:59

cadence 版圖設計

2012-08-15 16:40:31

重裝了很多次、都是這樣,ic5141和ic610都用了單獨打開元件layout是可以的,但是自己畫版圖添加mos管版圖就成了方框左邊是畫的,右邊是導入的(在library 里單獨打開是mos管版圖)用的是tsmc18rf 庫,自己導入的

2013-06-02 13:42:48

/>相比Cadence 的綜合工具略為遜色然而Cadence 在仿真電路圖設計<br/>自動布局布線版圖設計及驗證等方面卻有著絕對的優勢Cadence

2008-07-12 23:11:21

我有個TI方案的原來是cadence的,是用cadence16.6做的,怎么轉成AltiumDesigner13支持的格式,按網上的提示通過AltiumDesigner13工具的導入向導來操作,選擇

2016-01-05 15:30:31

大家好,本人剛入ic行,這幾天用virtuoso畫版圖在LVS檢測過程中出現了如圖所示的報錯,有沒有哪位大神知道怎么改,麻煩賜教,很急謝謝!

2017-07-25 17:17:22

這篇博客記錄一下virtuoso中進行CMOS反相器和靜態寄存器的電路設計以及功能仿真,適合入門。還做了版圖設計,但是自己對原理不是不清楚,在此就不記錄了。virtuoso電路設計環境基本教學一

2021-11-12 06:28:47

or subcircuit, `nmos_6p0'. Either include the。。。。仿真前需要設置model libraries,這個怎么設置啊。我用的是virtuoso 6.1.7

2018-07-19 20:16:30

全新 MSP430Ware采用便利套件的形式提供,囊括了代碼范例、產品說明書及其它設計資源,適用于所有 MSP430? MCU 器件。我們將所有內容打包成簡單易用的軟件套件,使用戶能夠更輕松地配置

2018-09-26 11:03:12

分立器件版圖設計L-edit和virtuoso哪個更合適?

2023-08-07 15:15:29

Camelot技術來追蹤芯片和電路板間信號。它可讀取業界標準PCB和芯片版圖格式并將其以圖形方式顯示出來; 所支持的格式包括:OASIS、Virtuoso、Gerber、GDSII和AutoCAD繪圖交換

2018-09-10 15:56:50

(如ICC)的版圖培訓證書者優先懂得以下單項或多項版圖設計原理:模擬電路, 混合信號,標準單元對ESD有一定的了解熟悉集成電路設計的整個開發流程,熟悉CMOS工藝制程熟練掌握Virtuoso

2015-03-14 23:33:28

參數提取方案中的晶體管級寄生參數提取功能、Cadence Spectre? APS和Spectre? XPS的晶體管級仿真功能、以及最后在真實版圖上可快速分析、調試排除故障和優化的EMIR結果可視化功能

2018-09-30 16:11:32

本帖最后由 l_xy 于 2020-10-18 18:23 編輯

原標題:華為海思推出首批 HiSpark 開發套件,全面支持鴻蒙 2.0來源:IT之家 9月17日消息 上海海思與合作伙伴

2020-10-12 11:01:34

上海需要20名SRAM 版圖工程師:報價豐厚,全國各地都可以參加遠程面試1. 1年以上SRAM版圖設計相關經驗2. 熟悉SRAM版圖設計,包括SRAM/TCAM/ROM等,了解半導體工藝制程和器件

2021-08-30 13:11:14

在直接接觸的情況下,人體可感知并承受的電子脈沖頻率值在哪個區間。

2022-05-14 14:52:09

`推薦課程:張飛軟硬開源,基于STM32 BLDC直流無刷電機驅動器視頻套件http://t.elecfans.com/topic/42.html?elecfans_trackid=bbs_post全球銷量3000萬!!經典電機與機電學`

2016-01-21 13:52:16

基本都是Cadence, Synopsys, Mentor三家的產品):模擬及混合信號類(包括模擬前端設計及仿真,模擬后端設計及驗證,芯片后仿真):電路及版圖設計工具:Virtuoso (Cadence

2020-06-14 08:01:07

本帖最后由 gk320830 于 2015-3-4 19:06 編輯

在cadence ic版圖設計中tsmc.18,寬長比4/0.18的mosfet怎么畫?有多少層?每一層什么意義?

2014-10-06 08:07:57

基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖該如何去設計?怎樣去驗證一種基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖?

2021-06-22 06:12:49

可以使版圖設計流暢高效;利用Layout-XL的交叉參考可以隨時發現錯誤的連線或因疏忽造成的短路;利用DRD的實時規則檢查可以避免絕大多數違反設計規則的布圖。版圖的規則檢查可以采用Virtuoso

2018-11-26 10:56:11

PDK 套件支持我們先進的一流 IPD1 和 IPD2 工藝。此款 PDK 套件配備完全可擴展的布局參數單元 (Pcell)、先進布局實用程序以及準確的電磁 (EM) 仿真功能。此套件可應客戶要求供下載

2018-10-26 08:54:41

您是否正在使用Cadence Virtuoso進行功率放大器設計?您想運行信封跟蹤模擬嗎?包絡跟蹤是一種響應于調制的RF輸入信號的功率電平來調整功率放大器的偏置電壓以獲得更高效率的方法。已在

2019-02-21 16:18:37

。在這里可以先使用cadence的版圖與電路圖輸入工具Virtuoso來根據設計規范的要求構建建立在單管基礎上的基本單元庫,然后再根據已經驗證的算法和功能描述,利用所構建的基本單元庫來得到整個芯片的電路圖

2013-01-07 17:10:35

打開virtuoso的一些功能一、Connectivity --> Mark net 如圖所示,此功能就是可以選中相關連的層(通常大家會采用skill 來達到這一功能),這里講的是調用tech

2018-11-26 16:20:19

Virtuoso5、設計規則檢查---Assura DRC6、版圖與原理圖一致性檢查--Assura LVS7、寄生參數提取--Assura RCX8、層次化管理和后防真...

2021-11-11 07:08:32

在下微電子專業,玩過cadence的IC設計套件和Orcad,現在公司做pcb設計,用concept hdl畫原理圖,用allegro畫版圖.在學習concept hdl過程中遇到了如圖的問題:左邊

2012-12-06 17:47:16

模擬IC設計工程師-西安1.參與IC產品的框架設計和Spec定義;2.獨立負責產品電路設計及仿真驗證工作,指導后端工程師完成版圖設計;3.協助完成測試方案,提供測試支持,并對測試結果進行分析;4.

2017-07-13 17:42:23

相關專業,碩士及以上學歷;

具備扎實的器件與電路基礎,熟悉半導體器件的物理特性、寄生和版圖要求等;

熟練運用Cadence模擬電路設計工具,如Virtuoso、Spectre等;

熟悉BGR、LDO

2023-11-30 17:09:44

工藝; 4、熟悉模擬以及射頻電路版圖設計與布線技巧; 5、熟練掌握主流EDA軟件,如Virtuoso等; 6、能吃苦,喜上進,有團隊精神者優先。

2015-07-03 17:59:37

; 5、支持應用團隊對芯片的使用。 崗位要求 : 1、微電子或相關專業畢業,本科以上學歷2、熟悉模擬集成電路設計流程,熟悉仿真與測試;3、掌握相關設計工具,如Cadence Virtuoso與ADS,及其

2015-07-03 17:58:39

SpringSoft Laker定制版圖系統支持TSMC跨平臺制程設計套件

IC設計軟件全球供貨商SpringSoft, Inc.近日宣布,Laker定制版圖自動化系統(Custom Layout Automation Syste

2009-07-30 08:11:20 1005

1005 芯邦采用Cadence Incisive Xtreme III系統提升SoC驗證實效

全球電子設計創新領先企業Cadence設計系統公司今天宣布,位于中國深圳的、無晶圓廠集成電路設計領先企業芯邦科

2010-03-02 10:32:47 573

573 電子設計創新企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,中國科學院計算技術研究所(簡稱計算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系統,來加速其下一代6400萬門以上龍芯3號高級多

2011-05-27 10:49:34 646

646 Giantec最近采用Cadence軟件設計并成功流片了一款用于低功耗微控制器的存儲器產品,這款低功耗微控制器應用于智能卡、智能電表和消費電子產品。

2011-09-22 18:08:05 896

896 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence? Virtuoso?統一定制/模擬(IC6.1)以及Encounter?統一數字流程生產其混合信號芯片。

2011-09-27 11:06:26 1483

1483 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

2013-07-10 13:07:23 842

842 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)今天宣布,歷經廣泛的基準測試后,半導體制造商聯華電子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence? “設計內”和“簽收”可制造性設計(DFM)流程對28納米設計進行物理簽收和電學變量優化。

2013-07-18 12:02:09 905

905 美國加州圣何塞,2014年9月30日 ─ 全球知名的電子設計創新領導者Cadence設計系統公司(NASDAQ: CDNS)今日宣布其豐富的IP組合與數字和定制/模擬設計工具可支持臺積電全新的超低功耗(ULP)技術平臺。

2014-10-08 19:24:35 907

907 IC design 集成電路的設計流程以及cadence的簡介,使用方法和入門須知。

2016-03-14 14:11:33 25

25 4月15日,中國上海—楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布Cadence? Virtuoso? 版圖依賴效應(Layout-Dependent Effects

2016-04-15 10:09:07 1939

1939 CADENCE射頻SiP方法學套件加速無線應用設計

2017-01-14 12:50:17 25

25 2017年4月18日,中國上海 – 楷登電子(美國Cadence公司,NASDAQ: CDNS)今日正式發布針對7nm工藝的全新Virtuoso? 先進工藝節點平臺。通過與采用7nm FinFET

2017-04-18 11:09:49 1165

1165 中國上海,2017年6月12日 – 楷登電子(美國Cadence公司,NASDAQ: CDNS)今日發布全新Cadence? Virtuoso? System Design Platform

2017-06-13 14:26:28 2937

2937 Kit) 推向中國射頻電路設計市場,中芯國際將發展支持 Cadence 射頻方案的工藝設計套件 (process-design kit) 并于2006年底前完成測試芯片。 客戶將可于2006年底得到0.18微米的CMOS射頻工藝設計套件(process-designkit)。

2017-12-13 14:21:01 1568

1568 Virtuoso快捷鍵總結 入門級

2017-12-21 17:32:14 0

0 Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面,包括ASIC 設計、FPGA 設計和PCB 板設計。Cadence 在仿真、電路圖設計、自動布局布線、版圖設計及驗證等方面有著絕對的優勢。Cadence 包含的工具較多幾乎包括了EDA 設計的方方面面。

2018-02-07 13:44:36 18492

18492 Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面,包括ASIC 設計、FPGA 設計和PCB 板設計。Cadence 在仿真、電路圖設計、自動布局布線、版圖設計及驗證等方面

2018-02-07 17:11:21 26525

26525

版圖驗證是指采用專門的軟件工具,對版圖進行幾個項目的驗證,例如是否符合設計規則?版圖和電路圖是否一致?版圖是否存在短路、斷路及懸空的節點?借助于計算機和Cadence軟件的功能,對版圖設計進行高效而全面的驗證。經過版圖驗證后,一次流片成功率大大提高。

2018-04-20 15:56:47 0

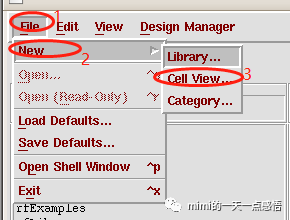

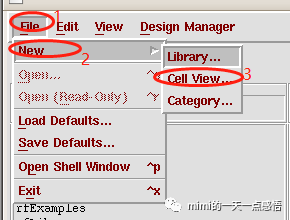

0 本文檔的主要內容介紹的是Cadence軟件的介紹和CMOS集成電路的版圖設計詳細資料內容包括:1. Cadence軟件簡介 2. 建立新庫和新文件 3. 電路圖編輯窗 4. 電路圖的輸入及編輯 5. 電路圖的層次化設計

2018-06-15 08:00:00 0

0 采用Virtuoso電路原理圖編輯器與Virtuoso版圖套件將總周轉時間縮短30-50%:Virtuoso電路原理圖編輯器內置種類齊全的的,用于各種仿真的,定義明確的元件庫,可以加快模擬電路

2018-08-08 18:11:11 1324

1324 本文檔的主要內容詳細介紹的是Cadence設計軟件的教程免費下載包括了:實驗 1:Cadence 系統編輯環境設置與基本操作,實驗 2:二與非門電路原理圖設計實驗 3:數、模混合集成電路原理圖

2020-05-15 08:00:00 0

0 cadence 公司 IC5141 工具主要包括集成平臺 design frame work II、原理圖編輯工具 virtuoso schematic editor、仿真工具、版圖編輯工具

2020-07-21 08:00:00 3

3 應用提供優化的性能和吞吐量。面向 PCIe 6.0 的 Cadence IP 的早期采用者現在可以使用相應的設計套件。 Cadence 的這款 5 納米 PCIe 6.0 PHY 測試芯片在所有 PCIe 速率下都表現出了出

2021-10-26 14:28:00 4024

4024 Virtuoso5、設計規則檢查---Assura DRC6、版圖與原理圖一致性檢查--Assura LVS7、寄生參數提取--Assura RCX8、層次化管理和后防真...

2021-11-06 17:21:01 0

0 這篇博客記錄一下virtuoso中進行CMOS反相器和靜態寄存器的電路設計以及功能仿真,適合入門。還做了版圖設計,但是自己對原理不是不清楚,在此就不記錄了。virtuoso電路設計環境基本教學

2021-11-07 10:21:01 36

36 版圖驗證工具不僅要支持扁平化驗證,而且要支持層次化驗證。扁平化驗證是版圖驗證工具的基礎;層次化驗證充分利用版圖層次,可以有效避免重復報錯和提高處理版圖的速度。對于大規模版圖,通常還采用并行技術以加速版圖驗證效率。

2022-08-29 11:00:32 1861

1861 Virtuoso Layout Suite 支持現有版圖在給定工藝技術上的復用,利用自定義布局和布線自動化技術,在新的工藝技術上快速重建移植后的版圖。

2022-10-28 10:26:05 691

691 Cadence 射頻集成電路解決方案支持 Cadence 智能系統設計(Intelligent System Design)戰略,助力實現系統級芯片(SoC)的卓越設計。

2022-11-03 14:18:50 835

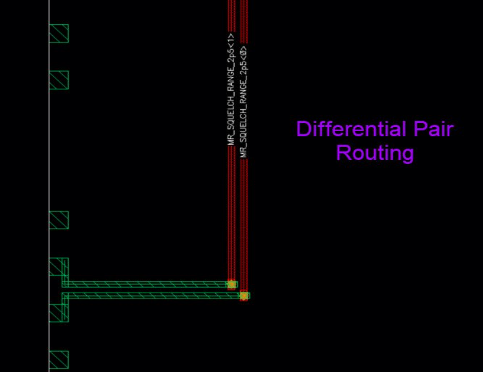

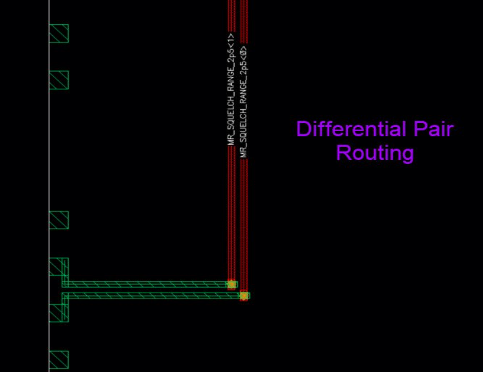

835 交互式路由允許您在自動路由之前完成關鍵網絡,并在自動路由后完成未布線的不完整網絡。Virtuoso 交互式和輔助路由功能允許您在 Virtuoso 環境中以交互方式路由連接,以滿足關鍵的設計約束和規則。在所有工藝節點上啟用交互式和自動布線功能,包括最先進的工藝技術。

2023-04-20 10:58:23 2071

2071

Cadence LPDDR5X IP 現已支持客戶使用,該 IP 采用全新高性能、可擴展的自適應架構,并依托于 Cadence 久經驗證且大獲成功的 LPDDR5 和 GDDR6 產品線。

2023-04-21 12:46:31 1100

1100 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的節點到節點設計遷移流程,能兼容所有的臺積電先進節點

2023-05-06 15:02:15 801

801 了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-06-13 12:15:02 557

557

●?Samsung Foundry 有眾多 PDK 系列,可搭配 Virtuoso Studio 用于簡化模擬、定制和射頻設計,最高支持 SF 2nm 技術 ●?Virtuoso Studio

2023-06-30 10:08:30 681

681 內容提要 1 輕松實現節點到節點的設計和 layout 遷移 2 將定制/模擬設計遷移速度提升 2 倍 3 Cadence Virtuoso Studio 針對所有 Samsung Foundry

2023-07-04 10:10:01 471

471 了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-07-11 12:15:02 241

241

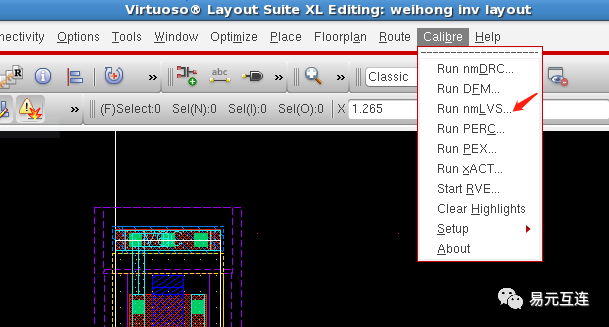

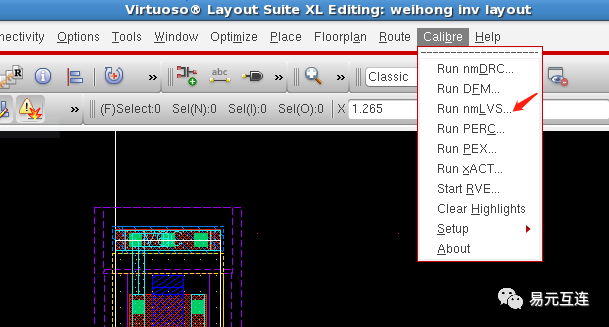

Siemens的Calibre是業內權威的版圖驗證軟件,被各大Foundry廠廣泛認可。用戶可以直接在Virtuoso界面集成Calibre接口,調用版圖驗證結果數據,使用起來極為方便。

2023-08-24 11:14:13 1980

1980

了新一代定制設計平臺 Cadence Virtuoso Studio ,該平臺采用全新的底層架構,以獨特的方法來管理設計流程,可將當今大型設計的設計同步吞吐量提升 3 倍,是面臨大型復雜項目和有短時間

2023-09-01 12:20:01 413

413

Cadence Virtuoso定制設計平臺的一套全面的集成電流(IC)設計系統,能夠在多個工藝節點上加速定制IC的精確芯片設計,其定制設計平臺為模擬、射頻及混合信號IC提供了極其方便、快捷而精確的設計方式。

2023-09-11 15:14:16 3199

3199

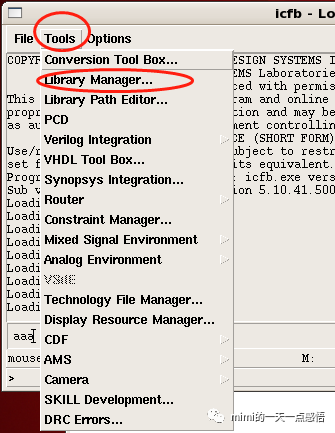

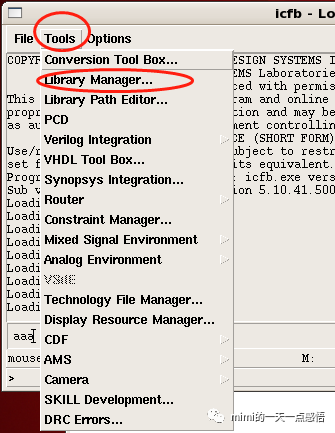

Library Manager:庫管理器。它主要用于項目中庫(Library)、單元(Cell)及視圖(View)的創建、添加、復制、刪除和組織

2023-09-11 15:38:17 1972

1972

菜單欄(菜單欄的展開Tool、Design、Windows、Create、Edit、Verify、Connectivity、Option、命令表達)

2023-09-11 15:44:44 5237

5237

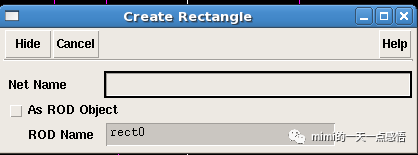

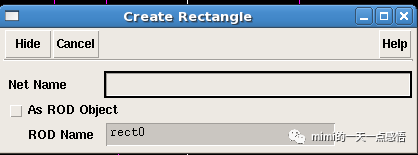

創建矩形命令用于創建矩形。當創建一個矩形時,按F3會出現選項來對矩形進行命名。其中,“Net Name”為對所創建的矩形進行命名

2023-09-11 16:02:19 9272

9272

一個版圖設計好以后,產生的錯誤可能是多連了一根鋁線造成的Short,或者是少連了幾根鋁線造成的Open,這樣的低級錯誤對芯片來說都是致命的,因此編輯好的版圖要通過LVS(Layout Versus Schematic)與原理圖進行核對驗證。然后再進行常規的DRC(Design Rule Check)。

2023-10-02 15:08:00 1738

1738

● AI 驅動的 Cadence Virtuoso Studio 助力 IC 設計在 TSMC 的制程技術之間實現遷移時自動優化電路 ●? 新的生成式設計技術可將設計遷移時間縮短

2023-09-27 10:10:04 301

301 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布與臺積電(TSMC)合作將新推出的 Cadence Virtuoso Studio 集成到 TSMC N16 毫米波設計參考流程

2023-09-28 10:10:02 533

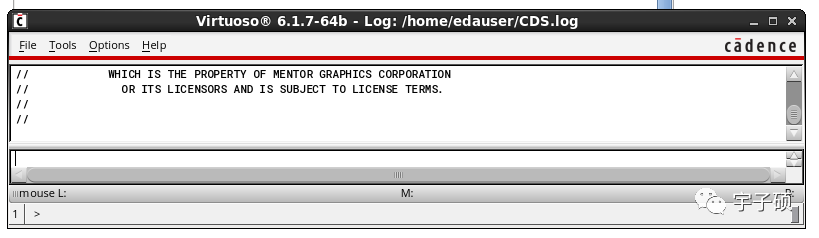

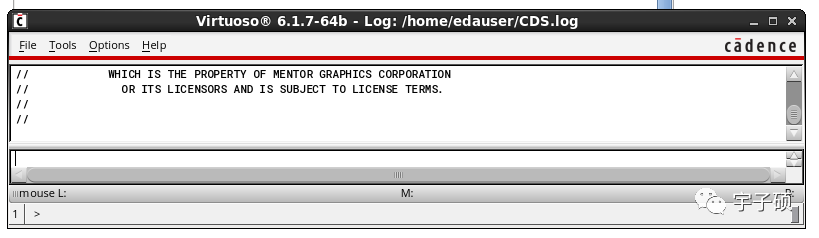

533 首先,在相應終端下鍵入virtuoso,啟動后出現以下窗口。

2023-10-18 15:47:46 742

742

基于 Cadence 30 年的行業知識和領先地位,全新人工智能定制設計解決方案 Virtuoso Studio 采用了多項創新功能和新的基礎架構,實現無與倫比的生產力,以及超越經典設計界限的全新集成水平。在本文中,您將了解優異的模擬設計工具如何變得更好,并助您解決挑戰性的設計問題。

2024-01-09 12:22:02 445

445

電子發燒友App

電子發燒友App

評論