作為芯片行業(yè)從業(yè)者,估計(jì)很多人最怕聽到的就是一些話是:芯片“可靠性”出問題了。對于5G射頻芯片,評估基本性能都已經(jīng)非常復(fù)雜,出了“可靠性”問題更是會讓人膽戰(zhàn)心驚。

如果“可靠性”評估不徹底,器件在終端使用中出現(xiàn)失效,則會影響產(chǎn)品功能,嚴(yán)重時可能造成不可挽回的慘痛后果。

但如果對“可靠性”的評估不科學(xué),層層加碼、過度苛責(zé),又會嚴(yán)重影響項(xiàng)目進(jìn)度,使成本、時間急劇上升。

為了科學(xué)的解釋和評估電子元器件的可靠性,伴隨著1947年半導(dǎo)體晶體管的發(fā)明和大規(guī)模應(yīng)用,逐漸興起了一個學(xué)科:可靠性工程。

可靠性工程是提高元器件在整個生命周期內(nèi)可靠性的一門工程技術(shù)學(xué)科,涉及設(shè)計(jì)、分析、試驗(yàn)等各個產(chǎn)品開發(fā)過程。可靠性工程于1950年前后在美國興起,伴隨著半導(dǎo)體技術(shù)的進(jìn)步,已經(jīng)發(fā)展了70年。本文借可靠性工程的相關(guān)理念和方法,和大家就芯片的可靠性設(shè)計(jì)與評估理念做一個討論。

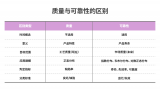

? 可靠性工程中的幾個重要理念??

失效時間:性能退化是基本物理規(guī)律

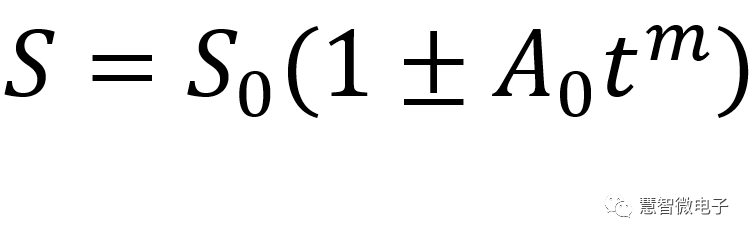

正如人有生老病死,自然界中物體的特性也會逐漸退化。這也符合熱力學(xué)第二定律,熵增定律的表現(xiàn):孤立不可逆系統(tǒng)的熵(無序程度),會隨著時間增加而增加。 ? 既然每個期間都會性能退化,那器件可以使用的時間究竟是多少呢?于是,失效時間(Timeto Failure,TF)的概念就被引入了進(jìn)來。 ? 在可靠性工程中,認(rèn)為器件參數(shù)S是與時間t相關(guān)的函數(shù)。性能參數(shù)S與初始性能S0、時間t的關(guān)系,可以用級數(shù)的方式表示出來(m為冪律指數(shù)): ?

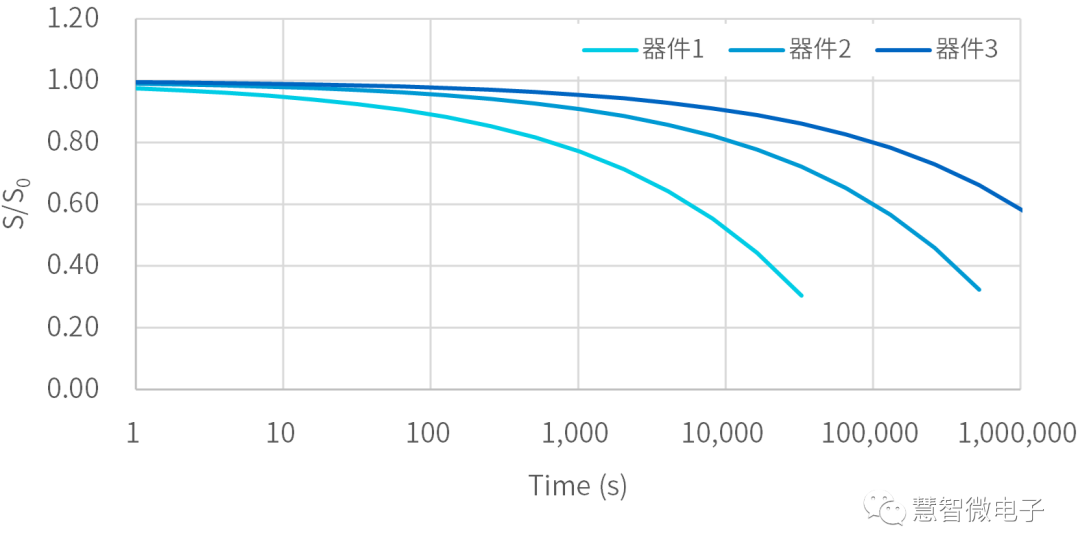

通過以上公式可以看到,參數(shù)S會隨時間變化而變化,變大與變小受正負(fù)號控制,變化的幅度受A0控制。 ? 當(dāng)器件參數(shù)S隨時間變化而減小時,假設(shè)可以在不同時間將器件參數(shù)均采集出來,就可以得到以下器件參數(shù)S隨時間變化的曲線: ?

圖:器件參數(shù)S隨時間變化而減小

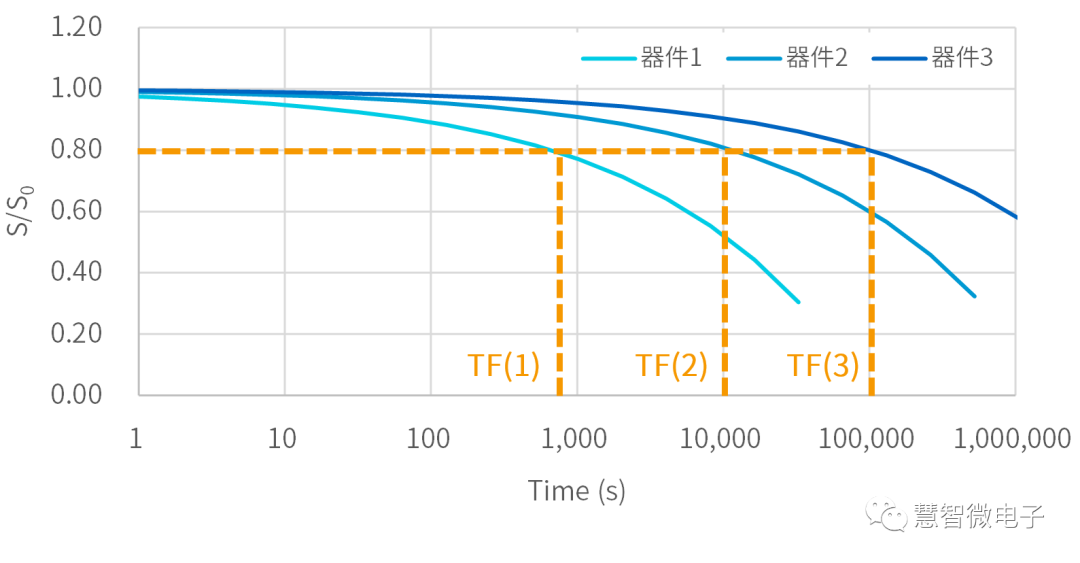

得到以上參數(shù)后,如果將S變化原有值的80%作為臨界值,就可以得到不同器件失效時對應(yīng)的時間。這個時間就定位為失效時間(Time to Failure,TF)。 ?

圖:器件失效時間(TF)的定義 ?

加速退化:可控時間內(nèi)測試出器件壽命

如前節(jié)所述,器件性能的退化是隨時間演進(jìn)而發(fā)生的。對于消費(fèi)類產(chǎn)品來說,一般生命周期長達(dá)數(shù)年。在產(chǎn)品推出來之前,先做完整個生命周期的可靠性驗(yàn)證是不現(xiàn)實(shí)的,更不用說一些工業(yè)級、車規(guī)級的芯片需要10年以上的可靠性壽命。 ? 于是,加速退化的概念就被引入進(jìn)來。 ? 加速退化(Accelerated Degradation)是指通過提高器件測試條件的應(yīng)力、或者升高濕度,來加快器件退化的過程。其目的是在不改變失效發(fā)生物理機(jī)理情況下,縮短失效測試的周期。 ?

加速因子:確定加速的速度

加速測試確實(shí)可大大減少可靠性測試所需要的時間,但究竟可以加速到多快呢?加速需要采用的測試條件應(yīng)力、溫度與加速時間之間又是什么關(guān)系?這里就有了加速因子的概念。

加速因子(Accelerated Factor)是加速測試?yán)碚撝械闹匾拍睿侵冈诩铀賾?yīng)力條件下快速采集器件失效時間數(shù)據(jù),并將這些數(shù)據(jù)外推到器件正常使用環(huán)境,得到正常使用下的失效時間。 ? 需要說明的是,采用加速模型進(jìn)行加速老化實(shí)驗(yàn)時,一定要確保兩點(diǎn):

加速必須是均勻的

不能改變失效的物理機(jī)制

第一點(diǎn)中,加速均勻性的要求是加速模型計(jì)算中的需求。第二點(diǎn)“不能改變失效物理機(jī)制”同樣需要注意,需要確保不因?yàn)閰?shù)應(yīng)力過大,而出現(xiàn)其他失效問題(如瞬間失效燒毀等)。 ? 設(shè)計(jì)合理的加速測試環(huán)境需要對器件的失效機(jī)理有著深入的分析。在集成電路產(chǎn)品中,典型的失效機(jī)理包含[2]:

電遷移

應(yīng)力遷移

腐蝕

熱循環(huán)疲勞

時間相關(guān)介電擊穿

熱載流子注入

離子鍵斷裂

加速測試方法需要根據(jù)以上失效機(jī)理進(jìn)行合適設(shè)計(jì)。

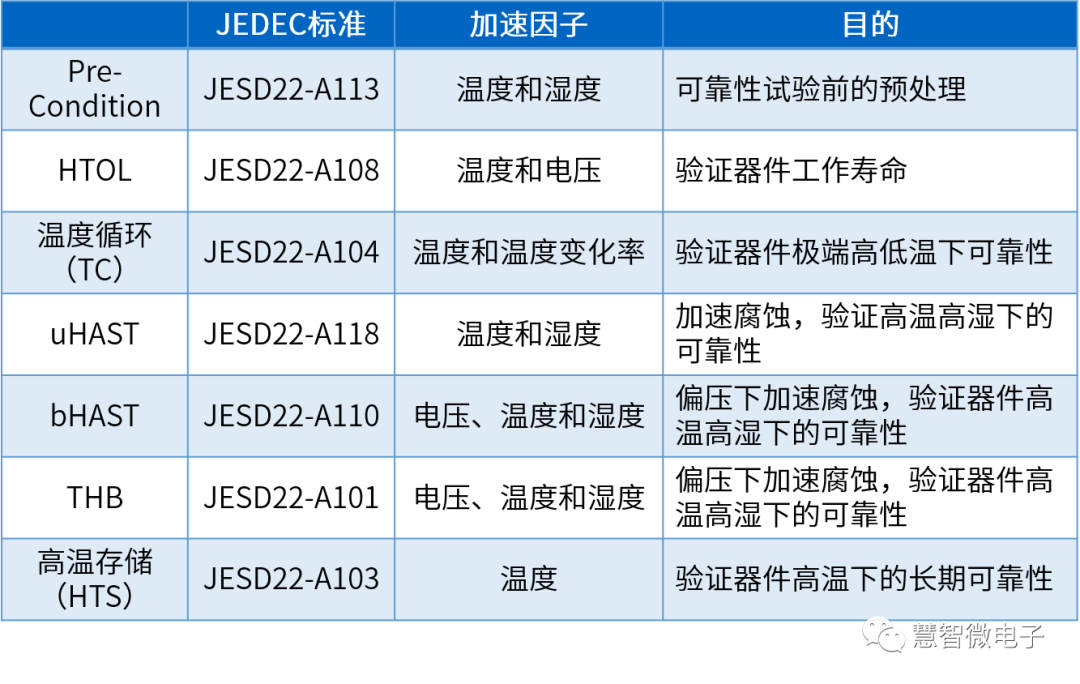

常見的加速退化方法

加速因子與加速時間有對應(yīng)關(guān)系是較為容易理解的,但要精準(zhǔn)推導(dǎo)出二者的數(shù)學(xué)聯(lián)系就較為復(fù)雜了。 ? 于是,行業(yè)組織這時就發(fā)揮出了較大的作用。 ? 1958年,由半導(dǎo)體器件制造廠商、設(shè)計(jì)廠商以及終端應(yīng)用廠商等,共同成立了行業(yè)標(biāo)準(zhǔn)制定組織JEDEC(Joint Electron Device EngineeringCouncil,聯(lián)合電子器件委員會),用于制定統(tǒng)一的產(chǎn)業(yè)標(biāo)準(zhǔn)制定。 ? 根據(jù)器件的老化機(jī)理,JEDEC定義了系列的加速測試方法。常見的加速測試方法如下。 ?

圖:常見的加速測試方法

JEDEC所定義的加速測試方法已成為電子器件的標(biāo)準(zhǔn)測試方法。在實(shí)際產(chǎn)品交付中,需要將以上可靠性報告,伴隨產(chǎn)品一起向客戶交付。 ?

浴盆曲線模型:將失效分時期看待

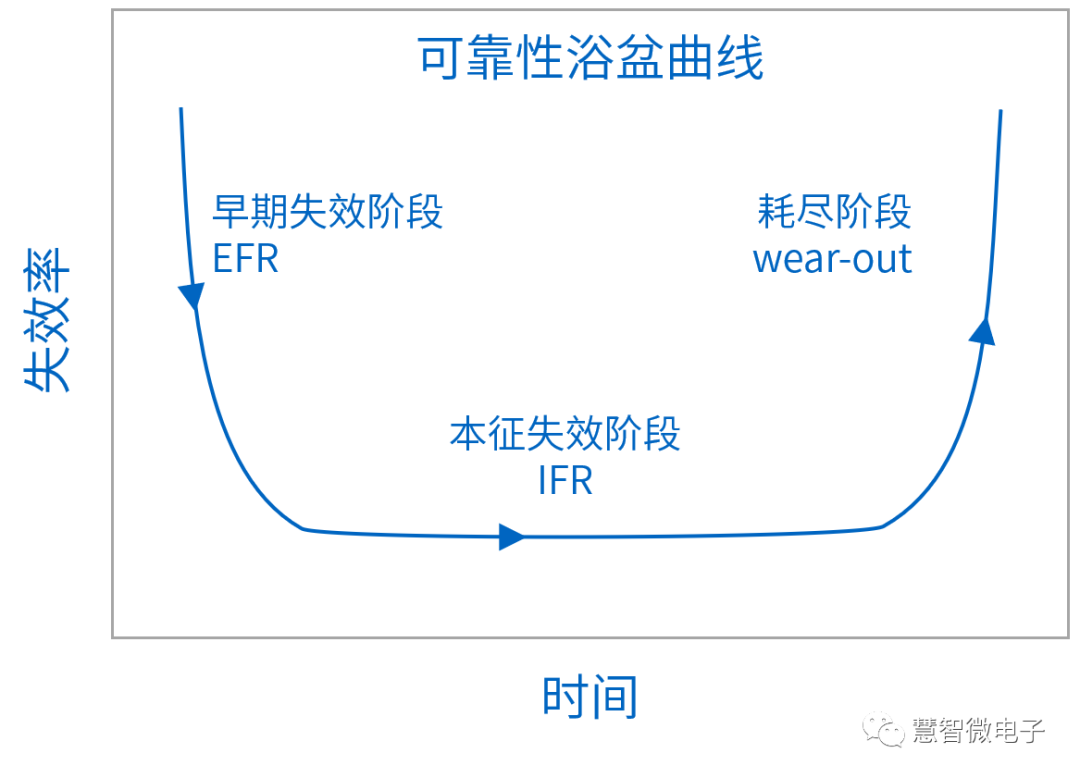

為了理解不同時期內(nèi)器件失效發(fā)生的物理機(jī)理,可靠性工程中引入著名的“浴盆曲線”概念。 ? 浴盆曲線(Bathtub Curve)認(rèn)為一般器件失效有三個明顯不同的階段:

早夭期(Early Failure Rate,EFR):在器件早期使用階段發(fā)生,失效率較高。這個時期主要的失效原因是器件生產(chǎn)時的嚴(yán)重缺陷造成;

本征失效期(Intrinsic FailureRate,IFR):這個階段是由于器件內(nèi)部材料內(nèi)部存在微小缺陷造成的;

耗盡期(Wear-out):這個階段器件的性能已經(jīng)退化,達(dá)到使用的末期。此時失效由于器件的正常退化造成。

圖:可靠性浴盆曲線

可靠性浴盆曲線反應(yīng)了失效的一般規(guī)律,甚至可以用生物的生命周期來類比:一般新生兒在出生的24小時內(nèi),需要醫(yī)生格外關(guān)注,如果新生兒有一些出生時的缺陷,則在這個時期很容易出現(xiàn)生命危險;而經(jīng)過一年之后一直到70歲左右,這個時期內(nèi)死亡率較低并且趨于平緩;而到70歲之后,人類的器官開始出現(xiàn)消耗殆盡的現(xiàn)象。 ? 對于集成電路來說,早夭期(EFR)可能會延續(xù)一年的時間。為了剔除存在缺陷的產(chǎn)品,使之不至于流向客戶造成高的失效率,集成電路會采用讓產(chǎn)品試運(yùn)行一段時間,來清除有先天缺陷產(chǎn)品,這個清除的過程,被稱為Burn-in(老化)。 ? 將器件做長達(dá)一年的Burn-in是不現(xiàn)實(shí)的。所以,一般會用到前一節(jié)提到的“加速退化”的方法,提升器件工作時的電壓或其他工作條件的應(yīng)力,使失效時間縮短到幾小時、幾分鐘,甚至幾秒鐘。與加速退化的分析類似,具體所加應(yīng)力大小與對應(yīng)時間的關(guān)系,需要根據(jù)器件的失效各類來確定。 ? Burn-in是一種對產(chǎn)出產(chǎn)品進(jìn)行100%篩選的非破壞性實(shí)驗(yàn),目的是將早夭產(chǎn)品剔除。由于實(shí)驗(yàn)對應(yīng)芯片工作的時長是早期失效階段(比如一年正常工作時間),所以并沒有使器件進(jìn)入耗盡期而發(fā)生性能的退化失效,也不會明顯減少器件使用壽命(器件的壽命通常為數(shù)年)。 ? 另外需要說明的是,Burn-in是減少早期失效的一種方式,需要在每顆產(chǎn)品出廠前進(jìn)行全數(shù)測試。如果工藝和設(shè)計(jì)電路成熟,有數(shù)據(jù)表明器件早期失效率穩(wěn)定,也可以在測試中去掉Burn-in的測試。 ?

統(tǒng)計(jì)概念的引入:評估性能波動的影響

失效時間定義了器件性能隨時間的變化。在大批量使用時,還會存在不同器件間性能波動的問題。

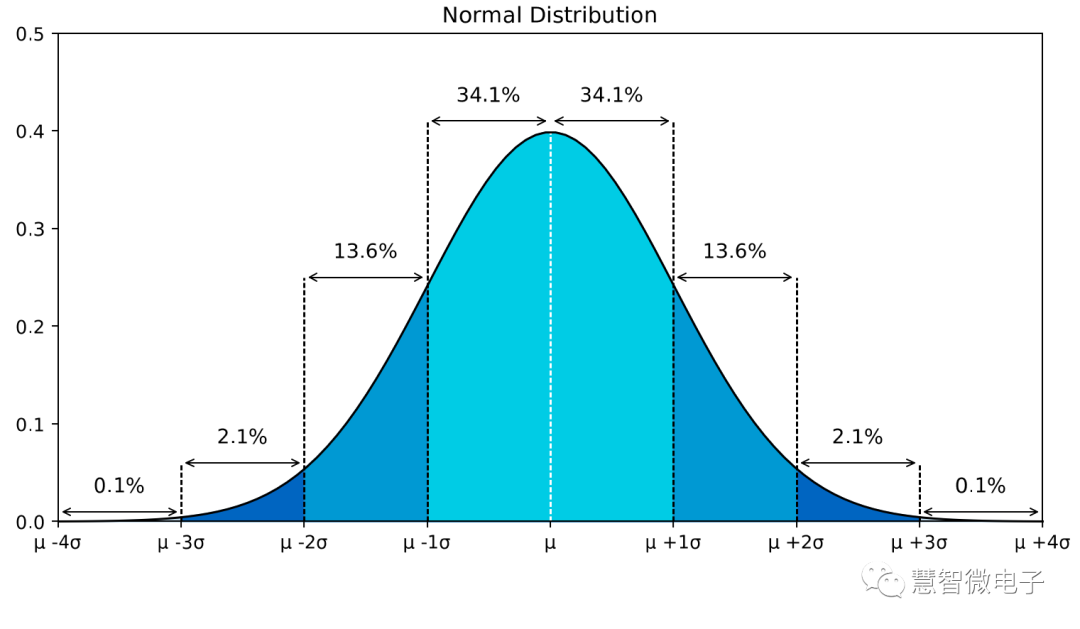

既然不同器件之間的性能是不完全一致的,那如何衡量波動和確定卡控門限(Limit)呢?于是,統(tǒng)計(jì)的概念就被引入了進(jìn)來。 ? 正態(tài)分布(Normal Distribution)是數(shù)學(xué)家們在18世紀(jì)所發(fā)現(xiàn)的一種統(tǒng)計(jì)規(guī)律,著名高斯在1809年對其進(jìn)行了理論推導(dǎo)與完善,所以正態(tài)分布又被稱為高斯分布。 ? 正態(tài)分布的作用不止是揭示了一個數(shù)學(xué)現(xiàn)象,而是在實(shí)際工程應(yīng)用中有著重要的作用。

圖:正態(tài)分布及其對應(yīng)區(qū)間的概率

正態(tài)分布中兩個重要參數(shù)是均值和標(biāo)準(zhǔn)差。均值決定了數(shù)據(jù)的平均數(shù),標(biāo)準(zhǔn)差決定了數(shù)據(jù)的分散程度。在正態(tài)分布中:

68%的數(shù)據(jù)在平均值1個標(biāo)準(zhǔn)差內(nèi);

95%的數(shù)據(jù)在平均值2個標(biāo)準(zhǔn)差內(nèi);

99.7%的數(shù)據(jù)在平均值3個標(biāo)準(zhǔn)差內(nèi)

一旦根據(jù)統(tǒng)計(jì)分布得出某一變量的均值和標(biāo)準(zhǔn)差后,就可以根據(jù)高斯分布,計(jì)算出任意給定區(qū)間內(nèi)的概率分布。所以,此種統(tǒng)計(jì)的方法可以用來計(jì)算給定上下限的良率,或者推測性能波動帶來的ppm失效率。

? 高可靠性芯片的設(shè)計(jì)和評估??

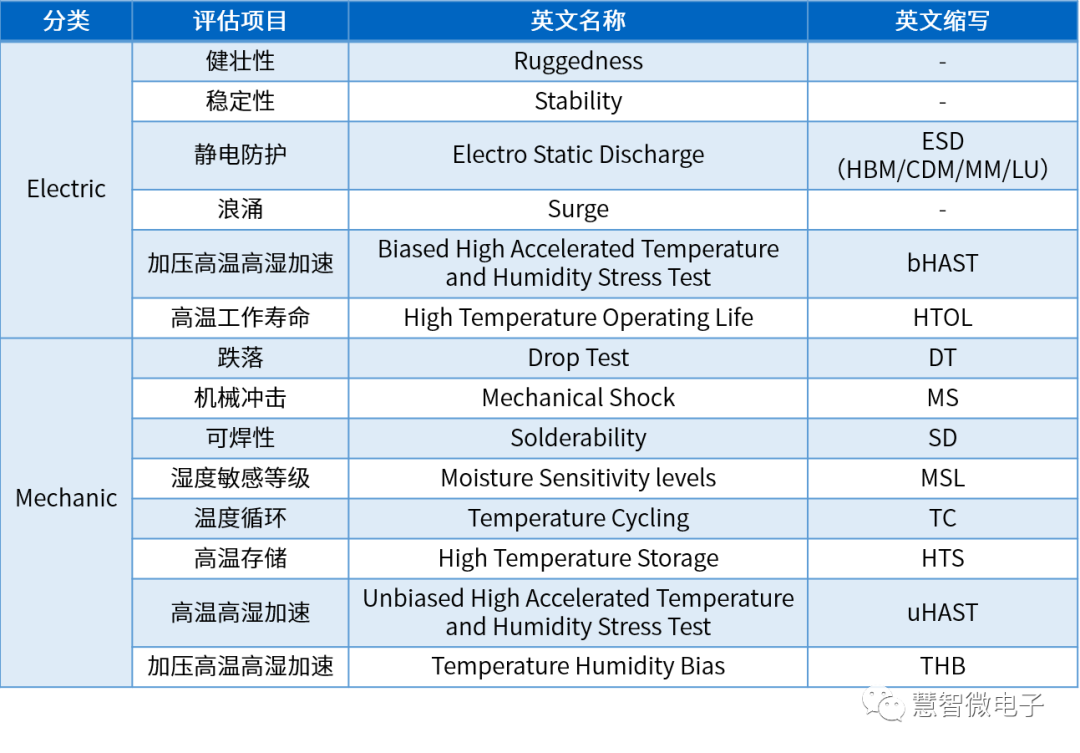

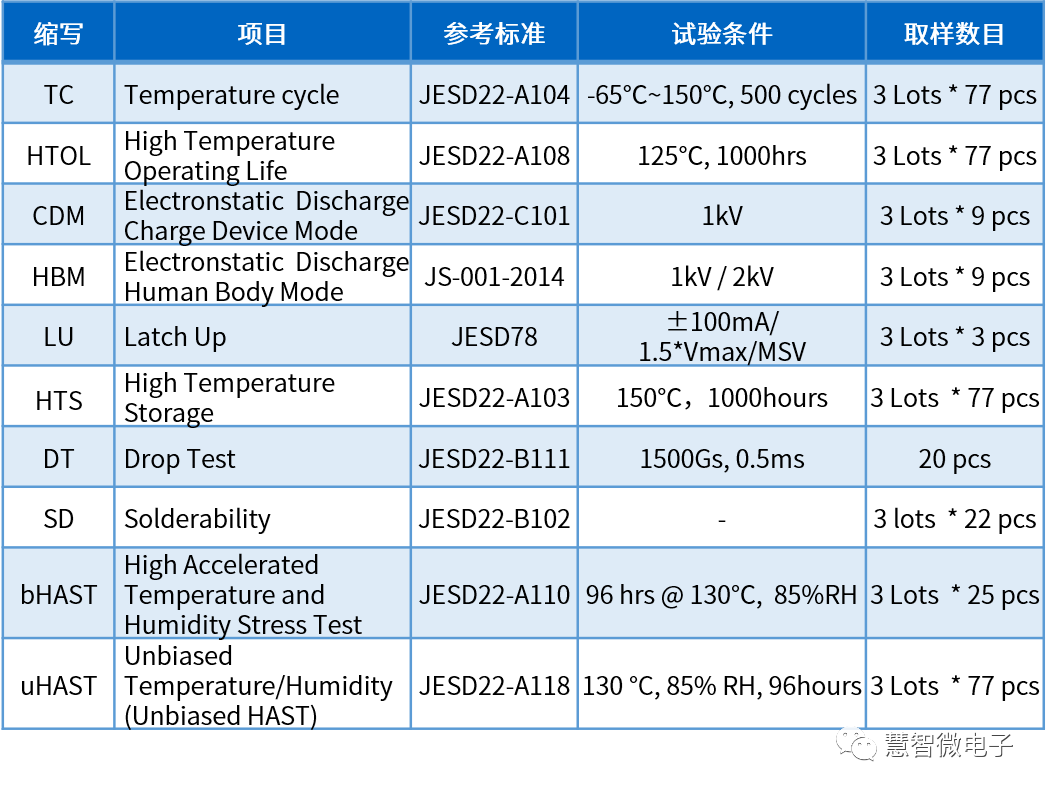

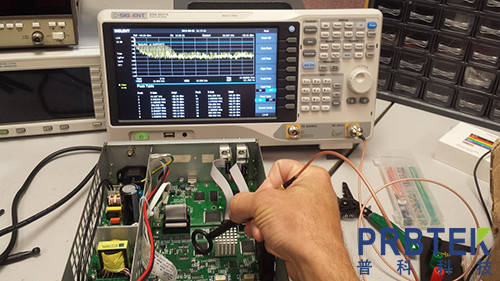

基于以上可靠性工程理念,在芯片產(chǎn)品開發(fā)過程中加入高可靠性設(shè)計(jì)與評估。 ? 根據(jù)芯片是否帶電測試,芯片的可靠性主要分為Electric類與Mechanic類兩類。射頻前端產(chǎn)品常見的可靠性測試內(nèi)容如下。 ?

圖:常見的可靠性測試項(xiàng)目

以上可靠性測試項(xiàng)根據(jù)產(chǎn)品的不同需求,選擇進(jìn)行評估。部分測試目的相同的測試項(xiàng)(如THB與bHAST),可以二選一進(jìn)行測試。 ? ?

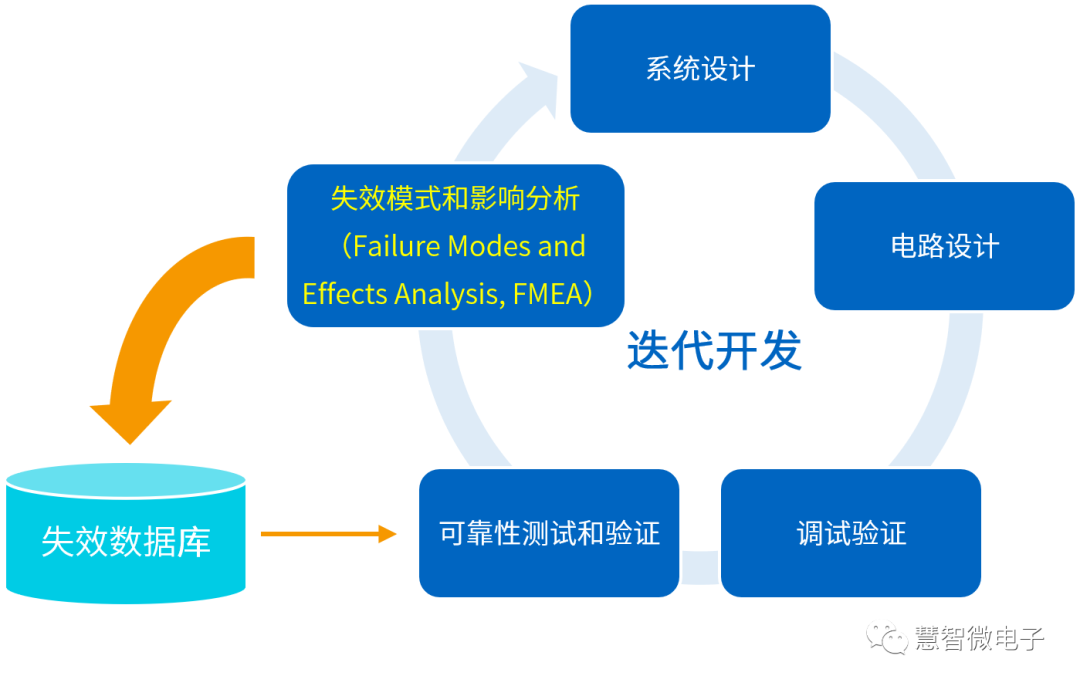

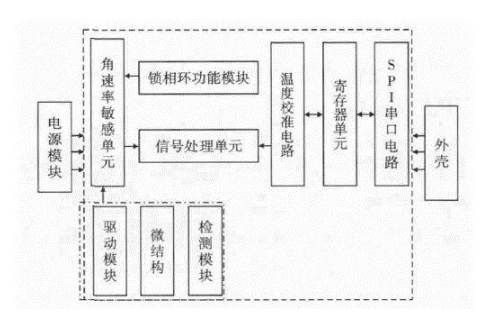

高可靠芯片的設(shè)計(jì)

“可靠性是設(shè)計(jì)出來的,不是測試出來的”是高可靠芯片設(shè)計(jì)中的重要理念。實(shí)現(xiàn)滿足以上可靠性需求的高可靠模組芯片,必須要在設(shè)計(jì)之初就對芯片的高可靠性加以考慮。 ? 常見的高可靠性芯片設(shè)計(jì)思路是FMEA(FailureModes and Effects Analysis)方法,下圖為典型的包含F(xiàn)MEA的迭代開發(fā)流程。 ?

圖:包含F(xiàn)MEA的迭代開發(fā)流程

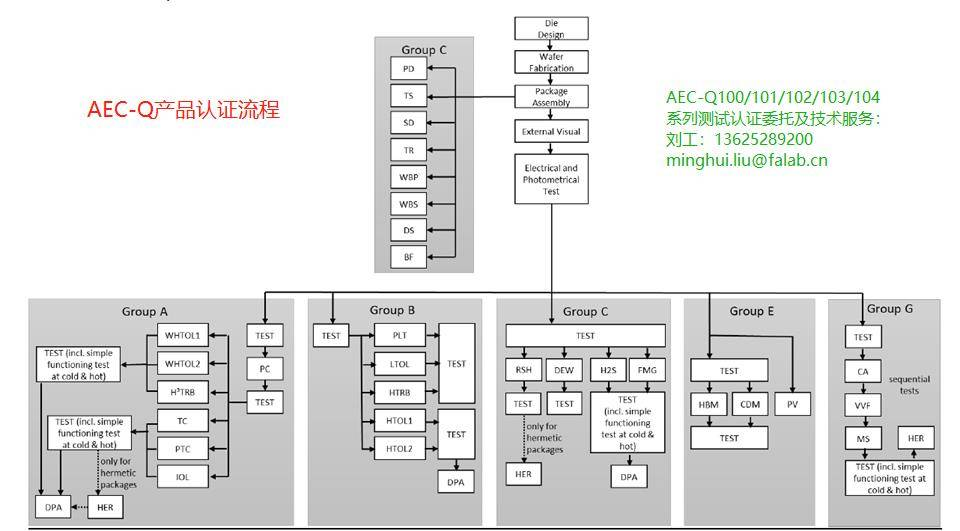

高可靠芯片的驗(yàn)證

芯片的可靠性驗(yàn)證一般遵循一定的測試標(biāo)準(zhǔn),常見的測試標(biāo)準(zhǔn)為前一章節(jié)提到的JEDEC標(biāo)準(zhǔn),另外還有車規(guī)產(chǎn)品驗(yàn)證的AEC-Q系列標(biāo)準(zhǔn)。 ? 這些標(biāo)準(zhǔn)中建立起標(biāo)準(zhǔn)的測試方法。同時,在器件選取數(shù)量、判定標(biāo)準(zhǔn)上也做了明確規(guī)定。如下為JEDEC相關(guān)測試項(xiàng)及測試標(biāo)準(zhǔn)。高可靠的芯片設(shè)計(jì)必須完全通過以下測試。 ?

圖:JEDEC所規(guī)定的測試項(xiàng)及條件(部分)

? ? 總? ?結(jié)???

高質(zhì)量芯片是先進(jìn)的設(shè)計(jì)能力、優(yōu)質(zhì)的流程管理、完整的可靠性評估帶來的綜合結(jié)果。開發(fā)高質(zhì)量芯片,對設(shè)計(jì)企業(yè)的綜合能力和開發(fā)投入提出了高的要求。 ? ?

[1].章曉文等, 2015, 半導(dǎo)體集成電路的可靠性及評價方法

[2].姚立真,2004,可靠性物理

[3].J. W. McPherson, 2019, ReliabilityPhysics and Engineering

[4].https://www.jedec.org/ ?

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論