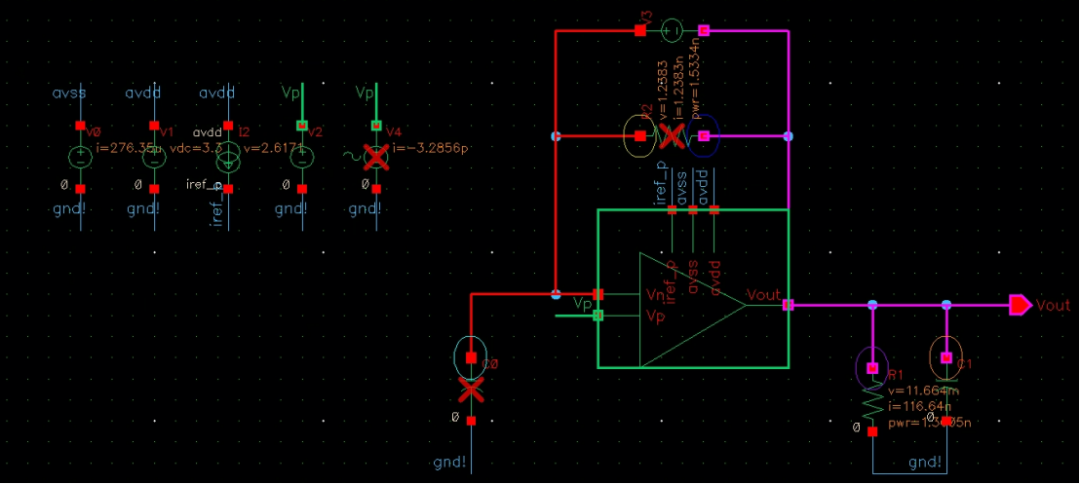

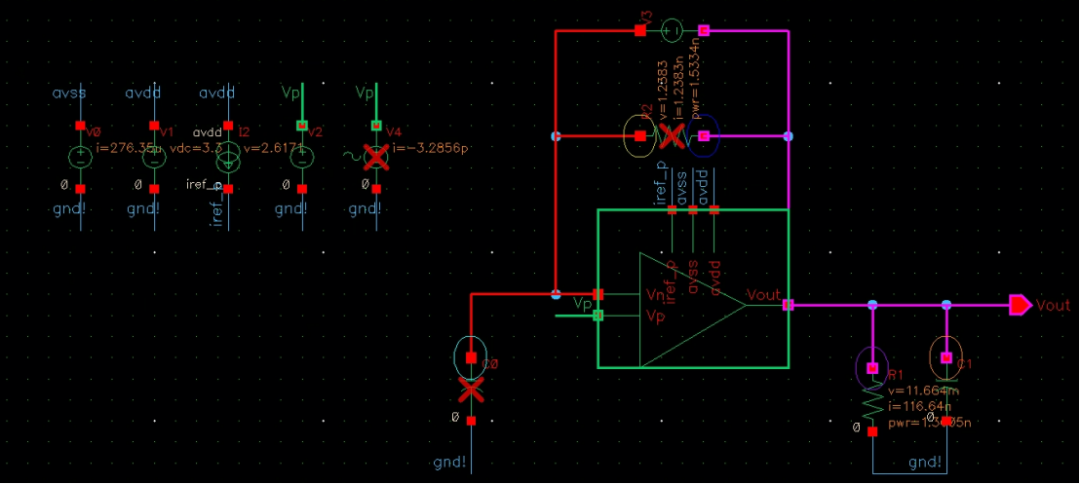

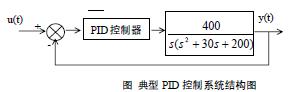

以一個(gè)二級(jí)彌勒補(bǔ)償運(yùn)放為例,說(shuō)明stb仿真和ac仿真的區(qū)別,vdd=3.3,Vcm=1.25V,ibias=5uA,負(fù)載電容是5pF,負(fù)載電阻是100K。

2023-11-03 17:35:52 1218

1218

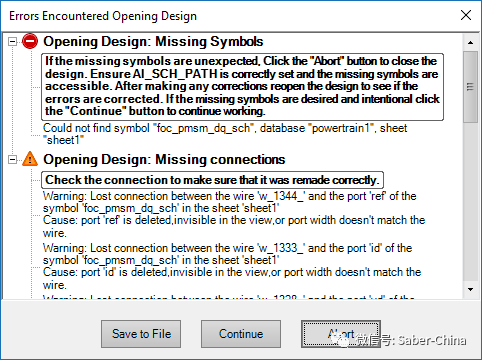

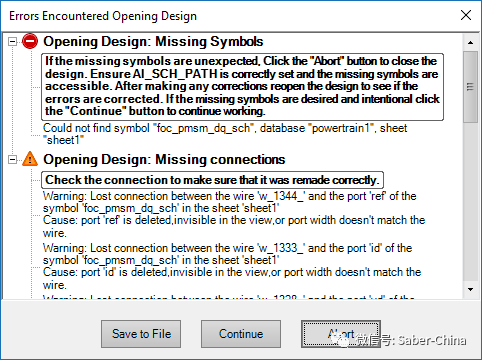

在仿真過(guò)程中,由于仿真模型的不連續(xù)性,或者模型沒有適當(dāng)?shù)乇碚?參數(shù)化,或者當(dāng)求解器無(wú)法求解控制模型行為的方程時(shí),可能就會(huì)出現(xiàn)仿真的收斂問題。

2023-12-05 14:43:09 577

577

仿真的時(shí)候出現(xiàn)這個(gè)問題不知道怎么辦,大家?guī)兔纯丛趺雌疲?/div>

2014-07-08 10:16:54

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

ATK-USB Blaster仿真器 BURNER 5V

2023-03-28 13:05:53

DAP仿真器 BURNER

2023-03-28 13:06:20

本帖最后由 349060579 于 2015-9-14 11:23 編輯

就是做了一個(gè)普通的減法,然而在modelsim做后仿真的時(shí),出現(xiàn)了得到兩個(gè)結(jié)果,前一個(gè)28錯(cuò)誤,后一個(gè)26正確?這是為什么,是我做錯(cuò)了還是仿真硬件電路就是會(huì)出現(xiàn)這樣子?

2015-09-14 11:18:43

;wave->all items in design。這樣就可以查看中間變量了。2.仿真帶有ip核的工程總出錯(cuò)。大部分原因是因?yàn)槟銢]有把支撐ip核的仿真的文件添加到工程中。對(duì)于verilog來(lái)說(shuō),要把

2017-04-15 21:46:29

Keil軟件仿真的串口調(diào)試技巧 引言 在單片機(jī)系統(tǒng)中,串口(UART,通用異步收發(fā)接口)是一個(gè)非常重要的組成部分。通常使用單片機(jī)串口通過(guò)RS232/RS485電平轉(zhuǎn)換芯片與上位機(jī)連接,以

2018-06-29 16:24:31

本文主要描述了如何在QUARTUS II中輸入程序文件,生成網(wǎng)表及標(biāo)準(zhǔn)延時(shí)文件,然后通過(guò) MODELSIM進(jìn)行功能仿真與后仿真的過(guò)程,主要為圖解,含全部代碼及仿真波形。 工具: 源程序

2012-08-12 16:12:54

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

本帖最后由 eehome 于 2013-1-5 10:08 編輯

Xilinx Fpga前仿真后仿真

2012-08-17 08:50:07

Xilinx Fpga前仿真后仿真

2012-08-15 18:49:38

arm9中的jlink仿真器和JTag仿真器有什么區(qū)別?初學(xué)者需要這個(gè)嗎?Jlink支持windows系統(tǒng)該怎么理解?是電腦的系統(tǒng)必須是windows系統(tǒng)?

2014-09-23 23:17:17

nanosim和vcs為什么可以聯(lián)合起來(lái)進(jìn)行數(shù)字模擬混合仿真?nanosim和vcs混合仿真的過(guò)程是怎樣的?

2021-06-18 08:28:30

proteus的電路仿真和虛擬模型仿真的區(qū)別是什么?

2023-04-23 16:41:22

simulink電機(jī)仿真學(xué)習(xí) - 基本坐標(biāo)變換在學(xué)習(xí)simulink過(guò)程中,發(fā)現(xiàn)park變換出來(lái)的id\iq仍然是交流電,心想這么簡(jiǎn)單的變化都不對(duì),懵逼,然后在大佬的講解下,知道了simulink

2021-09-13 09:21:58

`⑴ FPGA 開發(fā)中,是否需要進(jìn)行仿真驗(yàn)證?為什么?有什么個(gè)人體會(huì)?⑵ 一般采用怎樣的仿真工具和仿真手段?了解 Testbench 嗎?⑶ 什么是前仿真和后仿真?能否根據(jù)自身經(jīng)歷,總結(jié)一下前仿真

2012-03-08 11:32:54

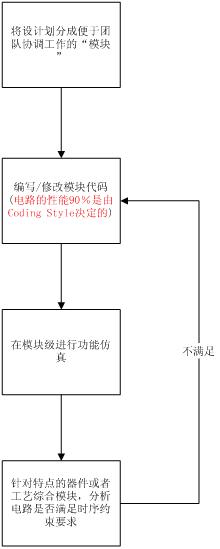

FPGA設(shè)計(jì)流程包括設(shè)計(jì)輸入,仿真,綜合,生成,板級(jí)驗(yàn)證等很多階段。在整個(gè)設(shè)計(jì)流程中,完成設(shè)計(jì)輸入并成功進(jìn)行編譯僅能說(shuō)明設(shè)計(jì)符合一定的語(yǔ)法規(guī)范,并不能說(shuō)明設(shè)計(jì)功能的正確性,這時(shí)就需要通過(guò)仿真對(duì)設(shè)計(jì)進(jìn)行驗(yàn)證。在FPGA 設(shè)計(jì)中,仿真一般分為功能仿真(前仿真)和時(shí)序仿真(后仿真)。

2019-09-20 06:36:23

就是做了一個(gè)普通的減法,然而在modelsim做后仿真的時(shí),出現(xiàn)了得到兩個(gè)結(jié)果,前一個(gè)錯(cuò)誤后一個(gè)正確?這是為什么,是我做錯(cuò)了還是仿真硬件電路就是會(huì)出現(xiàn)這樣子?

2015-09-14 11:17:02

現(xiàn)使用的是NXP Cortex-M0+的板子,由于沒有仿真器,只能通過(guò)軟件模擬仿真,程序很簡(jiǎn)單就是定時(shí)器控制LED燈閃爍,生成的HEX文件下載到MCU內(nèi)部后,MCU正常工作,但在軟件仿真下,定時(shí)器

2013-06-11 16:03:19

我建立了一個(gè)簡(jiǎn)單的程序,只輸入一個(gè)地址對(duì)rom讀取一個(gè)數(shù)。仿真結(jié)果是這樣的前仿真功能正常,但后仿真在輸出紅線,且等到4000ps左右才有很亂的輸出,請(qǐng)問大家這是怎么回事?感激不盡!

2017-04-23 13:54:23

在quartus 中編好程序,生成仿真需要的 .vho 和 .sdf 文件在用modelsim仿真的時(shí)候出現(xiàn)如下錯(cuò)誤,# ** Error: (vsim-SDF-3250) C:/Users

2016-04-05 13:28:34

找了好久就是找不到nxp公司射頻ic,心累啊,這個(gè)proteus,能用天線仿真嗎,好像有點(diǎn)不科學(xué)誒

2017-01-05 10:46:30

modelsim時(shí),會(huì)給出相應(yīng)的時(shí)序關(guān)系。這只能驗(yàn)證你的代碼正確性。綜合后仿真:將剛才編寫的代碼通過(guò)綜合器綜合,若能夠綜合,則會(huì)添加相應(yīng)的時(shí)延信息,判斷你的代碼是否符合要求。時(shí)序仿真:就是在IC上了。我的理解在編

2016-08-23 16:57:06

目前我前仿過(guò)了,功能仿真表示成功。然后后仿有紅線。因?yàn)樵O(shè)置時(shí)沒延時(shí),考慮是后仿門級(jí)電路由原來(lái)的0,1變成了0,1,z,x四種情況,可能原來(lái)的能通過(guò)現(xiàn)在就不通了。遇到這種問題,各位大神如何解決的呢?網(wǎng)表里面的數(shù)據(jù),除了端口,根本不認(rèn)識(shí)啊。。。是個(gè)難題

2016-05-26 17:22:15

《同步電機(jī)模型的MATLAB仿真的設(shè)計(jì).doc》由會(huì)員分享,可免費(fèi)在線閱讀全文,更多與《同步電機(jī)模型的MATLAB仿真的設(shè)計(jì)(最終版)》相關(guān)文檔資源請(qǐng)?jiān)趲蛶臀膸?kù)數(shù)億文檔庫(kù)存里搜索。1、在經(jīng)歷了一開始

2021-09-03 09:00:38

。下面小編來(lái)詳細(xì)介紹一下不同仿真模式的區(qū)別。 數(shù)字電路設(shè)計(jì)中一般包括3個(gè)大的階段:源代碼輸入、綜合和實(shí)現(xiàn),而電路仿真的切入點(diǎn)也基本與這些階段相吻合,根據(jù)適用的設(shè)計(jì)階段的不同仿真可以分為RTL行為級(jí)仿真

2018-01-24 11:06:12

最近在做一個(gè)項(xiàng)目,就是帶隙中運(yùn)放的前后仿真不一致 。后仿真(NO RC)的時(shí)候出現(xiàn)的SA SB參數(shù)和前端仿真中的SA SB 參數(shù)不同。如果將后端網(wǎng)表的SA SB 參數(shù)改成前仿真默認(rèn)參數(shù),與前仿真的

2021-06-25 08:07:33

,進(jìn)入ADE來(lái)進(jìn)行仿真luanch-ADE在setup中設(shè)置design,選擇要進(jìn)行仿真的電路單元然后在model library中選擇所需的模型文件,模型文件在PDK/model...

2021-11-12 08:39:23

給大家分享一下Allegro后仿真的一些資料

2018-03-01 10:44:55

高位高手:小弟論文做制動(dòng)試驗(yàn)臺(tái),由于需要模擬的慣量很大,需要加裝慣性輪,眾所周知,在高速下,慣性輪很不安全而且需要較大功率的電機(jī)帶動(dòng)。SO,小弟有個(gè)想法:能不能通過(guò)半實(shí)物仿真來(lái)取代慣性輪?輸入的是電機(jī)輸出的扭矩、轉(zhuǎn)速;輸出的是經(jīng)過(guò)慣性輪后的轉(zhuǎn)矩。由于沒有半實(shí)物仿真的經(jīng)驗(yàn),需要高手的指點(diǎn)~萬(wàn)謝!!

2013-05-22 11:06:59

比如說(shuō)我用示波器進(jìn)行仿真,通道1仿真結(jié)束后,停止,再加上通道2,兩個(gè)一起仿真就不出現(xiàn)結(jié)果,需要重啟proteus才行,這是怎么回事呢?有什么好的解決辦法么?沒什么分了,請(qǐng)大神們幫一下忙吧

主要是示波器第二次進(jìn)行仿真的話,示波器面板就不出現(xiàn)了

2023-04-23 16:24:40

不知道是否有基于PCB仿真的DAC/ADC的簡(jiǎn)化仿真模型呢? 像數(shù)字邏輯部分一般有IBIS等模型可以用于仿真 不知道模擬部分是否有類似的簡(jiǎn)化模型,可以通過(guò)PCB系統(tǒng)仿真提前評(píng)估自己的設(shè)計(jì)是否滿足呢? 是不是目前只能是等電路焊接完成后才能評(píng)估與發(fā)現(xiàn)問題?

2018-12-06 09:31:08

我發(fā)現(xiàn)硬件仿真的速度一般要低于軟件仿真的速度,我想主要是因?yàn)閏ache miss引起的(在使能cache的情況下),請(qǐng)問,除了cache miss影響之外,還有哪些因素影響硬件仿真的速度,假若處理

2020-05-25 09:13:34

我發(fā)現(xiàn)硬件仿真的速度一般要低于軟件仿真的速度,我想主要是因?yàn)閏ache miss引起的(在使能cache的情況下),請(qǐng)問,除了cache miss影響之外,還有哪些因素影響硬件仿真的速度,假若處理好的話 有沒有可能硬件仿真速度大于軟件仿真速度? 在硬件上需要注意哪些影響硬件仿真速度的關(guān)鍵因素?

2019-07-26 17:18:28

軟件仿真與硬件仿真的區(qū)別和聯(lián)系是什么?

2021-09-28 06:27:59

高速DAP仿真器 BURNER

2023-03-28 13:06:20

................................................................................................................................ 936.1 后仿真前的幾個(gè)準(zhǔn)備步驟

2008-08-05 14:27:09

SPEOS是ANSYS公司功能強(qiáng)大的光學(xué)仿真軟件,用于光學(xué)設(shè)計(jì)、環(huán)境與視覺模擬、成像仿真等,強(qiáng)大的解決方案提供了可視化光學(xué)系統(tǒng)和直觀的人機(jī)交互平臺(tái),其仿真技術(shù)已廣泛用于汽車、電子電器、精密儀器

2022-04-19 10:37:53

用ModelSimSE進(jìn)行功能仿真和時(shí)序仿真的方法(ALTERA篇)(ALTERA 篇)軟件準(zhǔn)備(1) QuartusII,本文截圖是QuartusII 6.1 界面的。我個(gè)人認(rèn)為,如果是開發(fā)StratixII 或CycloneII 或MAXII

2009-06-19 00:26:41 70

70 不能仿真的各種問題

2010-11-09 11:44:07 0

0 SIMULINK仿真的運(yùn)行構(gòu)建好一個(gè)系統(tǒng)的模型之后,接下來(lái)的事情就是運(yùn)行模型,得出仿真結(jié)果。運(yùn)行一個(gè)仿真的完整過(guò)程分成三個(gè)步驟:設(shè)置仿真參數(shù),啟動(dòng)仿真和

2008-06-19 12:53:46 3981

3981 SIMULINK仿真

一、實(shí)驗(yàn)?zāi)康膶W(xué)習(xí)使用SIMULINK進(jìn)行系統(tǒng)仿真的方法二、實(shí)驗(yàn)內(nèi)容:1、Simulink的基本操作(1)運(yùn)行

2008-10-17 00:26:06 3514

3514

為什么要使用仿真器

1、 仿真的概念:仿真的概念其實(shí)使用非常廣,最終的含義就是使用可控的手段來(lái)模仿真實(shí)的情況。在嵌入式系統(tǒng)的

2008-12-13 21:49:51 1921

1921 基于LabVIEW的SIP系統(tǒng)仿真的設(shè)計(jì)與實(shí)現(xiàn)

將虛擬儀器的概念引入大亞灣核電站的SIP系統(tǒng)的仿真,利用計(jì)算機(jī)仿真技術(shù)參與其系統(tǒng)設(shè)

2009-05-14 18:35:31 645

645

芯片高速仿真的創(chuàng)新

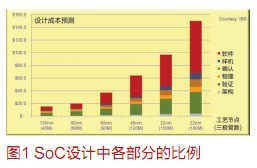

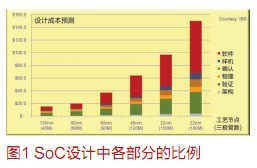

目前IC設(shè)計(jì)中,軟件工作量越來(lái)越大(圖1),在65nm設(shè)計(jì)成本統(tǒng)計(jì)中,軟件已占50%,驗(yàn)證占30%,其他還有樣機(jī)、確認(rèn)(Validation)、物理、架構(gòu)。隨著工

2010-02-06 10:55:30 583

583

1、 仿真的目的:在軟件環(huán)境下,驗(yàn)證電路的行為和設(shè)想中的是否一致。

2、 仿真的分類:a) 功能仿真:在RTL層進(jìn)行的仿真,其特點(diǎn)是不考慮構(gòu)成

2010-06-07 08:32:20 3686

3686

ALTERA公司:用ModelSimSE進(jìn)行功能仿真和時(shí)序仿真的方法(ALTERA篇)之學(xué)習(xí)筆記

2012-08-15 16:00:59 68

68 IC卡讀寫仿真IC卡讀寫仿真IC卡讀寫仿真

2015-11-10 16:49:51 5

5 用protues仿真的數(shù)字電壓表和程序代碼

2016-05-23 16:25:31 26

26 基于軟件和邏輯聯(lián)合仿真的SOPC驗(yàn)證技術(shù)研究_周珊

2017-01-07 19:00:39 9

9 在我們用ModelSim仿真的時(shí)候經(jīng)常是修改一點(diǎn)一點(diǎn)修改代碼,這樣會(huì)造成一個(gè)無(wú)奈的操作循環(huán):修改代碼--->編譯代碼--->仿真設(shè)置--->進(jìn)入仿真頁(yè)面--->添加需要觀察的波形--->運(yùn)行仿真

2017-02-11 15:25:07 10202

10202

基于MATLAB仿真的火電廠環(huán)境影響的研究_張新銘

2017-03-18 09:13:24 0

0 數(shù)字電路設(shè)計(jì)中一般包括3個(gè)大的階段:源代碼輸入、綜合和實(shí)現(xiàn),而電路仿真的切入點(diǎn)也基本與這些階段相吻合,根據(jù)適用的設(shè)計(jì)階段的不同仿真可以分為RTL行為級(jí)仿真、綜合后門級(jí)功能仿真和時(shí)序仿真。這種仿真輪廓的模型不僅適合FPGA/CPLD設(shè)計(jì),同樣適合IC設(shè)計(jì)。

2018-07-02 08:43:00 16011

16011 本文檔的主要內(nèi)容詳細(xì)介紹的是IC卡讀寫仿真的技術(shù)資料和軟件免費(fèi)下載。

2018-11-06 08:00:00 27

27 本文檔的主要內(nèi)容詳細(xì)介紹的是IC卡讀寫仿真的資料合集免費(fèi)下載。

2020-05-28 16:30:00 28

28 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA仿真的學(xué)習(xí)課件和工程文件免費(fèi)下載包括了:1、testbench編寫,2、仿真工具使用,2、仿真工具使用,4、Vivado與Modelsim聯(lián)合仿真。

2020-12-10 15:28:18 30

30 本文檔的主要內(nèi)容詳細(xì)介紹的是單片機(jī)公交報(bào)站仿真的原理圖和仿真源程序免費(fèi)下載。

2020-12-14 08:00:00 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是4個(gè)URAT VHDL程序與仿真的資料合集包括了:1. 頂層程序與仿真,2. 波特率發(fā)生器程序與仿真,3. UART發(fā)送器程序與仿真,4. UART接收器程序與仿真。

2020-12-18 16:44:17 6

6 svpwm的MATLAB仿真的實(shí)現(xiàn)方法說(shuō)明。

2021-04-28 14:56:34 22

22 具有Protues仿真的電子表項(xiàng)目源碼

2021-05-20 09:39:10 1

1 具有Protues仿真的萬(wàn)年歷項(xiàng)目源碼

2021-05-20 09:40:24 15

15 仿真是我們?cè)隍?yàn)證邏輯功能的常用手段。通過(guò)仿真,我們可以提早發(fā)現(xiàn)一些隱含的邏輯Bug。仿真一般分為功能仿真和時(shí)序仿真,有的時(shí)候也稱作前仿真和后仿真。這兩者的主要區(qū)別是在功能仿真里暫時(shí)忽略了邏輯延時(shí)

2021-07-02 10:43:26 2556

2556 仿真是我們?cè)隍?yàn)證邏輯功能的常用手段。通過(guò)仿真,我們可以提早發(fā)現(xiàn)一些隱含的邏輯Bug。仿真一般分為功能仿真和時(shí)序仿真,有的時(shí)候也稱作前仿真和后仿真。這兩者的主要區(qū)別是在功能仿真里暫時(shí)忽略了邏輯延時(shí)和布局布線延時(shí),仿真的模型相對(duì)簡(jiǎn)單,仿真的運(yùn)行速度更快。

2021-07-02 10:49:29 2695

2695 電機(jī)拖動(dòng)與MATLAB仿真的程序代碼免費(fèi)下載。

2022-04-02 16:28:04 8

8 然而,在仿真的情況下,軟件算法使用設(shè)計(jì)語(yǔ)言處理表示設(shè)計(jì)模型的數(shù)據(jù),而仿真器使用處理器陣列啟用的計(jì)算引擎處理數(shù)據(jù)結(jié)構(gòu)。盡管硬件仿真的市場(chǎng)規(guī)模已超過(guò) 3 億美元,但這并不意味著它將成為 HDL 仿真工具的終點(diǎn)。

2022-06-19 15:27:37 1575

1575 本文主要介紹使用 Vivado 仿真器進(jìn)行混合語(yǔ)言仿真的一些要點(diǎn)。

2022-08-01 09:25:56 1031

1031 虛擬仿真的概念及意義 什么是虛擬仿真?虛擬仿真的概念是什么?想必大家對(duì)VR這些都不陌生,虛擬現(xiàn)實(shí)技術(shù)綜合了計(jì)算機(jī)圖形學(xué)、圖像處理與模式識(shí)別、智能技術(shù)、傳感技術(shù)、語(yǔ)音處理與音響技術(shù)、網(wǎng)絡(luò)技術(shù)等多門科學(xué)

2022-12-13 16:29:12 7987

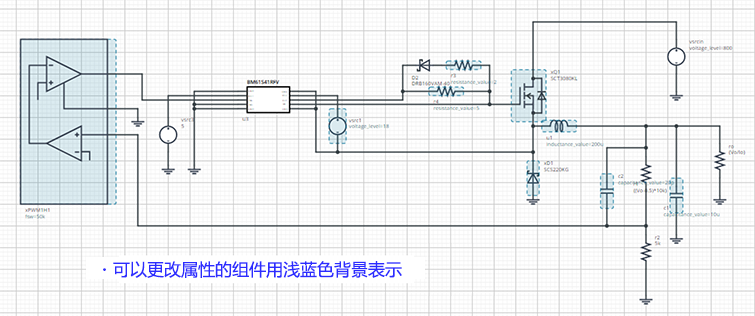

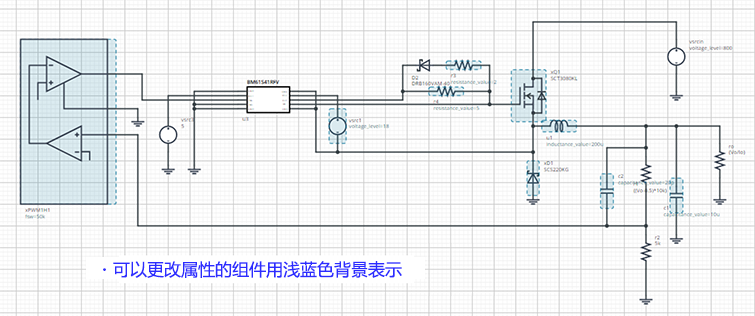

7987 本文將介紹通過(guò)更改所提供的仿真電路的元器件、常數(shù)和條件等來(lái)執(zhí)行仿真的方法。

2023-02-14 09:26:25 489

489

電路仿真是指使用計(jì)算機(jī)模擬電路的過(guò)程,它可以幫助電路設(shè)計(jì)者更好地理解電路的行為,并可以檢測(cè)出電路中的錯(cuò)誤。電路仿真的知識(shí)包括電路分析、電路模擬、電路仿真軟件的使用、電路仿真結(jié)果的分析等。

2023-02-17 14:04:36 4678

4678 基于單片機(jī)IC卡讀寫Proteus仿真設(shè)計(jì)資料包含仿真及源程序

2023-04-20 15:36:18 15

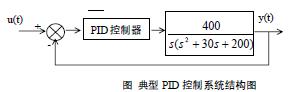

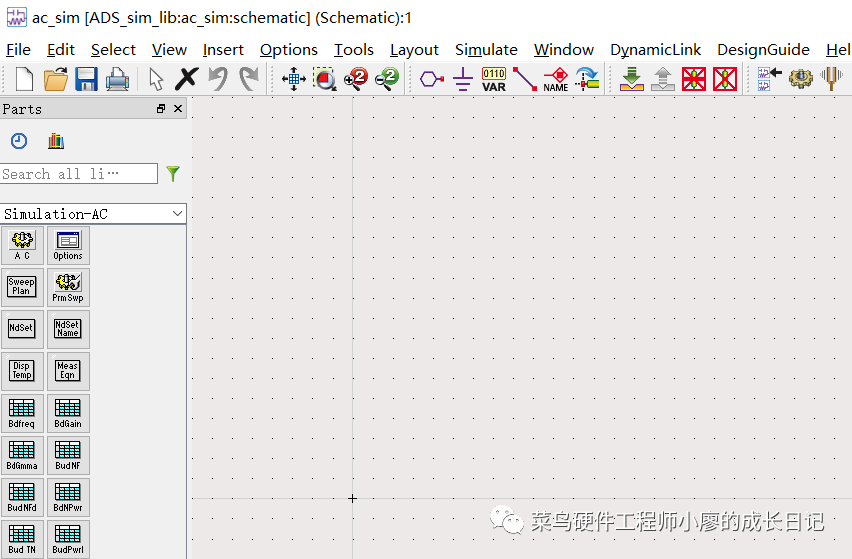

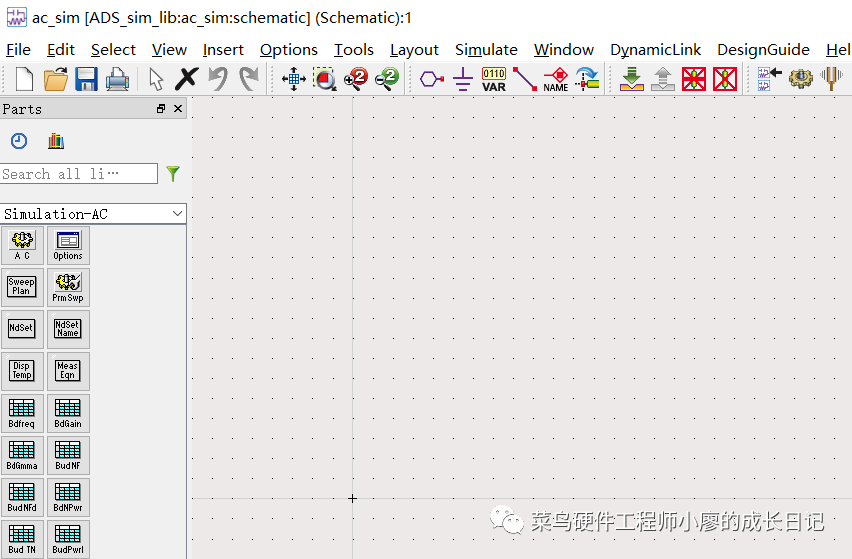

15 交流仿真的概念:交流放著是射頻電路中最重要的仿真方式之一,主要用于分析電路的小信號(hào)特性和噪聲特性。

2023-06-29 11:17:31 9028

9028

時(shí)序仿真與功能仿真的區(qū)別在于 時(shí)序仿真與功能仿真是電子設(shè)計(jì)自動(dòng)化(EDA)中最常見的兩種仿真方式。雖然二者都是仿真技術(shù),但根據(jù)仿真模型和目的的不同,它們之間還是存在一些根本差異。 1.定位 時(shí)序仿真

2023-09-08 10:39:40 3033

3033 時(shí)序仿真與功能仿真的區(qū)別有哪些? 時(shí)序仿真和功能仿真都是電子設(shè)計(jì)自動(dòng)化(EDA)過(guò)程中的常見任務(wù),它們都是為了驗(yàn)證或驗(yàn)證電路設(shè)計(jì)的正確性。然而,它們之間也有明顯的區(qū)別。 時(shí)序仿真 時(shí)序仿真是一種

2023-09-17 14:15:02 2614

2614 電子發(fā)燒友網(wǎng)站提供《能連arduino仿真的電化學(xué)軟件.zip》資料免費(fèi)下載

2023-09-18 09:25:26 5

5 AllegroPCBSI仿真的教程(英文)

2022-12-30 09:19:28 2

2 目前仿真的方向基本上有兩個(gè),一個(gè)是以試驗(yàn)測(cè)試為導(dǎo)向,對(duì)產(chǎn)品進(jìn)行EMC測(cè)試項(xiàng)目的仿真

2023-11-04 17:28:06 1381

1381

最近探索仿真的時(shí)候,在DF下仿真射頻系統(tǒng)時(shí),需要用到包絡(luò)仿真(envelope simulation),所以就扒拉著看了一點(diǎn)ADS里面關(guān)于其的help內(nèi)容。以下為翻譯記錄。

2023-11-08 14:23:26 430

430

PCB仿真軟件有哪些?PCB仿真軟件是如何進(jìn)行LAYOUT仿真的? PCB仿真軟件是為了幫助電子工程師在設(shè)計(jì)和開發(fā)PCB電路板時(shí)進(jìn)行各種仿真分析而開發(fā)的。這些軟件可以模擬電路的行為和性能,并幫助

2023-11-24 14:51:01 5899

5899 電子發(fā)燒友網(wǎng)站提供《模擬電路仿真的基本原理.pdf》資料免費(fèi)下載

2023-11-27 09:34:20 0

0 我調(diào)試過(guò)其他同事的產(chǎn)品,并且把相應(yīng)的鏈路,也量化到仿真軟件里。然后花時(shí)間,驗(yàn)證出正確的仿真設(shè)置,仿真一些指標(biāo)對(duì)接收機(jī)性能的影響。并且,在實(shí)驗(yàn)室實(shí)測(cè),對(duì)比測(cè)試和仿真的差別,發(fā)現(xiàn)吻合的很好。

2023-11-27 16:59:40 332

332

仿真器和燒錄器的區(qū)別? 仿真器和燒錄器是電子技術(shù)領(lǐng)域中常見的兩種設(shè)備,它們?cè)陔娮酉到y(tǒng)的開發(fā)和調(diào)試過(guò)程中起著重要的作用。盡管它們都是用于調(diào)試電子設(shè)備的工具,但是它們的功能和工作原理有著明顯的區(qū)別

2023-12-07 15:48:20 2497

2497 在芯片設(shè)計(jì)中,前仿真和后仿真都是非常重要的環(huán)節(jié),但它們?cè)诠δ芎湍康纳洗嬖诿黠@的區(qū)別。本文將詳細(xì)介紹前仿真和后仿真的區(qū)別,以及它們?cè)谛酒O(shè)計(jì)中的應(yīng)用和重要性。 一、前仿真和后仿真概述 前仿真:前仿真

2023-12-13 15:06:55 2048

2048 IC設(shè)計(jì)為什么需要仿真模擬?仿真模擬的重要性有哪些? IC設(shè)計(jì)(集成電路設(shè)計(jì))是指利用EDA工具(電子設(shè)計(jì)自動(dòng)化工具)設(shè)計(jì)出滿足特定功能和性能要求的集成電路芯片。仿真模擬是IC設(shè)計(jì)過(guò)程中至關(guān)重要

2023-12-19 11:35:38 928

928 FPGA時(shí)序仿真和功能仿真在芯片設(shè)計(jì)和驗(yàn)證過(guò)程中各自扮演著不可或缺的角色,它們之間存在明顯的區(qū)別。

2024-03-15 15:28:40 339

339 FPGA的前仿真和后仿真在芯片設(shè)計(jì)和驗(yàn)證過(guò)程中扮演著不同的角色,各自具有獨(dú)特的特點(diǎn)和重要性。

2024-03-15 15:29:06 261

261  電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論