本文介紹了一種基于FPGA的用于高分辨率視頻圖像處理的SDRAM控制器的設(shè)計(jì)方法。通過設(shè)置SDRAM的工作狀態(tài),使其工作在猝發(fā)模式。在視頻時(shí)序信號(hào)控制下,用多行連續(xù)的SDRAM存儲(chǔ)空間,存取視頻

2014-02-10 14:10:21 3023

3023

1. 背景 這篇文章主要介紹了DDR3IP核的寫實(shí)現(xiàn)。 2. 寫命令和數(shù)據(jù)總線介紹 DDR3 SDRAM控制器IP核主要預(yù)留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5068

5068

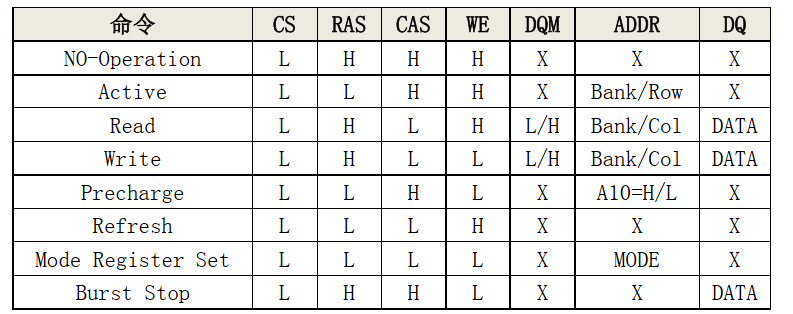

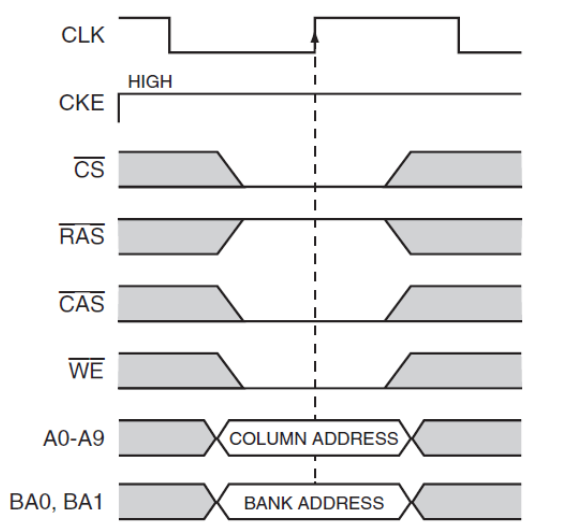

/列地址選擇、讀寫選擇、數(shù)據(jù)有效;(2)地址:時(shí)分復(fù)用管腳,根據(jù)行/列地址選擇管腳控制輸入地址為行地址或列地址;(3)數(shù)據(jù):雙向管腳,受數(shù)據(jù)有效控制;根據(jù)控制信號(hào)和地址輸入,SDRAM包括多種輸入命令

2019-06-10 05:00:08

stm32固件庫(kù)手冊(cè)使用方法(以FMC_SDRAM擴(kuò)展外部?jī)?chǔ)存為例)一、SDRAM簡(jiǎn)介二、利用固件庫(kù)FMC外設(shè)初始化1.初始化SDRAM時(shí)序結(jié)構(gòu)體2.初始化SDRAM結(jié)構(gòu)體3.初始化SDRAM命令

2022-01-20 08:22:13

。 設(shè)置完模式寄存器后就進(jìn)入正常操作模式。 實(shí)際上具體的操作要跟選用的處理器的SDRAM控制模塊相結(jié)合來設(shè)置。對(duì)于這些初始化命令比較直觀的理解就是拿邏輯分析儀來分析。 &

2009-10-24 10:38:38

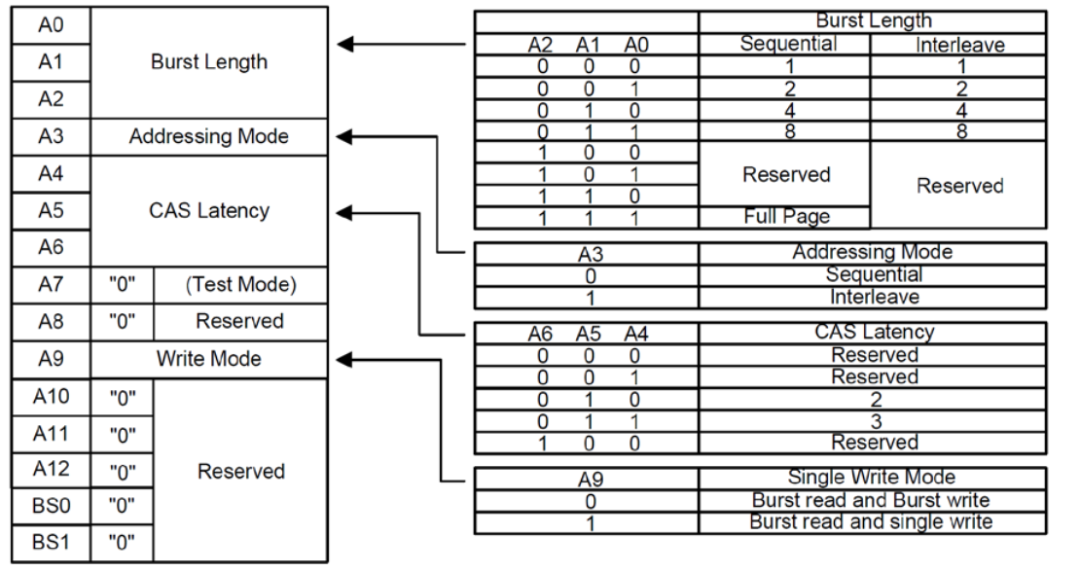

、突發(fā)長(zhǎng)度這幾個(gè)參數(shù)。這幾個(gè)參數(shù)是在進(jìn)行配置命令時(shí)給addr這些引腳賦值決定的。四、編寫SDRAM初始化模塊并進(jìn)行仿真對(duì)于SDRAM初始化模塊的編寫,我們可以先學(xué)習(xí)下SDRAM的初始化時(shí)序圖,然后再

2018-03-26 14:35:04

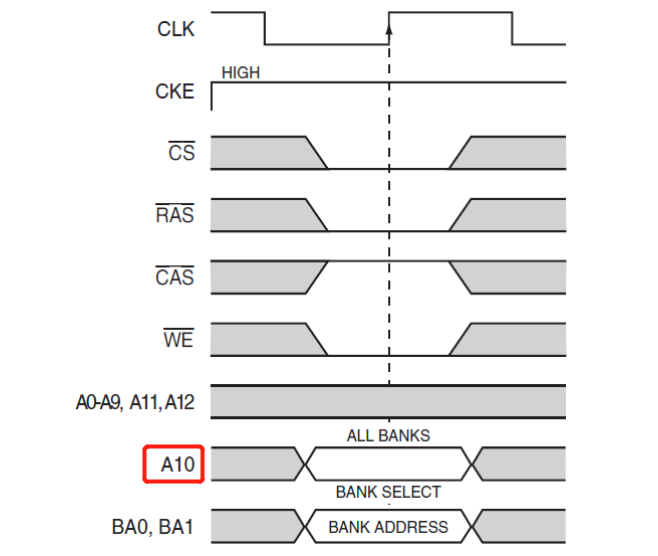

的時(shí)候,只用A0~A8這9根線;A10這個(gè)信號(hào)可以用來控制Auto-precharge。RAS、CAS、WE:這三根線就是用來給SDRAM發(fā)命令的,包括初始化、讀、寫、自動(dòng)充電等命令。UDQM、LDQM

2016-01-16 18:06:27

獲取我們給出的命令時(shí)出現(xiàn)錯(cuò)誤。CKE:時(shí)鐘使能信號(hào),是用來控制SDRAM內(nèi)部時(shí)鐘是否工作的一個(gè)信號(hào)(在SDRAM內(nèi)部也是有時(shí)鐘的哦)CS:片選信號(hào),這里需要注意的是,如果要對(duì)SDRAM進(jìn)行操作,必須

2019-01-14 06:35:26

SDRAM的基本工作原理是什么SDRAM的基本讀寫操作步驟是什么一種簡(jiǎn)單的通用SDRAM控制器的實(shí)現(xiàn)

2021-05-10 06:26:44

獲取我們給出的命令時(shí)出現(xiàn)錯(cuò)誤。CKE:時(shí)鐘使能信號(hào),是用來控制SDRAM內(nèi)部時(shí)鐘是否工作的一個(gè)信號(hào)(在SDRAM內(nèi)部也是有時(shí)鐘的哦)CS:片選信號(hào),這里需要注意的是,如果要對(duì)SDRAM進(jìn)行操作,必須

2019-01-24 06:35:14

SDRAM的控制原理是什么?SDRAM有哪些控制命令呢?SDRAM的讀寫流程有哪些呢?

2021-10-22 08:31:37

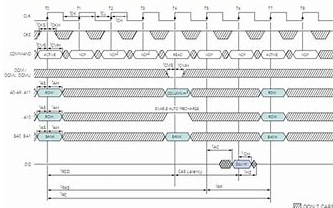

;如果上一次執(zhí)行了寫操作,則此次執(zhí)行讀操作。如果不是同時(shí)出現(xiàn)讀寫請(qǐng)求,則是什么請(qǐng)求就執(zhí)行什么操作。2)采用全頁(yè)模式的讀寫操作,該模式在讀、寫完成時(shí),需要給出預(yù)充電命令才能結(jié)束。3)刷新請(qǐng)求始終優(yōu)于讀、寫請(qǐng)求。DDR的時(shí)序與SDRAM是相似的,學(xué)好SDRAM后,理解DDR2和DDR3就非常容易了。

2017-11-23 11:02:27

第39章 STM32F429的FMC總線應(yīng)用之SDRAM本章教程為大家講解SDRAM的驅(qū)動(dòng)實(shí)現(xiàn),后面LCD的顯存和大數(shù)量的存取都要用到。目錄第39章 STM32F429的FMC總線應(yīng)用之

2021-08-10 06:39:31

第49章 STM32H7的FMC總線應(yīng)用之SDRAM本章教程為大家講解SDRAM的驅(qū)動(dòng)實(shí)現(xiàn),后面LCD的顯存和大數(shù)量的存取都要用到。49.1 初學(xué)者重要提示49.2 SDRAM硬件設(shè)計(jì)49.3 SDRAM驅(qū)動(dòng)設(shè)計(jì)49.4 SDR...

2021-08-13 08:09:44

AT32 MCU SDRAM Application Note本文主要講解AT32 SDRAM 控制器的使用。

2023-10-25 06:37:13

。TMS626812A 主要有六條控制命令,它們是:條激尖 / 行地址入口、列地址入口 / 寫操作、列地址入口 / 讀操作、條無效、自動(dòng)刷新、自動(dòng)刷新。SDRAM 與 TMS320C54x 接口中用到的命令主要有

2020-04-23 08:00:00

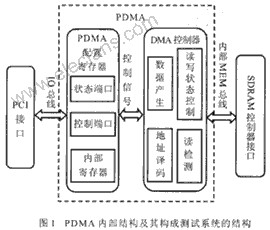

,經(jīng)常在SDR SDRAM驅(qū)動(dòng)器中加入輸入和輸出緩沖器(FIFO)。為了能夠使SDR SDRAM控制器能夠獨(dú)立自主的讀取輸入FIFO的數(shù)據(jù)到SDR SDRAM,以及SDR SDRAM到輸出FIFO中,中間

2023-03-27 17:09:14

本次發(fā)布三例 SDRAM 控制器參考設(shè)計(jì)及 IP Core Generator 支持調(diào)用SDRAM 控制器 IP。 1. 32-bit SDRAM Controller for device

2022-10-08 07:59:17

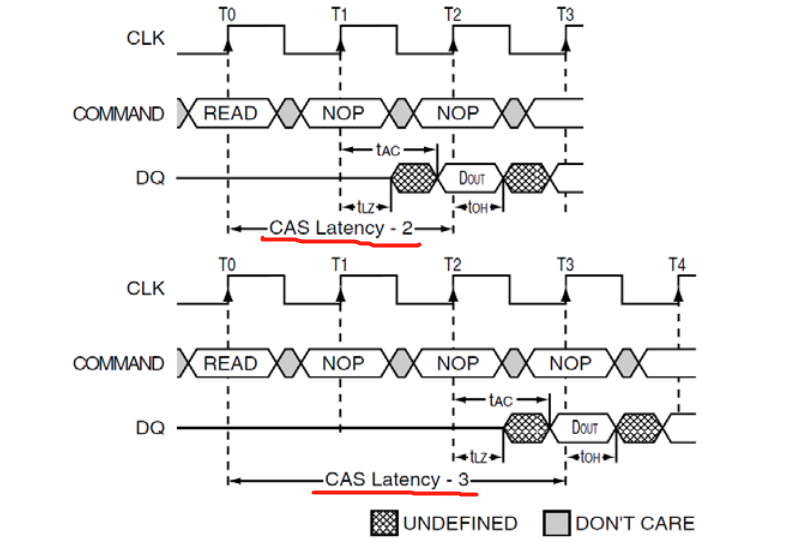

“從讀命令到數(shù)據(jù)輸出的等待時(shí)間”,其以時(shí)鐘為單位。允許值是1、2、3,默認(rèn)為3。initialization refresh cycles(初始化刷新周期):即為“復(fù)位后,SDRAM控制器要執(zhí)行多少個(gè)

2012-03-01 10:20:50

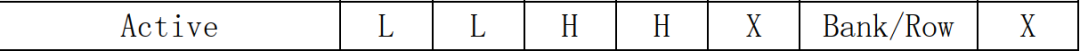

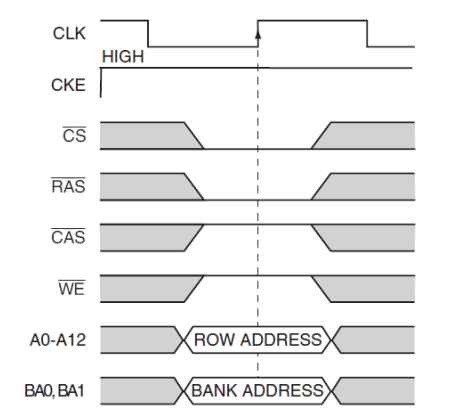

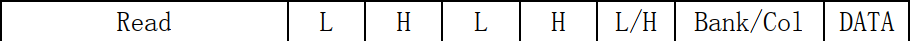

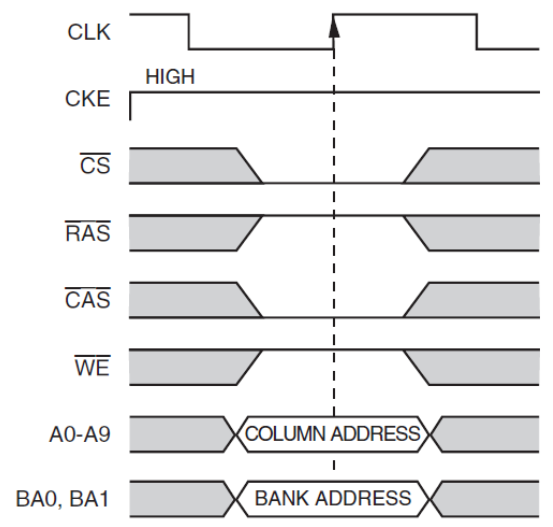

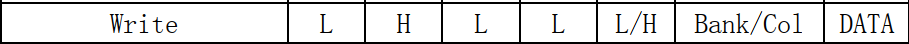

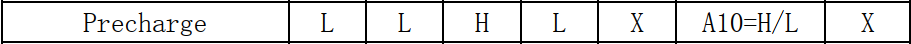

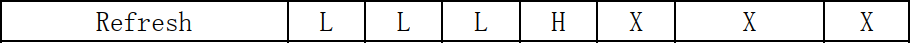

,此時(shí),我們只需要設(shè)置 LDQM 為低電平,UDQM 為高電平,就可以了。(4)控制命令SDRAM 的驅(qū)動(dòng)需要用到一些命令,我們列出幾個(gè)常用的命令給大家做講解,如表 19.1.1.2所示:表

2020-05-13 11:25:02

基于FPGA的SDRAM控制器設(shè)計(jì)(三)讀寫作者:小周 本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請(qǐng)注明出處! SDRAM控制器設(shè)計(jì)的主要功能是能對(duì)SDRAM進(jìn)行讀寫操作,本工程實(shí)現(xiàn)了SDRAM的初始化、自動(dòng)

2020-04-23 11:31:47

在這一講中,Kevin先帶著大家了解一下我們這一套視頻教程《SDRAM那些事兒第一季—輕松設(shè)計(jì)SDRAM控制器》中所要講的這個(gè)項(xiàng)目。這個(gè)項(xiàng)目總的來講,就是設(shè)計(jì)一個(gè)簡(jiǎn)單的SDRAM控制器,PC機(jī)通過

2017-05-08 22:14:21

終于到第九講了,第九講是這套《輕松設(shè)計(jì)SDRAM控制器》的最后一講。相信大家也是非常的期待這套教程的終結(jié),在前面的8講內(nèi)容,我們已經(jīng)介紹完了SDRAM控制器、串口部分和命令解析模塊。在第九講中,我們

2017-05-08 22:38:37

開始正式運(yùn)營(yíng)一周,已收獲粉絲38個(gè),對(duì)于Kevin來講,還是一種相當(dāng)大的鼓勵(lì)了。轉(zhuǎn)載請(qǐng)注明:鄧堪文博客 ? 【開源騷客】《輕松設(shè)計(jì)SDRAM控制器》第五講—仲裁機(jī)制介紹及刷新模塊講解

2017-05-08 22:22:44

到第七講,我們就已經(jīng)把SDRAM控制器的部分全部都完成了。雖然SDRAM控制器的部分完成好了,但是咱們的項(xiàng)目還沒完,我們還需要將串口部分和控制器部分聯(lián)合起來,形成一個(gè)可以通過串口發(fā)送命令控制

2017-05-08 22:31:58

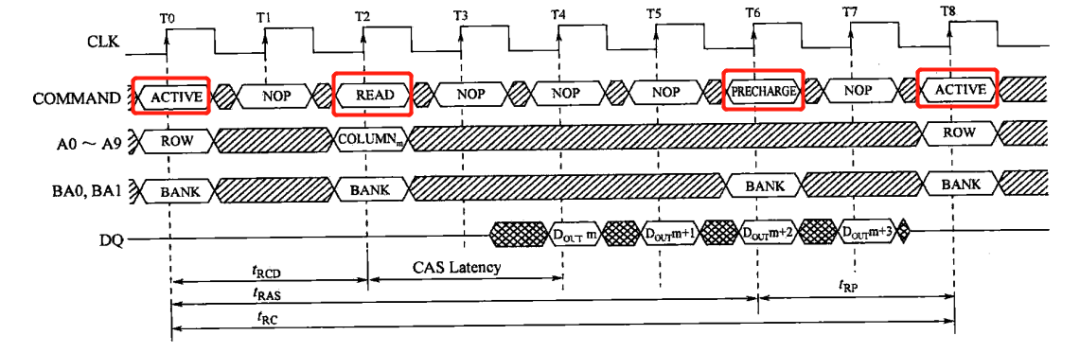

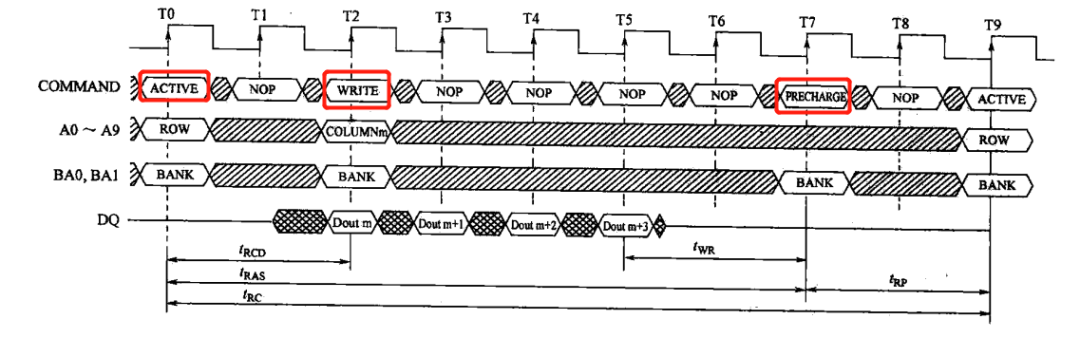

器件工作原理;SDRAM寫模塊狀態(tài)機(jī)講解;SDRAM寫模塊時(shí)序設(shè)計(jì)。一、SDRAM器件工作原理為了讓我們更好的設(shè)計(jì)SDRAM控制器,我們必須明白SDRAM器件的工作原理。當(dāng)然,我們這套教程所講

2017-05-08 22:25:30

設(shè)計(jì)簡(jiǎn)易計(jì)算器核心思想》一篇技術(shù)類的文章,當(dāng)然我們也會(huì)繼續(xù)給大家分享有價(jià)值的內(nèi)容。目前微信公眾號(hào)已開始正式運(yùn)營(yíng)一周,已收獲粉絲38個(gè),對(duì)于Kevin來講,還是一種相當(dāng)大的鼓勵(lì)了。轉(zhuǎn)載請(qǐng)注明:鄧堪文博客 ? 【開源騷客】《輕松設(shè)計(jì)SDRAM控制器》第四講—SDRAM 理論基礎(chǔ)講解

2017-05-08 22:20:54

控制器,PC機(jī)通過串口發(fā)送指令和數(shù)據(jù)來控制SDRAM芯片實(shí)現(xiàn)任意讀寫操作。本文主要通過以下幾個(gè)部分進(jìn)行講解:項(xiàng)目整體框圖介紹;串口收發(fā)模塊講解;SDRAM控制器核心模塊。一、項(xiàng)目整體框圖介紹 根據(jù)演示

2016-10-16 23:04:43

講解第六講:SDRAM寫模塊講解第七講:簡(jiǎn)易SDRAM控制器的完善第八講:命令解析模塊講解第九講:解密讀寫FIFO

2017-05-10 19:35:33

第1節(jié) SDRAM讀寫控制器--作者:小黑同學(xué)本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請(qǐng)注明出處!1.1 總體設(shè)計(jì)1.1.1 概述同步動(dòng)態(tài)隨機(jī)存取內(nèi)存(synchronousdynamic

2020-10-15 15:16:02

SDRAM功能模塊講解

2021-04-01 15:15:08

SDRAM時(shí)序講解

2021-04-01 15:12:38

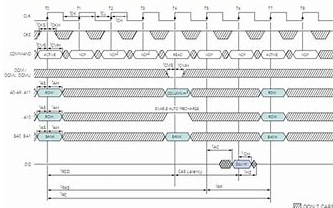

和內(nèi)部流水線結(jié)構(gòu)允許存儲(chǔ)外部高速數(shù)據(jù),其內(nèi)部結(jié)構(gòu)框圖如圖1所示。 SDRAM的所有輸入和輸出都與系統(tǒng)時(shí)鐘CLK上升沿同步,并且由輸入信號(hào)RAS、CAS、WE組合產(chǎn)生SDRAM控制命令,其基本的控制命令

2018-12-07 10:35:02

(建議用下面這段)至簡(jiǎn)設(shè)計(jì)法實(shí)現(xiàn)的SDRAM控制器使用了四段式狀態(tài)機(jī),其他信號(hào)根據(jù)狀態(tài)機(jī)對(duì)齊而設(shè)計(jì),結(jié)構(gòu)相當(dāng)清晰,相信有一定基礎(chǔ)的工程師,能感覺到這樣設(shè)計(jì)的精簡(jiǎn)、奇妙之處,歡迎借鑒、學(xué)習(xí)。 至簡(jiǎn)設(shè)計(jì)法

2017-08-02 17:43:35

狀態(tài)。? 仲裁模塊arbitrate即仲裁模塊,因?yàn)?b class="flag-6" style="color: red">SDRAM控制時(shí)可能進(jìn)行刷新或者讀寫操作(后續(xù)介紹),但是刷新時(shí)不能進(jìn)行讀寫操作,因此需要一個(gè)仲裁模塊,對(duì)這些控制命令進(jìn)行管理,使刷新命令優(yōu)先級(jí)最高

2020-04-15 14:43:50

摘要:介紹SDRAM的主要控制信號(hào)和基本命令時(shí)序,提出一種應(yīng)用于解復(fù)用的支持多路讀寫的SDRAM接口設(shè)計(jì),為需要大容量存儲(chǔ)器的電路設(shè)計(jì)提供了新思路。關(guān)鍵詞:SDRAM 解復(fù)用 接口 存儲(chǔ)器

2018-12-03 15:20:48

文章目錄一、 項(xiàng)目介紹:寫命令和寫數(shù)據(jù)總線介紹寫控制模塊框圖及波形代碼(1)連續(xù)寫(2)間隔部分測(cè)試代碼一、 項(xiàng)目介紹:本章節(jié)將會(huì)講解 A7 芯片內(nèi)自帶的 DDR3 SDRAM 的 IP 核的寫時(shí)序

2022-02-08 07:08:01

如何解決SDRAM控制器設(shè)計(jì)刷新的問題?

2021-11-04 07:20:02

存儲(chǔ)單元的下一個(gè)單元進(jìn)行尋址,也即是需要不停給SDRAM列激活信號(hào)以及讀/寫命令(行地址不變,所以不用再對(duì)行尋址)。雖然由于讀/寫延遲相同可以讓數(shù)據(jù)的傳輸在I/O端是連續(xù)的,但它占用了大量的內(nèi)存控制資源

2020-01-04 19:20:52

SDRAM有一個(gè)同步接口,在響應(yīng)控制輸入前會(huì)等待一個(gè)時(shí)鐘信號(hào),這樣就能和計(jì)算機(jī)的系統(tǒng)總線 同步。時(shí)鐘被用來驅(qū)動(dòng)一個(gè)有限狀態(tài)機(jī),對(duì)進(jìn)入的指令進(jìn)行管線(Pipeline)操作。這使得SDRAM與沒有同步

2020-09-23 10:59:56

最近想寫 SDRAM的讀寫。哪些命令看到 云里霧里的 ,有沒好人發(fā)給 調(diào)通的 VHDL 程序 ,給個(gè)參考學(xué)習(xí)下。拜謝了{(lán):4:}{:4:}

2013-02-25 16:04:55

簡(jiǎn)要介紹了SDRAM工作原理并認(rèn)真研究了Altera提供的SDRAM控制器,根據(jù)實(shí)際系統(tǒng)使用需要加以修改簡(jiǎn)化,設(shè)計(jì)了對(duì)修改后控制器進(jìn)行操作的狀態(tài)機(jī)。采用全頁(yè)突發(fā)讀寫模式,每次讀/寫

2009-12-26 17:02:56 70

70 DDR2 SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設(shè)計(jì)方法!詳述了其基本結(jié)構(gòu)和設(shè)計(jì)思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 實(shí)現(xiàn)了一個(gè)三端口非透明型SDRAM 控制器,該控制器面向用戶具有多個(gè)端口,通過輪換優(yōu)先級(jí)的設(shè)計(jì)保證了多個(gè)端口平均分配SDRAM的帶寬且不會(huì)降

2010-03-03 14:37:14 11

11 本文介紹了DDR3 SDRAM 的基本特點(diǎn)和主要操作時(shí)序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計(jì)方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計(jì)思想,分析了各模塊功能與設(shè)計(jì)注意事項(xiàng),并

2010-07-30 17:13:55 30

30 不只計(jì)算機(jī)存儲(chǔ)器系統(tǒng)一直需要更大、更快、功率更低、物理尺寸更小的存儲(chǔ)器,嵌入式系統(tǒng)應(yīng)用也有類似的要求。本應(yīng)用指南介紹了邏輯分析儀在檢驗(yàn)DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 本文將介紹DDR SDRAM的一些概念和難點(diǎn),主要結(jié)合上一篇SDRAM的介紹加以對(duì)比。同時(shí)著重講解主流DDRII的技術(shù)。最后結(jié)合硬件設(shè)計(jì)提出一些參考。

DDR SDRAM全稱為Double Dat

2010-08-30 16:26:16 119

119 摘要: 介紹了SDRAM的存儲(chǔ)體結(jié)構(gòu)、主要控制時(shí)序和基本操作命令,并且結(jié)合實(shí)際系統(tǒng),給出了一種用FPGA實(shí)現(xiàn)的通用SDRAM控制器的方案。

關(guān)鍵詞:

2009-06-20 12:51:58 834

834

摘 要:介紹了SDRAM的特點(diǎn)和工作原理,提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,使用該方法實(shí)現(xiàn)的控制器可非常方便地對(duì)SDRAM進(jìn)行控制。

關(guān)鍵

2009-06-20 13:04:51 2075

2075 基于FPGA的高速SDRAM控制器的視頻應(yīng)用

0 引言 SDRAM(同步動(dòng)態(tài)存儲(chǔ)器)是一種應(yīng)用廣泛的存儲(chǔ)器,具有容量大、數(shù)據(jù)讀寫速度快、價(jià)格低廉等優(yōu)點(diǎn),特別適

2009-11-04 09:56:20 847

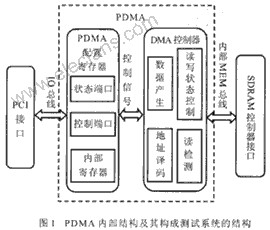

847 我們?cè)O(shè)計(jì)了一個(gè)PDMA(Programmable Direct Mem o ry Access)用于測(cè)試SDRAM控制器的性能。在SoC中,SDRAM控制器往往跟多個(gè)IP模塊(圖形處理單元,音頻處理單元等)交換數(shù)據(jù),采用多個(gè)PDMA通道

2010-07-02 18:31:41 1655

1655

SDRAM存儲(chǔ)芯片擁有快速讀寫的性能,可以應(yīng)用以回波模擬系統(tǒng)作為數(shù)據(jù)高速緩存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有嚴(yán)格的控制時(shí)序和工作狀態(tài),可以使用有限狀態(tài)機(jī)理論

2011-10-24 15:08:05 0

0 通過設(shè)計(jì)基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等單片機(jī)和DSP等微處理器的外部連接SDRAM,增加系統(tǒng)的存儲(chǔ)空間。

2012-02-16 17:06:47 45

45 TFT控制命令,SD卡的控制命令解析,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-06 14:24:46 0

0 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 高速圖像存儲(chǔ)系統(tǒng)中SDRAM控制器的實(shí)現(xiàn)

2016-08-29 15:02:03 10

10 華清遠(yuǎn)見FPGA代碼-SDRAM讀寫控制的實(shí)現(xiàn)與Modelsim仿真

2016-10-27 18:07:54 26

26 一種面向多核系統(tǒng)的DDR2SDRAM控制單元_章裕

2017-01-03 18:00:37 5

5 基于VHDL的SDRAM控制器的實(shí)現(xiàn)

2017-01-22 13:43:27 12

12 DDR2SDRAM控制器在機(jī)載顯控系統(tǒng)中的應(yīng)用_孫少偉

2017-03-19 11:26:54 1

1 字電視接收機(jī)的生產(chǎn)實(shí)際應(yīng)用中,不同廠家的PCB板布線、PCB材料和時(shí)鐘頻率的不同,及SDRAM型號(hào)和器件一致性不同等原因,都會(huì)帶來解碼主芯片與SDRAM間訪問時(shí)序的抖動(dòng)問題。 數(shù)字電視系統(tǒng) SDRAM時(shí)序控制 AVIA9700內(nèi)集成了一個(gè)SDRAM控制器,該控制器提供一套完整

2017-10-16 15:58:16 2

2 EPM1240的SDRAM控制器的設(shè)計(jì)

2017-10-31 08:24:31 21

21 在很多通信芯片及系統(tǒng)的開發(fā)中,常常需要用到存儲(chǔ)容量大、讀寫速度快的存儲(chǔ)器。在各種隨機(jī)存儲(chǔ)器件中,SDRAM的價(jià)格低、體積小、速度快、容量大,是比較理想的器件。但是,與SRAM相比較,SDRAM的控制

2017-11-28 19:51:26 5

5 現(xiàn)代的處理器(SoC)或DSP都內(nèi)建有內(nèi)存控制器,它是外部SDRAM、FLASH、EEPROM、SRAM等內(nèi)存的控制接口。但不同處理器內(nèi)部的內(nèi)存控制方式都不盡相同,而且它們的控制程序大部分都位于開機(jī)

2017-12-01 01:56:33 420

420 隨著大規(guī)模集成電路和高速、低功耗、高密度存儲(chǔ)技術(shù)的發(fā)展,SDRAM動(dòng)態(tài)存儲(chǔ)器因容量大、速度快、價(jià)格低廉等優(yōu)點(diǎn),現(xiàn)已成為PC內(nèi)存的主流。然而SDRAM存儲(chǔ)器內(nèi)部控制邏輯十分復(fù)雜,時(shí)序要求也非常嚴(yán)格,因此需要設(shè)計(jì)專門的SDRAM控制器來實(shí)現(xiàn)系統(tǒng)對(duì)SDRAM的訪問。

2018-04-30 10:58:00 5070

5070

所以SDRAM需要在電容的電量放完之前進(jìn)行刷新;隨機(jī)是指數(shù)據(jù)不是線性依次存儲(chǔ),而是自由指定地址進(jìn)行數(shù)據(jù)的讀寫。” 這只是對(duì)SDRAM的概念介紹,下面再簡(jiǎn)單的看一下SDRAM的內(nèi)部結(jié)構(gòu)。

2018-03-29 09:30:54 7543

7543

問:如何操作SDRAM的自刷新命令而不影響正常讀寫操作? 眾所周知,SDRAM從開始工作伊始,一直伴隨著64ms刷新一遍的最基本規(guī)定(假設(shè)該SDRAM有4096行,那么必須大約15us的時(shí)間就要發(fā)出

2018-06-20 10:41:32 10513

10513

操作,設(shè)計(jì)了DDR SDRAM 的數(shù)據(jù)與命令接口。用控制核來簡(jiǎn)化對(duì)DDR SDRAM 的操作,并采用自頂至下模塊化的設(shè)計(jì)方法,將控制核嵌入到整個(gè)數(shù)據(jù)采集系統(tǒng)的控制模塊中,完成了數(shù)據(jù)的高速采集、存儲(chǔ)及上傳

2019-08-14 08:00:00 3401

3401

無效時(shí),SDRAM內(nèi)部所有與輸入相關(guān)的功能模塊停止工作 (3)CS#:片選信號(hào),為輸入信號(hào),低電平有效。只有當(dāng)片選信號(hào)有效后,SDRAM才能識(shí)別控制器發(fā)送來的命令。設(shè)計(jì)時(shí)注意上拉 (4)RAS#

2018-10-09 15:22:29 4809

4809 眾所周知,SDRAM從開始工作伊始,一直伴隨著64ms刷新一遍的最基本規(guī)定(假設(shè)該SDRAM有4096行,那么必須大約15us的時(shí)間就要發(fā)出一次自刷新命令),這是為了保持SDRAM內(nèi)數(shù)據(jù)能夠在上電以后一直保持的原因,具體原因就不多解釋了,我們還是以實(shí)際操作為主。

2018-12-12 14:04:59 5030

5030 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA讀寫SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文主要包括了:FPGA讀寫SDRAM的實(shí)例,SDRAM控制器核心介紹,系列SDRAM數(shù)據(jù)手冊(cè)

2018-12-25 08:00:00 56

56 SDRAM是多Bank結(jié)構(gòu),例如在一個(gè)具有兩個(gè)Bank的SDRAM的模組中,其中一個(gè)Bank在進(jìn)行預(yù)充電期間,另一個(gè)Bank卻馬上可以被讀取,這樣當(dāng)進(jìn)行一次讀取后,又馬上去讀取已經(jīng)預(yù)充電Bank的數(shù)據(jù)時(shí),就無需等待而是可以直接讀取了,這也就大大提高了存儲(chǔ)器的訪問速度。

2019-11-25 07:00:00 1938

1938 無效時(shí),SDRAM內(nèi)部所有與輸入相關(guān)的功能模塊停止工作 (3)CS#:片選信號(hào),為輸入信號(hào),低電平有效。只有當(dāng)片選信號(hào)有效后,SDRAM才能識(shí)別控制器發(fā)送來的命令。設(shè)計(jì)時(shí)注意上拉 (4)RAS#

2019-07-15 15:35:23 3633

3633 SDRAM是同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器的縮寫。在微控制器應(yīng)用中,微控制器通過使用外部存儲(chǔ)控制器(EMC)操作訪問SDRAM ,SDRAM時(shí)鐘頻率通常為100MHz或133MHz。

2019-11-23 11:38:01 6043

6043

、PSRAM、MRAM等存儲(chǔ)芯片供應(yīng)商英尚微電子解析這款比腦力更強(qiáng)大的DDR SDRAM控制器。 任何DRAM控制器背后的智商都是與命令時(shí)序和執(zhí)

2020-07-24 14:25:27 719

719 動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器的縮寫。在微控制器應(yīng)用中,微控制器通過使用外部存儲(chǔ)控制器(EMC)操作訪問 SDRAM ,SDRAM 時(shí)鐘頻率通常為 100MHz 或 133MHz。外部存儲(chǔ)控制器通常不支持 DDR SDRAM, 數(shù)據(jù)只是單邊沿采樣,即并行數(shù)據(jù)總線可以接受一個(gè)命令并在每個(gè)時(shí)鐘周期傳輸一個(gè)數(shù)據(jù)字。在 S

2020-12-23 12:18:00 10

10 針對(duì)SDRAM 操作繁瑣的問題,在對(duì)SDRAM 存儲(chǔ)器和全頁(yè)突發(fā)式操作進(jìn)行研究的基礎(chǔ)上,提出一種簡(jiǎn)易SDRAM 控制器的設(shè)計(jì)方法。該設(shè)計(jì)方法充分利用全頁(yè)式高效率存取的優(yōu)點(diǎn),對(duì)SDRAM 進(jìn)行配置、全頁(yè)突發(fā)式讀寫時(shí),操作方便。在實(shí)現(xiàn)sDRAM 的快速批量存儲(chǔ)方面,具有良好的應(yīng)用價(jià)值。

2020-12-18 16:13:18 6

6 SDRAM作為大容量存儲(chǔ)器在高速圖像處理中具有很大的應(yīng)用價(jià)值。但由于SDRAM的結(jié)構(gòu)和SRAM不同,其控制比較復(fù)雜。文章詳細(xì)介紹了 SDRAM存儲(chǔ)器的結(jié)構(gòu)、接口信號(hào)和操作方法,以及 SDRAM控制

2021-01-26 15:30:52 13

13 1.SDRAM使用越來越廣泛。

2.SDRAM具有存儲(chǔ)容量大,速率快的特點(diǎn)。

3.SDRAM對(duì)時(shí)序要求嚴(yán)格,需要不斷刷新保持?jǐn)?shù)據(jù)。

.FPGA在電子設(shè)計(jì)中的廣泛應(yīng)用,使用十分靈活利用FPGA來設(shè)計(jì)自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 linux基本命令說明參數(shù)講解教程說明。

2021-03-25 16:00:10 9

9 本文首先分析了DDR SDRAM的基本特征,并提出了相應(yīng)的解決方案詳細(xì)介紹了基于J EDEC DDR SDRAM規(guī)范的DDR SDRAM控制器設(shè)計(jì)方案。該控制器采用Verilog HDL硬件描述語(yǔ)言實(shí)現(xiàn),并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 EE-127:ADSP-21065L片上SDRAM控制器

2021-04-16 10:12:57 3

3 EE-163:ADSP-21161N SHARC片上SDRAM控制器

2021-04-17 16:44:17 12

12 ,SDRAM的控制邏輯復(fù)雜,使用很不方便。 為了解決這個(gè)矛盾,需要設(shè)計(jì)專用的SDRAM控制器,使系統(tǒng)用戶象使用SRAM一樣方便的使用SDRAM是十分必要的。考慮到控制器的通用性,本文提出了一種通用的SDRAM控制器的 Verilog設(shè)計(jì),并給出了實(shí)現(xiàn)結(jié)果。 1 SDRAM的工作原理

2021-06-30 09:16:47 2346

2346

基于可編程邏輯的SDRAM控制方法設(shè)計(jì)

2021-06-30 10:16:14 8

8 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡(jiǎn)介(arm嵌入式開發(fā)平臺(tái)PB)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡(jiǎn)介資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)簡(jiǎn)介(嵌入式開發(fā)工程師和基層公務(wù)員)-該文檔為基于FPGA的SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)簡(jiǎn)介文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)(嵌入式開發(fā)式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 (網(wǎng)盤)關(guān)于SDRAM和錄音機(jī)等FPGA視頻(android嵌入式開發(fā)教程)-關(guān)于SDRAM和錄音機(jī)等FPGA視頻,一步一步的講解,真的很詳細(xì),適合大家自學(xué)研究。

2021-08-04 12:21:50 15

15 6個(gè)有趣的Linux命令案例講解

2021-08-11 17:49:53 12

12 Memcache系統(tǒng)常用命令講解(無線電源技術(shù)商業(yè)計(jì)劃書)-該文檔為Memcache系統(tǒng)常用命令講解文檔,是一份還算不錯(cuò)的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-28 11:27:02 5

5 上圖中,把SDRAM用到的所有指令都羅列出來了,其實(shí)我們?cè)谶\(yùn)用SDRAM的時(shí)候,只用到其中部分指令。例如其中write/write with autoprecharge,這兩個(gè)指令我們都可以對(duì)SDRAM進(jìn)行寫操作,只是說在” writewith autoprecharge”指令

2022-05-09 10:09:29 2228

2228 SDRAM 控制器用戶手冊(cè)主要內(nèi)容包括功能特點(diǎn)、整體框圖、工作原理、

信號(hào)定義、參數(shù)介紹、GUI 調(diào)用、接口時(shí)序等。主要用于幫助用戶快速了解

高云半導(dǎo)體 SDRAM 控制器的產(chǎn)品特性、特點(diǎn)及使用方法。

2022-09-15 15:17:29 0

0 今天浩道跟大家分享一篇關(guān)于講解top命令的硬核干貨,個(gè)人覺得本文羅列的實(shí)例比我平時(shí)關(guān)注的要詳細(xì)得多,所以分享給大家學(xué)習(xí)!

2023-01-30 17:30:55 4331

4331 我們可以利用這個(gè)命令對(duì)Wire進(jìn)行Cut的操作,再結(jié)合editSelect/editDelete等命令,我們可以實(shí)現(xiàn)對(duì)任意的Wire執(zhí)行切割刪除等操作。

2023-05-26 09:12:49 1297

1297

實(shí)時(shí)視頻SDRAM控制器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2022-12-30 09:21:26 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論