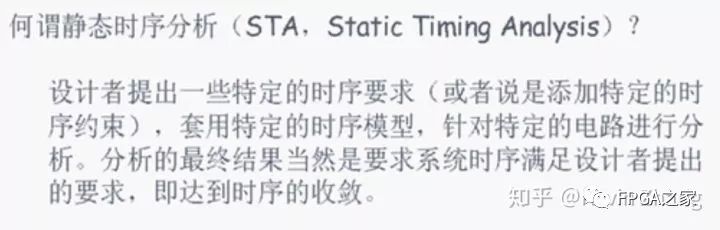

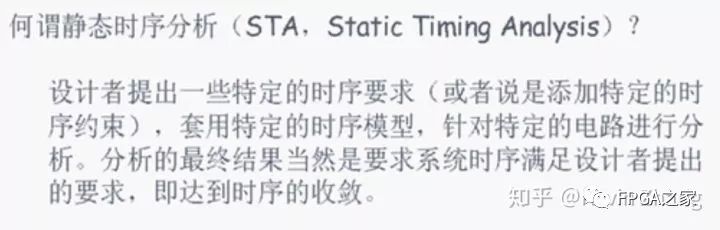

什么是靜態時序分析?

通俗來說:在輸入信號到輸出信號中,因為經過的傳輸路徑、寄存器、門電路等器件的時間,這個時間就是時序。開發工具不知道我們路徑上的要求,我們通過時序約束來告訴開發工具,根據要求,重新規劃,從而實現我們的時序要求,達到時序的收斂。

我們對整個設計添加時序約束,讓整個設計。

時序的欠約束:約束的少了;

時序的過約束:約束了過了;

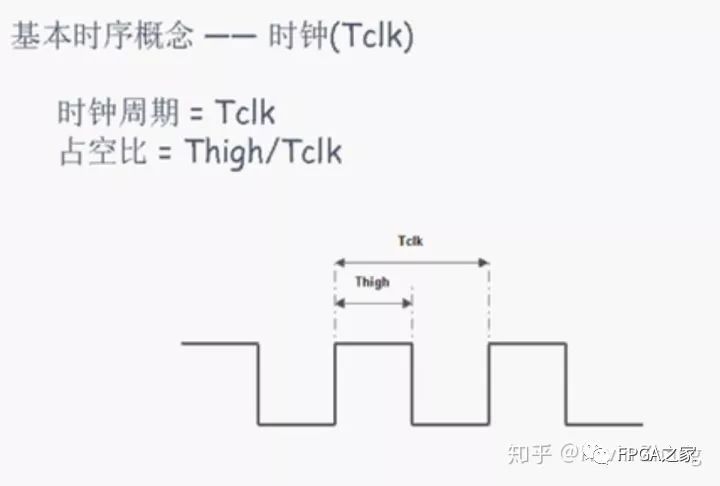

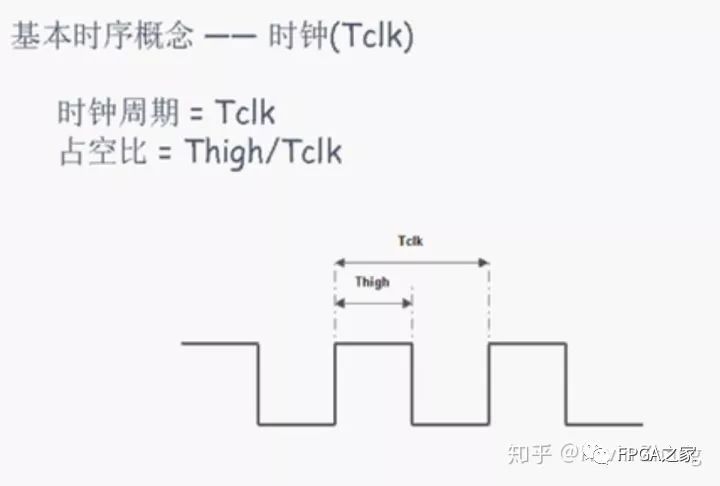

時序基本概念:時鐘

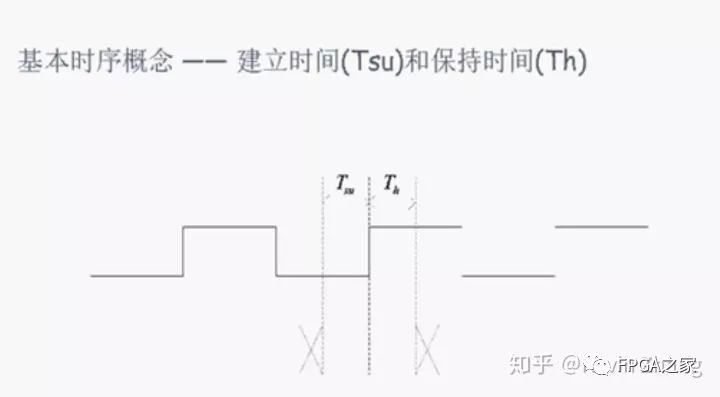

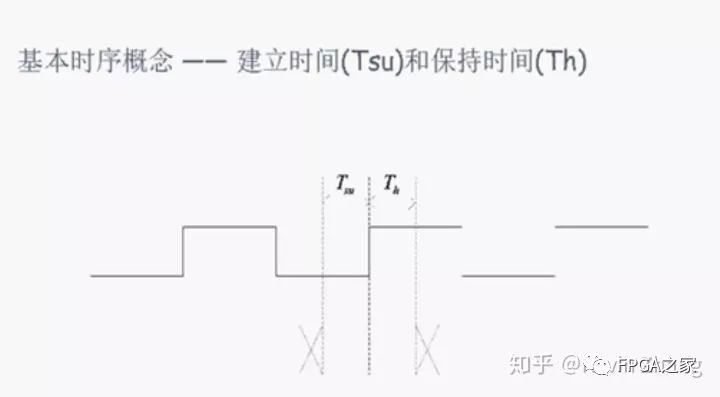

建立時間setup和保持時間hold

建立時間:在時鐘上升沿前,數據不能改變的最小時間;

保持時間:在數據上升沿后,數據不能改變的最小時間;

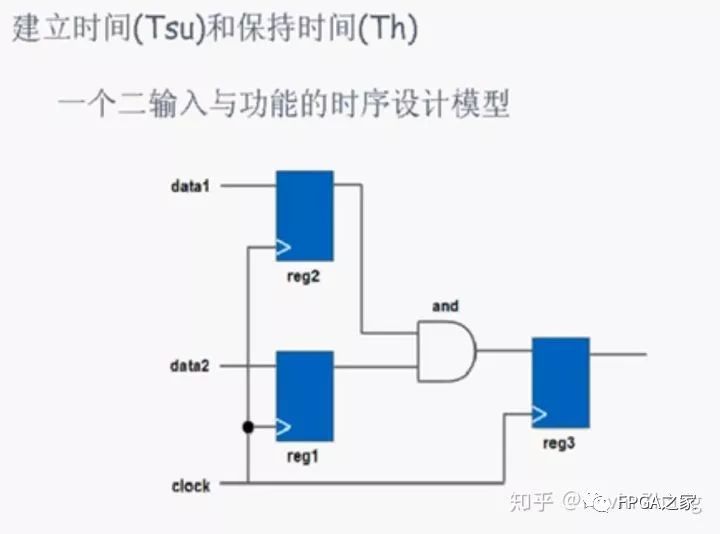

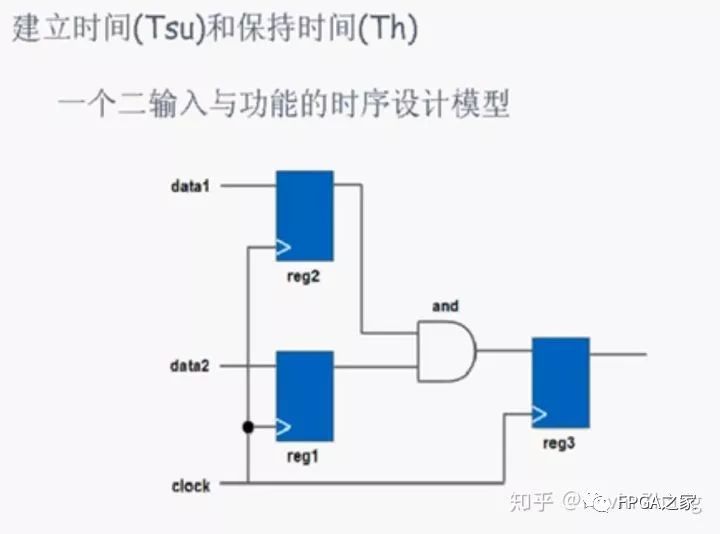

例子

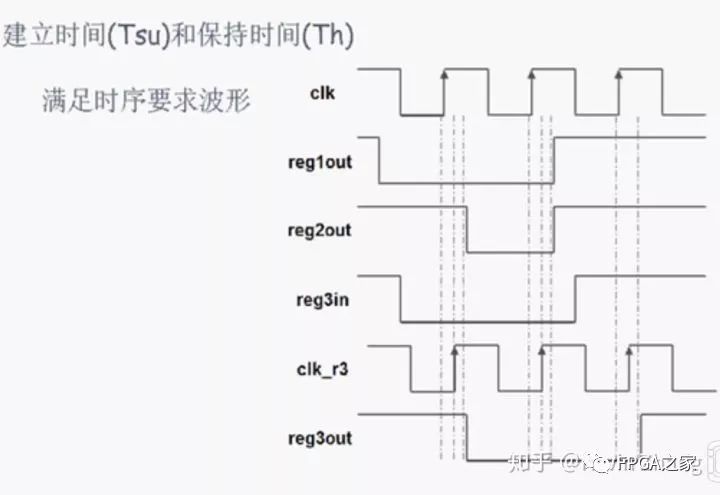

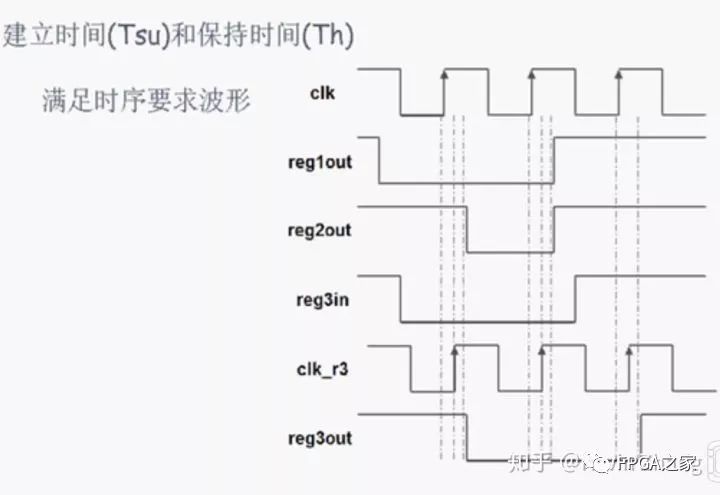

滿足reg的時間符合

滿足reg的時間符合

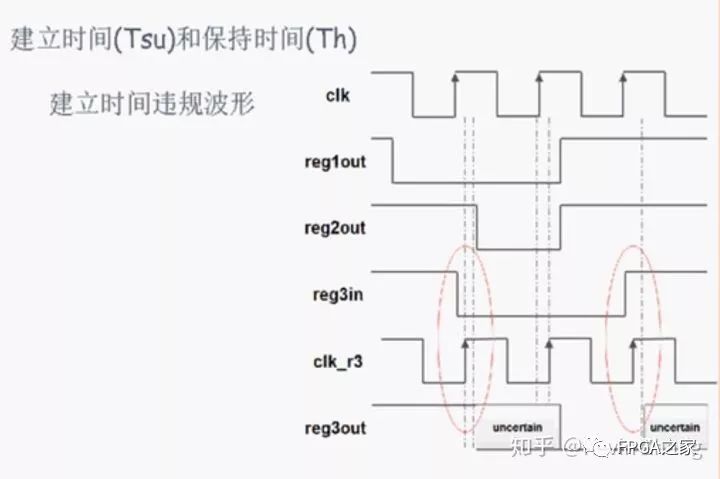

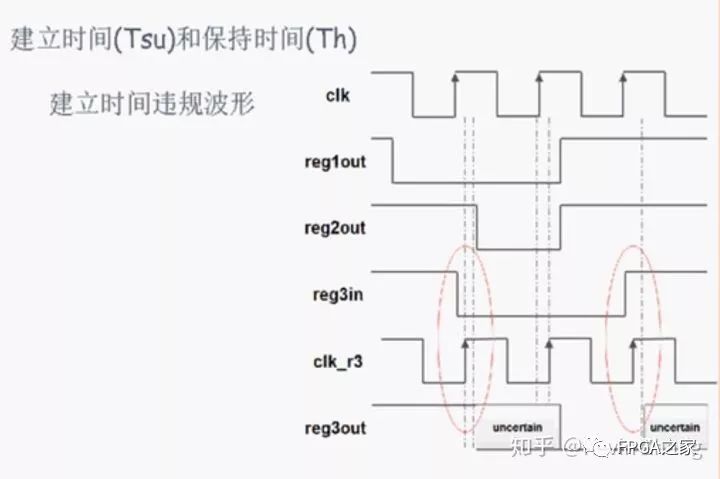

建立REG3 setup時間違規,導致輸出不確定

建立REG3 setup時間違規,導致輸出不確定

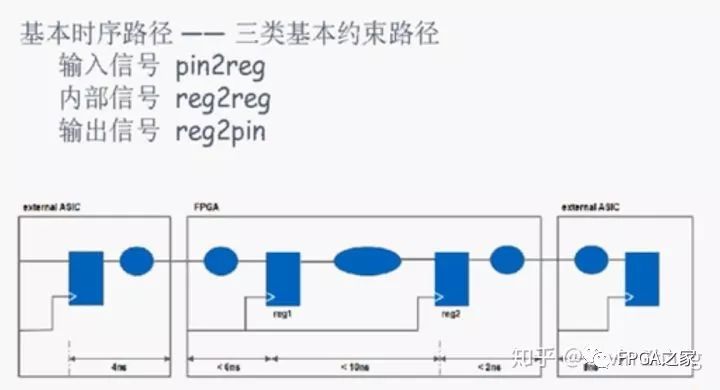

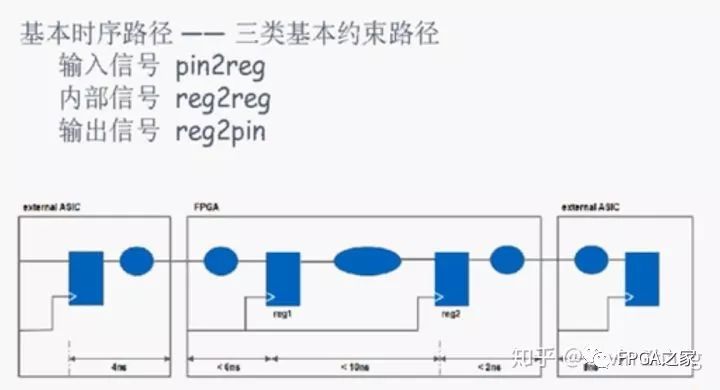

三種時序路徑

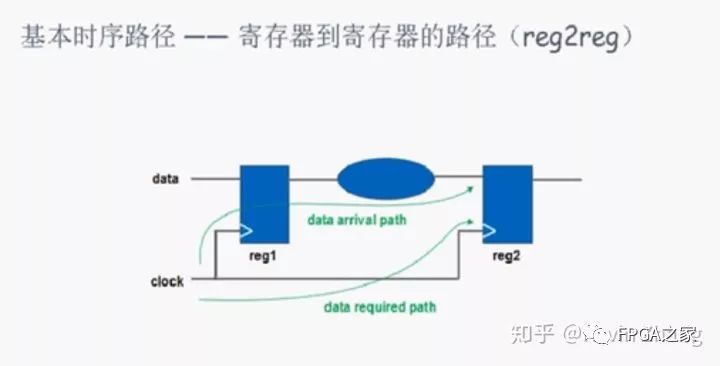

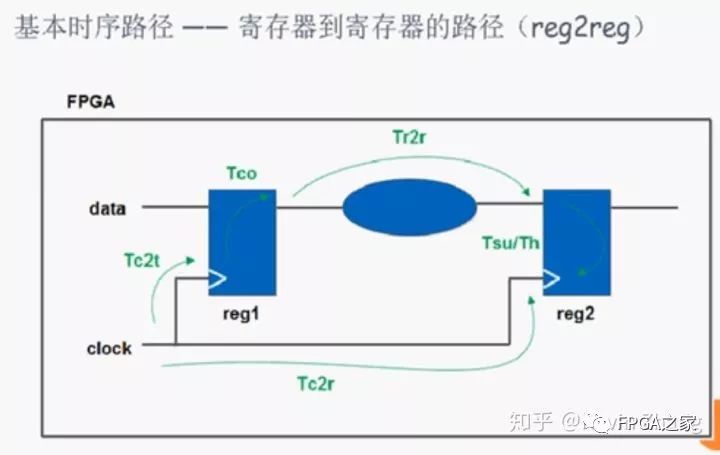

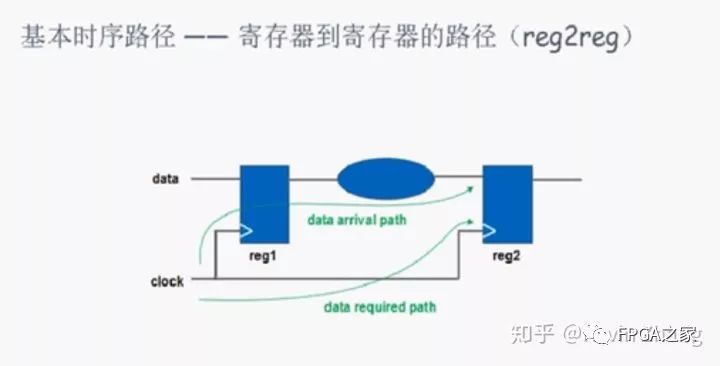

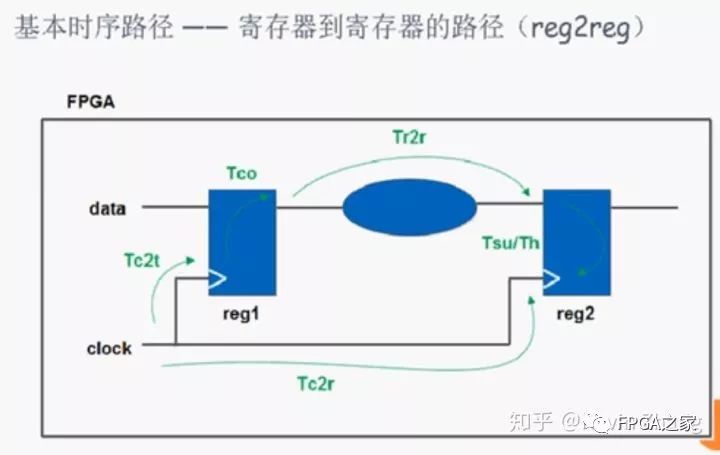

分析一個寄存器的延時

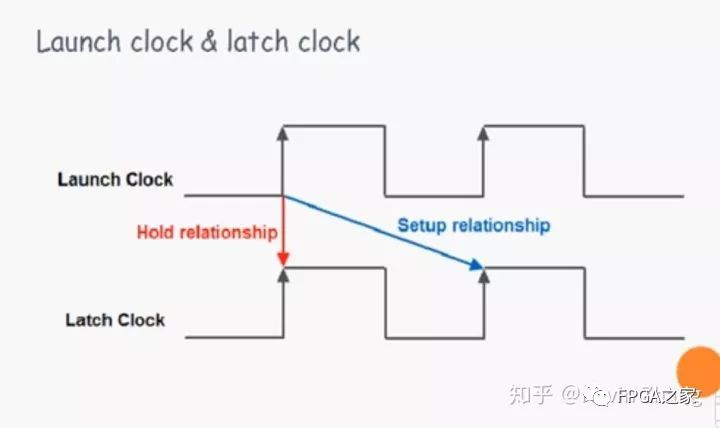

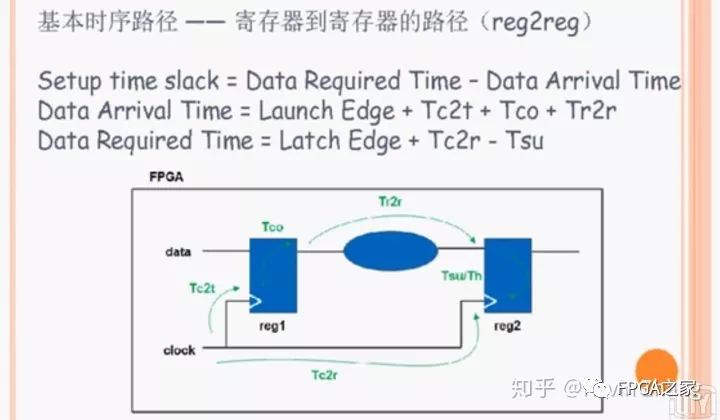

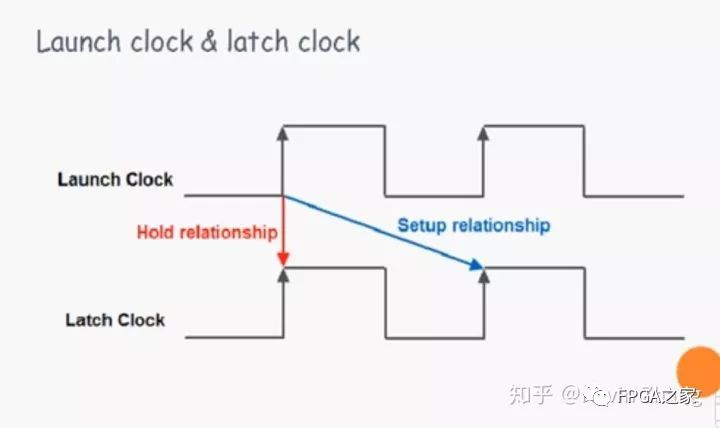

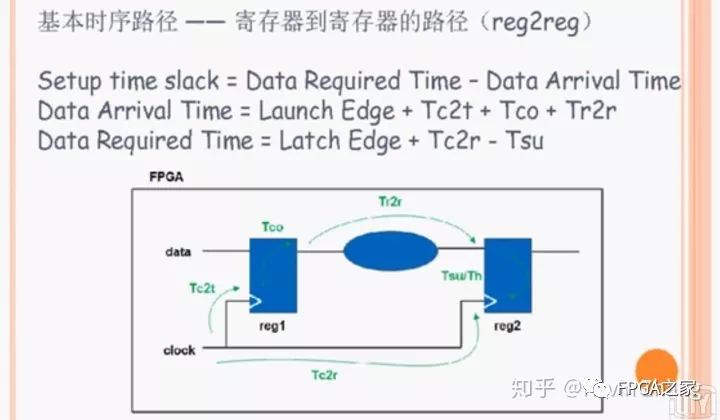

setup slack余量,這個時間是差了一個時鐘周期;

數據達到時間,首先是發射時鐘+時鐘到REG1的延時+reg1的延時+傳輸路徑的延時

數據時間需求:鎖存時鐘+時鐘到reg2的延時-setup時間

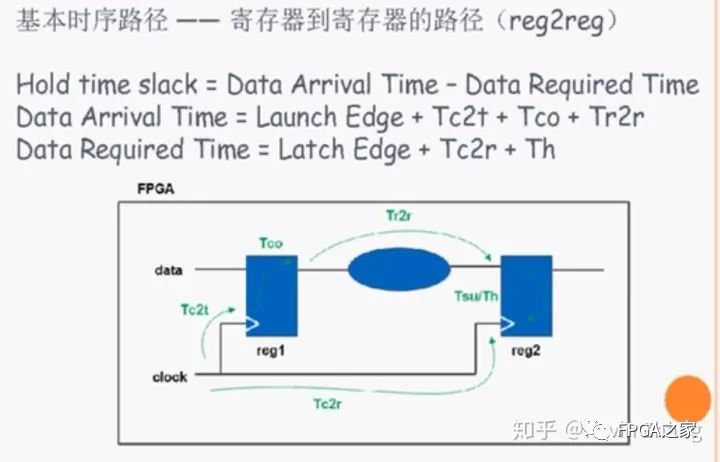

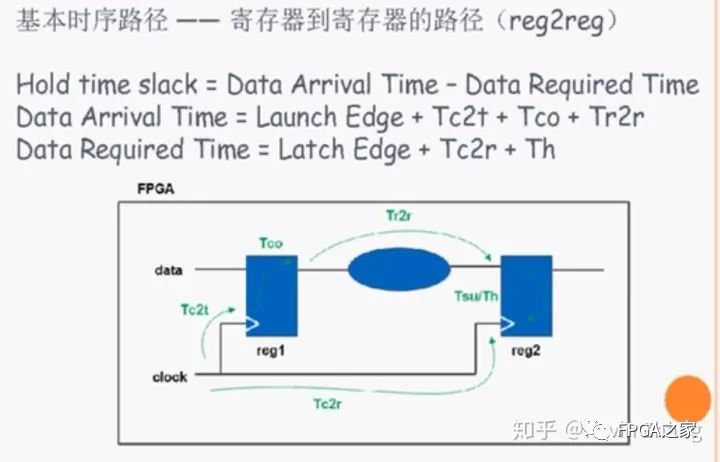

hold時間余量,這里分析的應該是同一個周期里面的時間,這個時間是對齊的;

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:FPGA學習-時序分析基礎001

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

相關推薦

xilinx FPGA IOB約束使用以及注意事項 一、什么是IOB約束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是

![的頭像]() 發表于

發表于 01-16 11:02

?126次閱讀

Constraints窗口,clocks選擇Create Clock,單擊添加圖標或雙擊Create Clock,進入創建窗口 Create Clock窗口中,Clock name為時鐘約束命名,Source obj

![的頭像]() 發表于

發表于 11-29 11:03

?620次閱讀

約束使用說明-v1

文章出處:【微信公眾號:易靈思FPGA技術交流】歡迎添加關注!文章轉載請注明出處。

![的頭像]() 發表于

發表于 11-01 11:06

?250次閱讀

電子發燒友網站提供《FPGA電源時序控制.pdf》資料免費下載

發表于 08-26 09:25

?0次下載

建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

![的頭像]() 發表于

發表于 08-06 11:40

?806次閱讀

吧。

1、設計初期,要考慮的是需要多少邏輯資源、IO口、信號電平、功耗,如何劃分模塊等。

2、確定了1中的需求后,就要根據原理圖,進行底層的設計輸入工作。整個設計工作,需要開發工具以及仿真軟件,檢查

發表于 06-23 14:47

Static Timing Analysis,簡稱 STA。它可以簡單的定義為:設計者提出一些特定的時序要求(或者說是添加特定的時序約束),套用特定的

發表于 06-17 17:07

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法

為了保證成功的設計,所有路徑的時序要求

發表于 05-06 15:51

詳細的原時鐘時序、數據路徑時序、目標時鐘時序的各延遲數據如下圖所示。值得注意的是數據路徑信息,其中包括Tco延遲和布線延遲,各級累加之后得到總的延遲時間。

發表于 04-29 10:39

?921次閱讀

添加約束的目的是為了告訴FPGA你的設計指標及運行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請注意該文件不能

![的頭像]() 發表于

發表于 04-28 18:36

?2413次閱讀

在FPGA開發過程中,配置全局時鐘是一個至關重要的步驟,它直接影響到整個系統的時序和性能。以下是配置全局時鐘時需要注意的一些關鍵問題:

時鐘抖動和延遲 :全局時鐘資源的設計目標是實現最

發表于 04-28 09:43

LOC約束是FPGA設計中最基本的布局約束和綜合約束,能夠定義基本設計單元在FPGA芯片中的位置,可實現絕對定位、范圍定位以及區域定位。

發表于 04-26 17:05

?1333次閱讀

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設計,所有路徑的時序要求

發表于 04-12 17:39

設計的代碼風格有明顯差異,特別是在功耗、速度、時序等要求上。例如ASIC設計中根據要求會有意識地采用某些組合邏輯、門控時鐘等,以降低功耗或提高速度。

第三章詳細介紹了FPGA的開發流程

發表于 03-29 16:42

FPGA時序仿真和功能仿真在芯片設計和驗證過程中各自扮演著不可或缺的角色,它們之間存在明顯的區別。

![的頭像]() 發表于

發表于 03-15 15:28

?2419次閱讀

FPGA開發中如何對整個設計添加時序約束

FPGA開發中如何對整個設計添加時序約束

評論