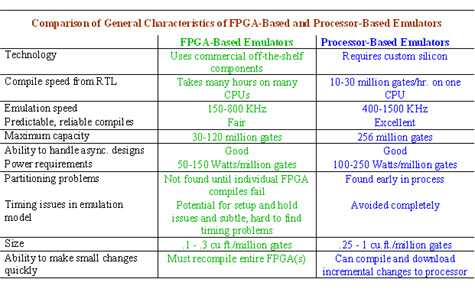

工程師更廣泛地理解基于FPGA的仿真,因?yàn)楣こ處熈?xí)慣于使用FPGA進(jìn)行設(shè)計(jì)。對(duì)基于處理器的仿真器的理解不太了解,而且有大量錯(cuò)誤信息的例子比比皆是。本文將嘗試消除解釋基于處理器的仿真如何工作以及如何將設(shè)計(jì)構(gòu)造映射到其中的謎團(tuán),例如三態(tài)總線(xiàn),復(fù)雜存儲(chǔ)器和異步時(shí)鐘。

早期基于處理器的仿真

在1990年代早期,IBM開(kāi)創(chuàng)了基于處理器的仿真技術(shù),這是他們?cè)缙诠ぷ鞯囊粋€(gè)分支。基于硬件的仿真引擎。硬件技術(shù)由大量布爾處理器組成,這些處理器能夠以非常高的速度相互共享數(shù)據(jù)。軟件技術(shù)包括在許多處理器之間劃分設(shè)計(jì),并以正確的時(shí)間順序和最佳方式調(diào)度各個(gè)布爾運(yùn)算。

最初,性能無(wú)法與基于FPGA的仿真器匹配,但編譯時(shí)間不到一小時(shí),消除了困擾基于FPGA的仿真器的時(shí)序問(wèn)題,使新技術(shù)對(duì)許多使用模型很有吸引力,特別是模擬加速。該技術(shù)的后代最終在仿真速度上超越了FPGA系統(tǒng),同時(shí)保留了編譯時(shí)間的巨大優(yōu)勢(shì)?并且沒(méi)有一百臺(tái)PC的農(nóng)場(chǎng)用于編譯。

軟件技術(shù)的進(jìn)步擴(kuò)展了基于處理器的仿真器的應(yīng)用,以處理具有任意數(shù)量時(shí)鐘的異步設(shè)計(jì)。其他擴(kuò)展支持設(shè)計(jì)中所有信號(hào)的100%可見(jiàn)性,從仿真運(yùn)行開(kāi)始的任何時(shí)間對(duì)所有信號(hào)的可見(jiàn)性,以及邏輯分析器觸發(fā)事件的動(dòng)態(tài)設(shè)置,無(wú)需重新編譯。在基于FPGA的系統(tǒng)的仿真速度不斷降低的同時(shí),新一代基于處理器的系統(tǒng)不僅以驚人的速度提高了仿真速度,而且還證明了其容量可擴(kuò)展到數(shù)億個(gè)門(mén)。

基于處理器的仿真器架構(gòu)

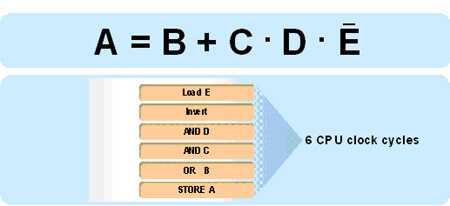

了解處理器的方式基于仿真器的工作原理,簡(jiǎn)要回顧一下邏輯仿真器的工作原理很有用。回想一下,計(jì)算機(jī)的ALU(算術(shù)邏輯單元)可以對(duì)變量執(zhí)行基本的布爾運(yùn)算,例如AND,OR,NOT,并且諸如“always @(posedge Clock)Q = D”之類(lèi)的語(yǔ)言構(gòu)造構(gòu)成了a的基礎(chǔ)。拖鞋。

在門(mén)(和透明鎖存器)的情況下,模擬順序很重要。信號(hào)通過(guò)門(mén)鏈?zhǔn)疽庑缘亍皬淖蟮接摇备?jìng)爭(zhēng),或者在RTL源代碼中“從上到下”。觸發(fā)器(寄存器)打破門(mén)鏈以進(jìn)行排序。

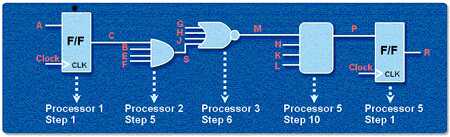

圖1 ??邏輯模擬; CPU對(duì)信號(hào)執(zhí)行布爾運(yùn)算,寄存器

一種類(lèi)型的模擬器,一個(gè)分級(jí)編譯邏輯模擬器,以正確的順序一次一個(gè)地執(zhí)行布爾方程。 (時(shí)間延遲與功能邏輯仿真無(wú)關(guān)。)如果有兩個(gè)ALU可用,您可以想象將設(shè)計(jì)分解為兩個(gè)獨(dú)立的邏輯鏈并將每個(gè)鏈分配給ALU,從而并行化并減少所需的時(shí)間,也許是一半。

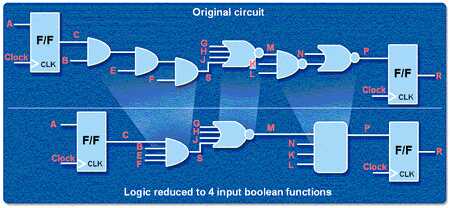

基于處理器的仿真器具有數(shù)萬(wàn)到數(shù)十萬(wàn)個(gè)ALU,這些ALU可以有效地進(jìn)行調(diào)度,以正確的順序執(zhí)行設(shè)計(jì)中的所有布爾方程。以下系列圖紙說(shuō)明了這一過(guò)程。對(duì)于此示例,我們假設(shè)模擬器中有一個(gè)4輸入布爾基元。

圖2 ??步驟1:將布爾邏輯簡(jiǎn)化為四輸入函數(shù)

將邏輯簡(jiǎn)化為四輸入函數(shù)后的布爾方程組是:

IF(時(shí)鐘上升) C = A

S = C& B& E& F

M = NOT(G + H + J + S)

P = NOT(N + NOT(M& K& L))

IF(時(shí)鐘上升)R = P

此外,以下排序約束集適用:

必須首先評(píng)估觸發(fā)器

必須在M之前計(jì)算S

M必須在P

之前計(jì)算

在計(jì)算S之前必須對(duì)主輸入B,E和F進(jìn)行采樣

在計(jì)算M之前必須對(duì)主輸入G,H和J進(jìn)行采樣

在計(jì)算P之前必須對(duì)主輸入K,L和N進(jìn)行采樣

注意:在觸發(fā)器之后的任何時(shí)間都可以對(duì)主輸入A進(jìn)行采樣

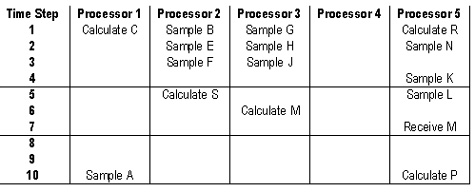

上面顯示了一種可能的調(diào)度。這是出于說(shuō)明目的而完成的,并且可能不是最有效的調(diào)度。

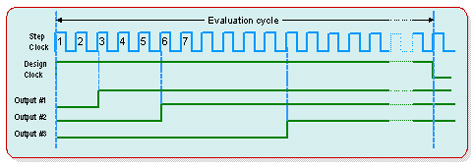

圖3 ??調(diào)度邏輯的結(jié)果

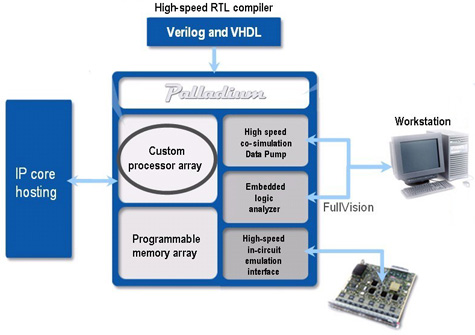

圖4 ??基于處理器的仿真器架構(gòu)

仿真周期包括運(yùn)行所有處理器步驟以完成設(shè)計(jì)的完整建模。大型設(shè)計(jì)通常安排在125? 320步。如果設(shè)計(jì)可以使用1x時(shí)鐘(稍后描述),則基于處理器的仿真器的仿真速度將在600KHz和1.5MHz之間。

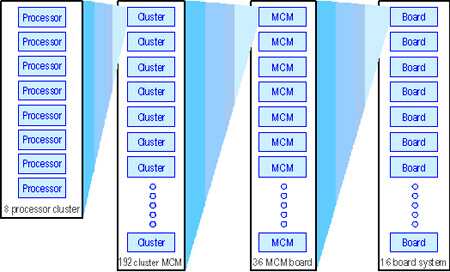

在每個(gè)時(shí)間步驟中,每個(gè)處理器都能夠執(zhí)行任何4輸入邏輯功能,使用任何處理器的任何先前計(jì)算結(jié)果和任何設(shè)計(jì)輸入或存儲(chǔ)器內(nèi)容作為輸入。處理器在集群中物理實(shí)現(xiàn),在集群內(nèi)快速通信。編譯器優(yōu)化處理器調(diào)度以最大化速度和容量。

圖5 ??處理器陣列架構(gòu)示例

設(shè)計(jì)編譯

RTL設(shè)計(jì)的編譯完全自動(dòng)化,并按以下順序完成:

1)將RTL代碼映射到原始單元,例如門(mén)和寄存器。

2)合成存儲(chǔ)器。

3)展平設(shè)計(jì)的層次結(jié)構(gòu)。

4)將布爾邏輯(門(mén))減少為4 - 輸入功能。

5)通過(guò)在最佳位置插入寄存器來(lái)中斷設(shè)計(jì)中的異步循環(huán)。

6)為目標(biāo)系統(tǒng)和任何硬IP分配外部連接。

7)設(shè)置任何需要的儀表邏輯(例如邏輯分析儀“視覺(jué)”)。

8)以統(tǒng)一的方式將所有設(shè)計(jì)輸入和輸出分配給處理器。

9)將設(shè)計(jì)中的每個(gè)單元分配給處理器。優(yōu)先考慮將具有公共輸入和/或輸出的信元分配給相同的處理器或集群,并為每個(gè)處理器分配相同數(shù)量的信元。

10)將每個(gè)處理器的活動(dòng)安排為連續(xù)的時(shí)間步長(zhǎng)。目標(biāo)是最小化最大時(shí)間步數(shù)。

編譯器還必須考慮模擬加速連接,三態(tài)總線(xiàn)建模,內(nèi)存建模,非均勻處理器連接,邏輯分析儀探測(cè)和觸發(fā)等因素。

但編譯器無(wú)需處理FPGA仿真器中高度可變的FPGA內(nèi)部時(shí)序。因此,基于處理器的仿真編譯速度更快,資源更少。盡管執(zhí)行了布爾優(yōu)化,編譯器仍會(huì)維護(hù)所有最初指定的RT級(jí)網(wǎng)名,以便在調(diào)試中使用。這允許用戶(hù)使用他們熟悉的信號(hào)名稱(chēng)進(jìn)行調(diào)試。

三態(tài)總線(xiàn)建模

三態(tài)總線(xiàn)采用組合邏輯建模。當(dāng)沒(méi)有啟用任何啟用時(shí),用戶(hù)可以選擇“上拉”,“下拉”或“保留狀態(tài)”。在后一種情況下,當(dāng)沒(méi)有啟用驅(qū)動(dòng)器時(shí),將鎖存器插入設(shè)計(jì)中以保持總線(xiàn)的狀態(tài)。在多個(gè)使能開(kāi)啟的情況下,對(duì)于上拉和保持狀態(tài)邏輯0將“贏(yíng)”并且對(duì)于下拉邏輯1將獲勝。 (注意:這是使用斷言的好地方。)

異步循環(huán)中斷

由于仿真器不對(duì)門(mén)級(jí)硅時(shí)序建模,因此異步循環(huán)會(huì)自動(dòng)中斷編譯期間的延遲觸發(fā)器。編譯器將自動(dòng)中斷異步循環(huán)而無(wú)需用戶(hù)干預(yù)。

但是,通過(guò)允許用戶(hù)指定應(yīng)該發(fā)生循環(huán)中斷的位置,可以提高性能,因?yàn)榛谔幚砥鞯姆抡嫫鞯男阅芘c長(zhǎng)組合路徑的長(zhǎng)度有關(guān)。通過(guò)插入延遲元件來(lái)打破錯(cuò)誤路徑或多時(shí)鐘周期路徑,如果這些路徑是設(shè)計(jì)的關(guān)鍵路徑,則可以提高性能。

長(zhǎng)組合路徑

仿真器的處理器使用特定深度的指令“堆棧”運(yùn)行,例如160個(gè)字。這些是設(shè)計(jì)計(jì)算順序的時(shí)間步驟。

有時(shí),設(shè)計(jì)中可能會(huì)有一個(gè)非常長(zhǎng)的組合路徑,無(wú)法將其安排到可用的連續(xù)步驟數(shù)中。注意,這并不一定意味著邏輯路徑具有更多“門(mén)級(jí)”,因?yàn)檎{(diào)度必須考慮許多時(shí)間序列約束。

在這種情況下,調(diào)度程序?qū)⑼ㄟ^(guò)使用未使用的處理器時(shí)間步驟在第二遍中調(diào)度剩余的布爾運(yùn)算來(lái)完成路徑。這也可能是因?yàn)閲L試將太多的門(mén)擠入仿真器,但是,作為一個(gè)好處,它提供了用戶(hù)權(quán)衡仿真速度與容量的關(guān)系。

基于處理器的仿真器中的時(shí)鐘處理

如前所述,時(shí)鐘是基于FPGA的仿真器不可靠性的主要來(lái)源之一。基于處理器的仿真器完全避免了這個(gè)問(wèn)題,因?yàn)樗鼈兛梢陨稍O(shè)計(jì)所需的所有時(shí)鐘或接受外部生成的時(shí)鐘。

讓仿真器生成所需的所有設(shè)計(jì)時(shí)鐘會(huì)更方便嗎?它運(yùn)行得更快。您可以指定每個(gè)時(shí)鐘的頻率,也可以讓編譯器從測(cè)試平臺(tái)中提取此信息(如果有的話(huà))。某些基于處理器的仿真器允許您從目標(biāo)系統(tǒng)向仿真器提供外部時(shí)鐘。在這種情況下,仿真器將其內(nèi)部時(shí)鐘與外部時(shí)鐘同步。

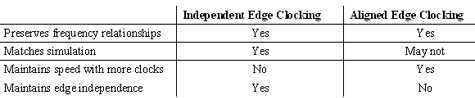

為了提供盡可能高的仿真速度,同時(shí)保持所需的異步精度,一些基于處理器的仿真器提供了兩種處理異步設(shè)計(jì)時(shí)鐘的方法:對(duì)齊邊和獨(dú)立邊緣。

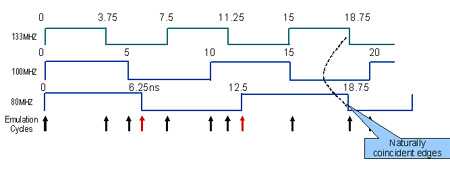

圖6 ??時(shí)鐘示例??三個(gè)異步時(shí)鐘

獨(dú)立邊沿時(shí)鐘

由于仿真器不對(duì)設(shè)計(jì)時(shí)序進(jìn)行建模,而是功能等效,因此異步時(shí)鐘邊沿之間的精確時(shí)序無(wú)關(guān)緊要。只需要在“現(xiàn)實(shí)生活”中不同時(shí)的時(shí)鐘邊緣是獨(dú)立模擬的。

通過(guò)獨(dú)立的邊沿時(shí)鐘,基于處理器的仿真器為每個(gè)時(shí)鐘的每個(gè)邊沿調(diào)度仿真周期,除非邊緣與已經(jīng)調(diào)度的邊緣自然共同發(fā)生。這與事件驅(qū)動(dòng)的模擬器非常相似。

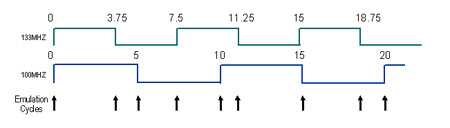

圖7 ???jī)蓚€(gè)異步時(shí)鐘的獨(dú)立邊沿時(shí)鐘

從兩個(gè)時(shí)鐘開(kāi)始,133 MHz時(shí)鐘從0到7.5,15.0等的高電平有時(shí)(以ns為單位)從高電平轉(zhuǎn)換為高電平。在時(shí)間為5,15,25等時(shí),100MHz時(shí)鐘從低到高從低到高轉(zhuǎn)換為高,低為5,15,25等。注意兩者是任意同步的在時(shí)間= 0.

仿真周期#1:133 MHz時(shí)鐘上升,100 MHz時(shí)鐘上升(兩者同時(shí)發(fā)生)。

仿真周期#2:133 MHz下降(時(shí)間= 3.75)。 100 MHz無(wú)效。

仿真周期#3:100 MHz下降(時(shí)間= 5.00)。 133 MHz無(wú)效。

仿真周期#4:133 MHz上升(時(shí)間= 7.5)。 100 MHz無(wú)效。

仿真周期#5:10 MHz上升(時(shí)間= 10)。 133 MHz無(wú)效。

仿真周期#6:133 MHz下降(時(shí)間= 11.25)。 100 MHz無(wú)效。

仿真周期#7:133 MHz上升,100 MHz下降(時(shí)間= 15ns ???jī)纱无D(zhuǎn)換)

圖8 ??添加具有獨(dú)立邊沿時(shí)鐘的第三個(gè)異步時(shí)鐘

所以時(shí)間表如下:仿真周期#1:133 MHz時(shí)鐘上升,100 MHz和80 MHz時(shí)鐘上升(同時(shí)發(fā)生) 。仿真周期#2:133 MHz下降(時(shí)間= 3.75)80 MHz,100 MHz什么都不做。

仿真周期#3:100 MHz下降(時(shí)間= 5.00)80 MHz,133 MHz什么也不做。

仿真周期#4:80 MHz下降(時(shí)間= 6.25)100 MHz,133 MHz什么也不做。

仿真周期#5:133 MHz上升(時(shí)間= 7.5)80 MHz,100 MHz什么都不做。

仿真周期#6:100 MHz上升。 (時(shí)間= 10)80 MHz,100 MHz不執(zhí)行任何操作。

仿真周期#7:133 MHz下降。 (時(shí)間= 11.25)80 MHz,100 MHz無(wú)效。

仿真周期#8:80 MHz上升。 (時(shí)間= 12.5)100 MHz,133 MHz什么都不做。

仿真周期#9:133 MHz上升,100 MHz下降(時(shí)間= 15ns ???jī)纱无D(zhuǎn)換)。

對(duì)齊邊沿時(shí)鐘

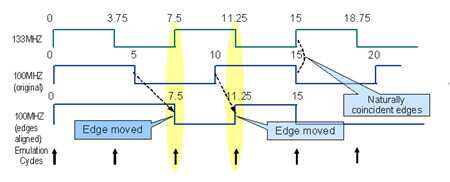

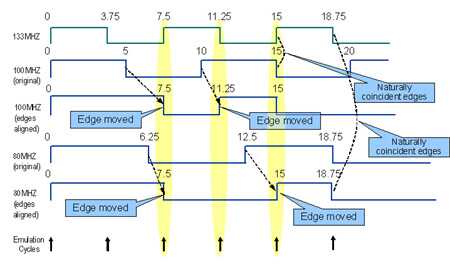

對(duì)齊邊沿時(shí)鐘基于以下事實(shí):盡管設(shè)計(jì)中的許多時(shí)鐘由于其頻率而碰巧具有非重合邊緣,但正確的電路操作并不依賴(lài)于邊緣是獨(dú)立的。在這種情況下,在保持適當(dāng)?shù)念l率關(guān)系的同時(shí),時(shí)鐘邊沿與最高頻率時(shí)鐘對(duì)齊,從而減少了所需的仿真周期數(shù),并提高了仿真速度。

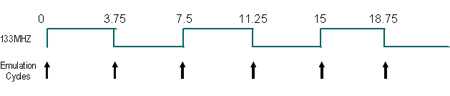

在對(duì)齊的邊沿時(shí)鐘中,我們首先為設(shè)計(jì)中最快時(shí)鐘的每個(gè)邊沿調(diào)度仿真周期。

圖9 ??通過(guò)為最快時(shí)鐘的每個(gè)邊沿分配仿真周期開(kāi)始對(duì)齊邊沿時(shí)鐘

然后,所有其他時(shí)鐘相對(duì)于此時(shí)鐘進(jìn)行調(diào)度,較慢的時(shí)鐘邊沿與下一個(gè)預(yù)定仿真“對(duì)齊”周期。請(qǐng)注意,第二個(gè)(較慢)時(shí)鐘沒(méi)有添加額外的仿真周期。因此保持了仿真速度。另請(qǐng)注意,雖然邊沿移動(dòng)到跟隨最快的時(shí)鐘邊沿,但仍保持頻率關(guān)系,這對(duì)于正確的電路操作是必不可少的。

圖10 ??添加第二個(gè)時(shí)鐘對(duì)齊邊緣到最快時(shí)鐘

圖11 ??通過(guò)將邊緣與最快時(shí)鐘對(duì)齊來(lái)添加其他時(shí)鐘

對(duì)齊邊緣時(shí)鐘中的過(guò)采樣和欠采樣

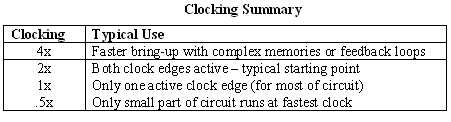

當(dāng)在最快設(shè)計(jì)時(shí)鐘的兩個(gè)邊沿存在仿真周期時(shí),它被稱(chēng)為“2x”時(shí)鐘(每個(gè)最快時(shí)鐘周期兩個(gè)仿真周期)。

1x時(shí)鐘

有時(shí)在設(shè)計(jì)中只有最快設(shè)計(jì)時(shí)鐘的一個(gè)邊沿有效,或者一個(gè)邊緣占主導(dǎo)地位,而另一個(gè)邊沿占用最少量的電路。在這種稱(chēng)為“1x時(shí)鐘”的情況下,每個(gè)設(shè)計(jì)時(shí)鐘周期的單個(gè)仿真周期加倍?還是差不多?仿真速度。所需容量可能略有增加。

如果一個(gè)邊緣不占優(yōu)勢(shì),那么仍然可以應(yīng)用這種技術(shù),但所需容量的增加將會(huì)顯著增加。請(qǐng)注意,只有使用最快時(shí)鐘的電路和任何大于最快時(shí)鐘速度一半的時(shí)鐘才能滿(mǎn)足所需容量的增加。

4x時(shí)鐘?過(guò)采樣

這可以快速啟動(dòng)包含復(fù)雜異步路徑的設(shè)計(jì)。具有讀 - 修改 - 寫(xiě)存儲(chǔ)器或背靠背鎖存器的設(shè)計(jì)可以通過(guò)最初使用4x時(shí)鐘更快地進(jìn)行仿真。

有時(shí)稱(chēng)為“過(guò)采樣”,4x時(shí)鐘為每個(gè)活動(dòng)時(shí)鐘邊沿提供兩個(gè)仿真周期(或更多)。當(dāng)存在復(fù)雜的異步反饋循環(huán)時(shí),這也會(huì)有所幫助。基于鎖存器的設(shè)計(jì)可能需要過(guò)采樣,因?yàn)榫幾g器必須在鎖存器的兩個(gè)級(jí)別之間插入延遲。如果存在復(fù)雜的反饋路徑,則可能無(wú)法始終將此延遲放在最佳位置。

.5x時(shí)鐘

這種技術(shù)可在某些基于處理器的仿真器上使用,主要用于在最快的設(shè)計(jì)時(shí)鐘運(yùn)行少量邏輯時(shí)。在.5x時(shí)鐘中,兩個(gè)最快的設(shè)計(jì)時(shí)鐘在一個(gè)仿真周期中進(jìn)行仿真。這可以進(jìn)一步提高仿真速度超過(guò)1倍時(shí)鐘,但有一定的限制:只有最快設(shè)計(jì)時(shí)鐘的一個(gè)邊沿可能有效,此時(shí)鐘不能有復(fù)雜的時(shí)鐘門(mén)控,并且不能有太多的設(shè)計(jì)邏輯以此速度運(yùn)行,因?yàn)樗梢燥@著增加模擬設(shè)計(jì)所需的容量。

使用戶(hù)可以靈活地在對(duì)齊邊緣時(shí)鐘或獨(dú)立邊緣之間切換時(shí)鐘為各種設(shè)計(jì)風(fēng)格提供高異步精度和最快的仿真速度。

基于處理器的仿真器中的內(nèi)存建模

編譯器將識(shí)別用可綜合的Verilog和VHDL RTL代碼編寫(xiě)的大多數(shù)內(nèi)存并自動(dòng)處理它們,包括:

多個(gè)讀寫(xiě)端口

端口共享最小化面積/延遲

改變讀/寫(xiě)依賴(lài)性

不同的寫(xiě)使能(邊緣與電平靈敏度)

同步和異步樣式

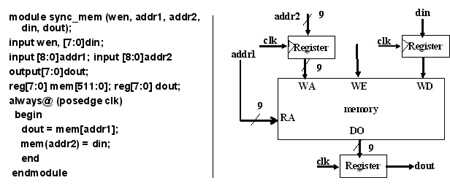

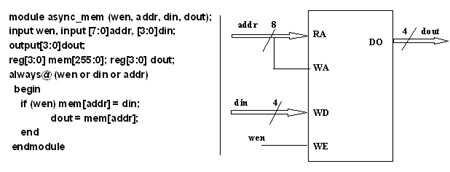

從用戶(hù)的Verilog代碼自動(dòng)建模的兩個(gè)存儲(chǔ)器示例如下。

圖12 ??示例:具有邊沿敏感時(shí)鐘的同步存儲(chǔ)器是從用戶(hù)的Verilog代碼自動(dòng)生成的

圖13 ??示例:具有電平敏感寫(xiě)入啟用的異步存儲(chǔ)器是從用戶(hù)的Verilog代碼自動(dòng)生成的。

如果必須手動(dòng)構(gòu)建異常存儲(chǔ)器,用戶(hù)將在仿真器的原始存儲(chǔ)器單元周?chē)鷮?xiě)一個(gè)“包裝器”以提供必要的回應(yīng)。

在線(xiàn)仿真接口

輸出時(shí)序控制

當(dāng)與現(xiàn)實(shí)世界接口時(shí)有時(shí)需要控制輸出信號(hào)的相對(duì)定時(shí)。 DRAM存儲(chǔ)器接口就是這樣一個(gè)例子??在斷言寫(xiě)入使能之前,所有地址線(xiàn)必須穩(wěn)定。

由于基于處理器的仿真器調(diào)度邏輯操作按順序發(fā)生,因此很容易在仿真周期內(nèi)對(duì)各個(gè)(或組)輸出信號(hào)添加約束,以控制定時(shí)到非常相對(duì)于其他輸出信號(hào)的高分辨率。然后,編譯器在仿真周期的適當(dāng)位置調(diào)度此輸出計(jì)算。基于FPGA的仿真器無(wú)法實(shí)現(xiàn)這一點(diǎn),因?yàn)樗鼈儫o(wú)法控制設(shè)計(jì)時(shí)鐘內(nèi)的時(shí)序。

圖14 ??基于處理器的仿真器可以高精度調(diào)整輸出時(shí)序

輸入時(shí)序控制

以類(lèi)似的方式?并出于類(lèi)似的原因??輸入信號(hào)上的定時(shí)(“采樣”)可由用戶(hù)控制以滿(mǎn)足特定情況。同樣,基于處理器的仿真器可以簡(jiǎn)單地調(diào)度特定輸入引腳,以便在仿真周期內(nèi)的其他引腳之前或之后進(jìn)行采樣。使用基于FPGA的仿真器,用戶(hù)必須通過(guò)增加某些信號(hào)的延遲來(lái)“調(diào)整”時(shí)序,包括一個(gè)大的保護(hù)頻帶,因?yàn)榛贔PGA的仿真器無(wú)法控制不同邏輯路徑上的絕對(duì)時(shí)序。對(duì)于基于FPGA的仿真器,這是一個(gè)命中注定的命題,可能因編譯而異。

摘要結(jié)果

硬件加速器和仿真器提供比邏輯仿真器更高的驗(yàn)證性能,但需要額外的部署工作。在線(xiàn)仿真提供了最高的性能,通常比模擬器快10,000到100,000倍,但需要使用速度緩沖設(shè)備圍繞它構(gòu)建仿真環(huán)境。加速器和仿真器要求用戶(hù)了解仿真和硅(仿真器和芯片)之間的差異:

仿真有12個(gè)或更多狀態(tài),硅只有兩個(gè)狀態(tài)。

模擬通常按順序執(zhí)行RTL語(yǔ)句,硅同時(shí)“執(zhí)行”RTL。

模擬是高度交互的,硅不那么。

基于FPGA的仿真器使用商用FPGA,體積更小,功耗更低,而基于處理器的仿真器需要定制芯片設(shè)計(jì)并消耗更多功率。另一方面,基于處理器的仿真器在十分之一的工作站上編譯設(shè)計(jì)速度快十倍?分鐘與小時(shí)。幾乎所有設(shè)計(jì)的仿真速度都更快,平均速度提高了2倍。

兩種仿真器都證明了它們?cè)谠O(shè)計(jì)中同樣能夠處理大量異步時(shí)鐘而不會(huì)對(duì)性能產(chǎn)生影響。基于處理器的仿真器能夠立即探測(cè)新信號(hào)并改變觸發(fā)條件而無(wú)需緩慢的FPGA編譯,這極大地提高了調(diào)試的交互性。由于用戶(hù)大部分時(shí)間都在調(diào)試,因此基于處理器的仿真器每天可以提供比基于FPGA的仿真器更多的設(shè)計(jì)周轉(zhuǎn)時(shí)間。這樣可以縮短新產(chǎn)品的上市時(shí)間并提高產(chǎn)品質(zhì)量。

Ray Turner是Cadence的Incisive Palladium加速器和在線(xiàn)仿真系統(tǒng)的高級(jí)產(chǎn)品線(xiàn)經(jīng)理,該系統(tǒng)是Incisive功能驗(yàn)證平臺(tái)的一部分。在加入Cadence之前,他曾擔(dān)任P CAD產(chǎn)品的EDA營(yíng)銷(xiāo)經(jīng)理7年。總體而言,Ray在EDA產(chǎn)品的產(chǎn)品管理方面擁有18年的經(jīng)驗(yàn)。他還在電信,航空航天,ATE和微處理器行業(yè)擁有14年的硬件,軟件和IC設(shè)計(jì)經(jīng)驗(yàn)。

-

處理器

+關(guān)注

關(guān)注

68文章

19409瀏覽量

231189 -

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606023 -

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83937

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于FPGA的仿真如何工作

基于FPGA的仿真如何工作

評(píng)論