在實際的設(shè)計中,板層特性(如厚度,介質(zhì)常數(shù)等)以及線長、線寬、線距、信號的上升時間等都會對串?dāng)_有所影響。

下面結(jié)合使用Mentor Graphie公司的信號完整性仿真軟件Hyperlynx,對上述的影響串?dāng)_的因素進(jìn)行分析。

首先在Hyperlynx中建立兩線串?dāng)_的模型,如圖4所示,設(shè)兩線的線寬為5 mil,線長為6 in,線距為5 mil,兩線均為頂層微帶線,特性阻抗為49.5Ω,兩線都端接50Ω的電阻,以消除反射的影響。

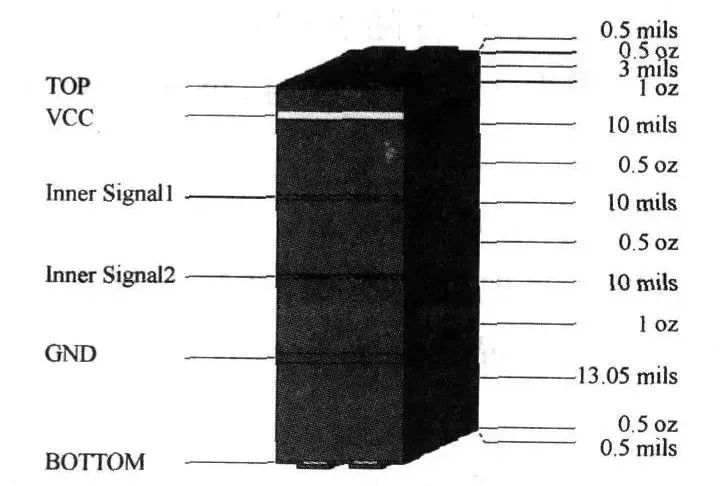

干擾線的驅(qū)動器采用CMOS工藝器件的IBIS模型,電壓為3.3 V,頻率為100 MHz。PCB的介電常數(shù)為4.3,六層板,其疊層結(jié)構(gòu)如圖5所示。

圖4:兩線串?dāng)_模型

圖5:PCB疊層結(jié)構(gòu)

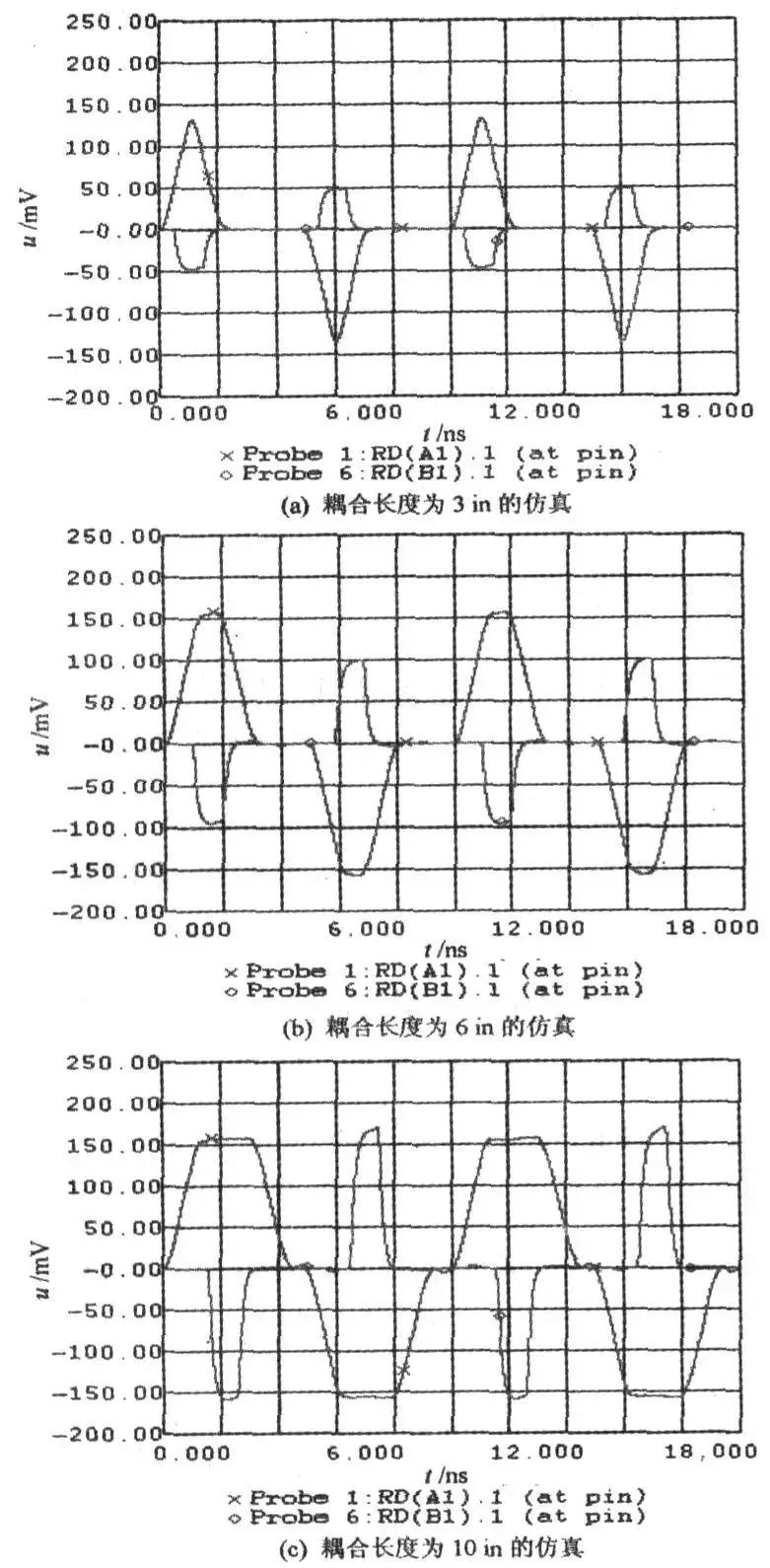

1耦合長度對串?dāng)_的影響

改變兩線的耦合長度,分別將耦合長度設(shè)置為3 in,6 in,10 in,其他設(shè)置不變。

圖6(a)是耦合長度為3 in的串?dāng)_波形,其中近端串?dāng)_峰值為126.34 mV,遠(yuǎn)端為43.01 mV;圖6(b)是耦合長度為6 in的串?dāng)_波形,其近端串?dāng)_峰值為153.23 mV,遠(yuǎn)端為99.46 mV;圖6(c)是耦合長度為10 in的串?dāng)_波形,其近端串?dāng)_峰值為153.23 mV,遠(yuǎn)端為163.98 mV。

由此可見,對于遠(yuǎn)端串?dāng)_峰值與耦合長度成正比,耦合長度越長,串?dāng)_越大;而對于近端串?dāng)_,當(dāng)耦合長度小于飽和長度時,串?dāng)_將隨著耦合長度的增加而增加,但是當(dāng)耦合長度大于飽和長度時,近端串?dāng)_值將為一個穩(wěn)定值。

圖6:不同耦合長度的仿真結(jié)果

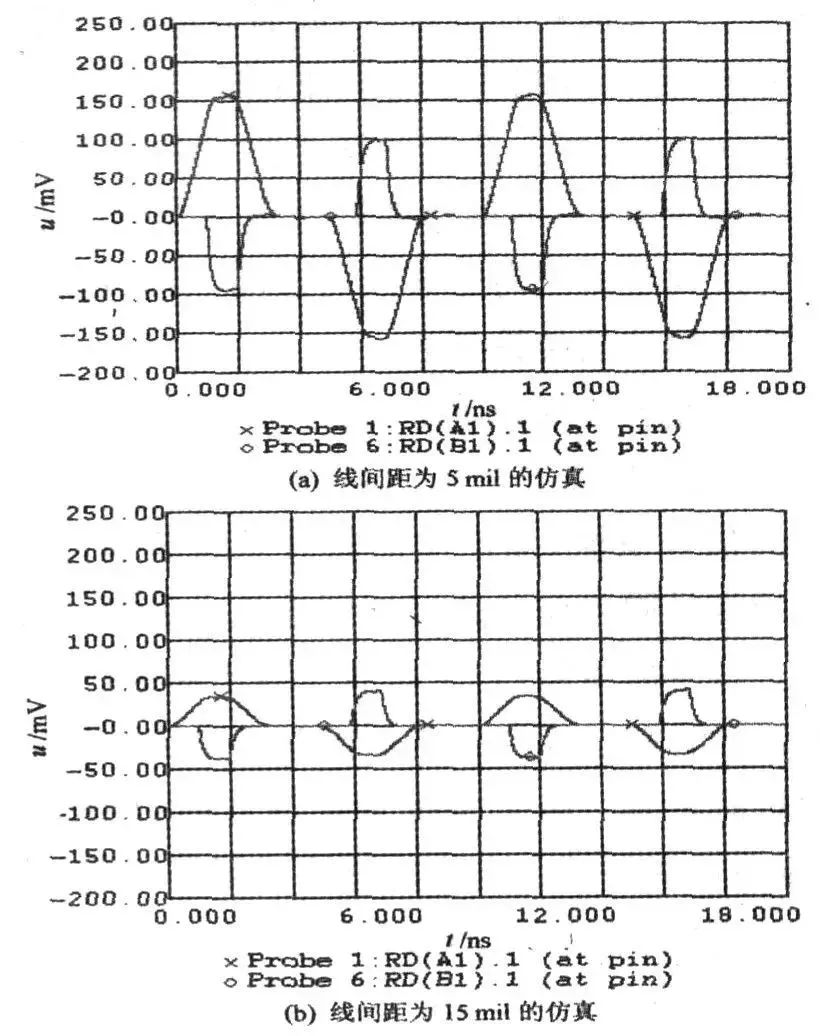

2線間距對串?dāng)_的影響

以下是保持其他設(shè)置不變,考察線間距的改變對串?dāng)_的影響。分別設(shè)置線距為5 mil,15 mil,仿真波形如圖7所示。

圖7:不同線間距的仿真結(jié)果

由圖7可知,當(dāng)線間距為5 mil時,近段串?dāng)_峰值為153.23 mV,遠(yuǎn)端為99.46 mV;而線間距為15 mil時,近端串?dāng)_峰值為33.40 mV,遠(yuǎn)端為40.49 mV。

可見隨著線間距的增大,無論是近端還是遠(yuǎn)端串?dāng)_都將減小,當(dāng)線間距大于等于線寬的3倍時,串?dāng)_已經(jīng)很小。

3上升時間對串?dāng)_的影響

下面考察上升沿時間的變化對串?dāng)_的影響,其他設(shè)置保持不變。分別設(shè)置驅(qū)動器為CMOS 3.3 V MEDI—UM;CMOS 3.3 V FAST;CMOS 3.3 V ULTRA—FAST,仿真波形如圖8所示。

圖8:不同驅(qū)動器設(shè)置的仿真結(jié)果

圖8(a)中的近端串?dāng)_峰值為153.9 mV,遠(yuǎn)端串?dāng)_為46.3 mV;圖8(b)中近端串?dāng)_峰值為153.2 mV,遠(yuǎn)端串?dāng)_為99.5 mV;圖8(c)中近段串?dāng)_峰值為153.2 mV,遠(yuǎn)端串?dāng)_為349.9 mV。

可見,當(dāng)上升沿時間縮短時,遠(yuǎn)端串?dāng)_噪聲越來越大。

對于近端串?dāng)_來說,如果與傳輸線的時延相比,上升時間較短,則近端串?dāng)_與上升時間無關(guān);而如果與傳輸線時遲相比,上升時間較長,則近端串?dāng)_噪聲與上升時間有關(guān)(隨著上升沿時間的減小,近端串?dāng)_變大)。

4介質(zhì)層厚度對串?dāng)_的影響

在PCB的疊層編輯器中將介質(zhì)層厚度分別設(shè)置為3 mil和6 mil,其他設(shè)置不變,仿真波形如圖9所示。

圖9:不同介質(zhì)層厚度的仿真結(jié)果

考察以上的仿真波形可知,當(dāng)介質(zhì)層厚度為3 mil時,近端串?dāng)_峰值為153.2 mV,遠(yuǎn)端串?dāng)_為99.5 mV;當(dāng)介質(zhì)層厚度為6 mil時,近端串?dāng)_峰值為277.3 mV,遠(yuǎn)端串?dāng)_為163.9 mV。

可見,隨著介質(zhì)層厚度的減小,串?dāng)_也將變小。

-

串?dāng)_

+關(guān)注

關(guān)注

4文章

189瀏覽量

26992 -

仿真分析

+關(guān)注

關(guān)注

3文章

105瀏覽量

33698

原文標(biāo)題:龍泉寺,一夜之間被刷屏的神秘組織!

文章出處:【微信號:Interflow-Platform,微信公眾號:WPR】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ADC電路的串擾怎么解決?

使用TMUX1109做ADC差分同步采樣,出現(xiàn)了很嚴(yán)重的串擾怎么解決?

DAC61416通道間出現(xiàn)串擾的原因?怎么解決?

博眼球還是真本事?參考平面不完整信號串擾反而好

博眼球還是真本事?參考平面不完整信號串擾反而好

高頻電路設(shè)計中的串擾問題

信號的串擾介紹

多通道數(shù)據(jù)采集串擾問題怎么解決

放大器的串擾問題

嵌入式開發(fā)中引起串擾的原因是什么?

車載網(wǎng)絡(luò)協(xié)議與串擾問題

串?dāng)_的仿真分析

串?dāng)_的仿真分析

評論