由于多種因素的綜合作用,電源噪聲和相關問題已成為90nm及以下設計的關鍵。由于電網噪聲,定時減速和功能故障在這些設計中變得普遍。然而,物理設計和驗證方法尚未充分發展以充分解決這些電源噪聲問題。

芯片電源的規劃,資源分配和設計(包括封裝,去耦電容和電網網絡)必須以整體方式進行,并進行簽核質量驗證和分析。設計人員需要降低設計中動態壓降(DvD)的技術及其對時序和功能的影響,他們需要采用功耗感知物理設計方法。

動態電網噪聲

電源噪聲具有以下組成部分:電阻網絡壓降,電容耦合電網噪聲和電感元件誘發噪音。技術和設計趨勢加劇了電源噪聲水平及其對性能的影響。

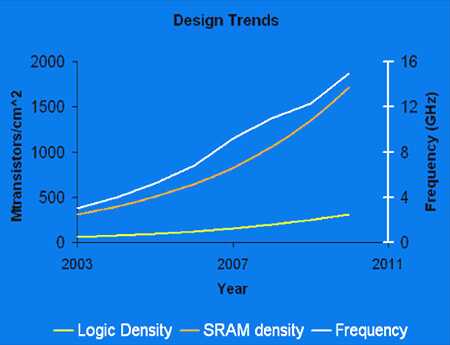

圖1顯示了基于ITRS數據的平均電流和di/dt值預測[1]。該趨勢表明,在先進技術節點中,同時切換設備的動態電壓降將變得更糟。不僅更高的di/dt會導致更大的動態壓降,而且導線中更高的開關電流也會導致更大的電阻壓降。

圖1 - 電流消耗趨勢

如圖2所示,更高的單元放置密度,更短的邊沿速率和更快的時鐘周期將導致更多的單元在時間上和空間上更緊密地切換,從而提高對瞬時電流的需求。針對封裝設計,片上電網尺寸調整和去耦電容分配的現有方法和設計實踐將不足以創建能夠響應更大和更頻繁的片上電流尖峰的電源系統,這將在下一代中看到設計。

圖2 - 設計趨勢

隨著設計從130nm技術節點遷移,設計人員正在超越傳統靜態電壓降分析采用全芯片動態仿真方法,該方法考慮了同步開關電流與設計中存在的電感和電容元件的相互作用。一種早期的動態分析形式包括將模擬周期劃分為幾個區間,并在每個區間內進行靜態分析。

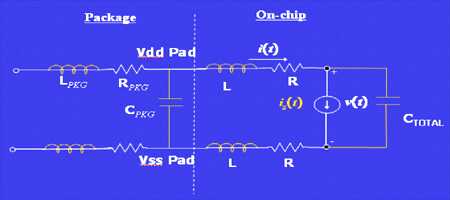

今天,這種方法已被高度精確的全芯片瞬態仿真解決方案所取代。提供設計中動態電壓曲線的完整畫面。該仿真技術考慮了芯片封裝和片上網格中的電阻,電感和電容元件,同時切換輸出所消耗的動態電流以及設計中存在的容性負載。圖3說明了該解決方案中建模的仿真框架。

圖3 - 動態仿真模型

影響動態電源噪聲

靜態定時工具不能解決DvD對松弛和轉換的影響,這通常遠大于靜態壓降預算。在存在電網噪聲的情況下,電池的傳播延遲增加。

此外,高級流程中的大門更有可能受到DvD的影響。高柵極延遲靈敏度和增加的電網噪聲的組合導致芯片中的頻率減慢,否則通過靜態時序分析。許多設計,特別是那些90nm節點的設計,都出現了動態電壓降相關問題的失敗。

時鐘網絡上的時序影響會更大,因為緩沖區通常彼此靠近并且切換一起。電網噪聲的可變性轉化為增加的偏斜,導致保持時間要求失敗。定時和時鐘偏移分析必須考慮關鍵路徑中實例或時鐘網絡中緩沖器所見的動態電壓降。

電網噪聲也會影響a的串擾抗擾度。設計。當電池同時經歷電壓降和/或接地反彈時,電池更可能從耦合噪聲中失效。細胞的譜庫表征通常不能解釋瞬態電壓降及其對細胞性能的影響。因此,功能可能會受到影響,尤其是在一段時間內持續保持動態電壓降時。

固定電網噪聲

設計人員必須估算和補償電網噪聲,以確保其電路正常運行并防止前面提到的電源發生故障。傳統技術是過度設計電源網絡并用去耦電容器填充所有可用區域。對于具有更高噪聲容限和更大設計保護頻帶的上一代設計,這種方法已經相當不錯。

然而,通過先進的流程,設計師不再擁有填充設計目標和增加豐厚利潤的奢侈品。更嚴格的設計規范(包括更低的電源電壓和更快的時鐘頻率)留下的誤差空間更小。在投入生產之前,關鍵設計的上市時間只能提供非常少的流片迭代。

低成本設計受到過度設計的電網和更多硅資源使用的嚴重影響。需要多個調試和流片周期來識別和修復與電網相關的芯片故障。由于缺乏可用的路由空間,電網的過度設計也會影響項目進度,因為路由和時序收斂變得更加困難。

電網設計傳統上基于啟發式或經驗。電力網絡在整個設計中的寬度和間距通常是均勻的。設計完成后,電源路由保持不變,除非在流片輸出之前執行的壓降驗證表明存在問題區域。這種方法的問題是:

網格未針對特定設計及其功耗進行優化。

網格均勻設計過度或設計不足。

電網問題僅在設計周期的后期解決。

故意去耦電容( decap)放置也是臨時的,無助于抑制電網噪聲。這些開蓋單元通常放置在空單元行中,其中沒有足夠的切換使它們有效。此外,通過消耗更多的漏電流,不加選擇的去耦位置會對設計產生不利影響,這是一個問題,因為90nm設計中芯片總功率的約30%將來自漏電流。

功率感知物理設計

電源感知物理設計需要改變當前的設計實踐。初始電網的設計應符合某些規范。應該使用原型解決方案來快速生成針對各種用戶定義約束的多個電網設計,例如不同的布局規劃或功耗方案,以估計路由資源需求。

在設計過程的早期階段,應該優化選定的原型網格,同時仍然可以靈活地更改電源路徑。應使用簽核質量的電網分析解決方案來驗證優化的質量。

在設計的后期階段,當更多地定義放置時,應該對電網執行目標修復以解決電壓降問題。去耦電容建議應該是自動的,以解決動態熱點問題,并使設計人員能夠有針對性地進行去耦,優化動態電壓降,同時最大限度地減少對去耦泄漏電流的影響。

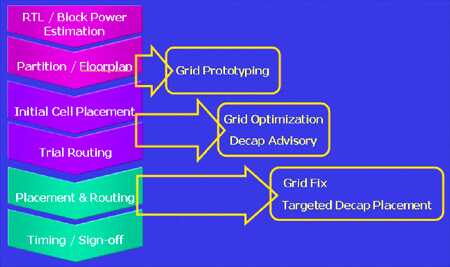

圖4顯示了功率感知物理設計流程,為初始P/G路由定義提供原型解決方案,允許沿設計周期優化P/G網格,修復P/G網格問題,建議十進制要求,并以有針對性的方式進行減速。

圖4 - 功率感知物理設計流程

網格原型設計

網格原型設計應允許設計人員針對各種設計方案探索不同的電網設計選項。高效,快速,準確的電網原型設計解決方案將使設計人員能夠嘗試不同的布局規劃選項,多種功耗場景和多種布線預算。原型設計解決方案應該足夠靈活,可以在設計的最初階段工作,當最小的布局信息可用時,或者在設計的稍微更確定的階段,當早期布局信息和定義全球和本地電網的范圍是可用。

網格原型設計應受約束驅動,以滿足用戶定義的動態和靜態電壓降目標,同時滿足特定的路由資源使用限制。由原型解決方案生成的多層電網應該遵循阻塞和電遷移限制,探索焊盤放置選項,并在需要時生成環。

它應該為用戶提供探索非均勻網格選項的能力,其中高功率區域獲得更高的電網資源份額。原型設計解決方案還應具有快速周轉時間,以實現多次迭代。

圖5顯示了設計團隊如何針對不同的布局規劃和功耗場景探索不同的電網結構。通過執行此練習,設計團隊可以獲得每個方案所需的P/G網格路由資源的工程估計。然后,他們可以選擇最適合其最可能的設計方案的電網。這個選定的電網將是最佳的,以滿足其功率和路由目標。

圖5 - 電網結構探索

電網優化和修復

隨著設計的發展,應優化原型網格以反映設計變化。為了滿足設計的電壓降目標,優化解決方案應根據用戶提供的限制(如節距和軌道要求)重新定義電網。這種方法可以讓設計人員通過精煉電網的自動化流程來滿足其降壓預算。對于給定的壓降預算,優化解決方案將調整導線的尺寸以最小化P/G網格的金屬布線使用。設計人員不是首先設計網格然后獲得電壓降數,而是首先確定下降預算并設計一個符合該預算的網格。

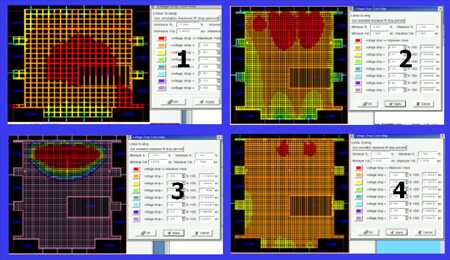

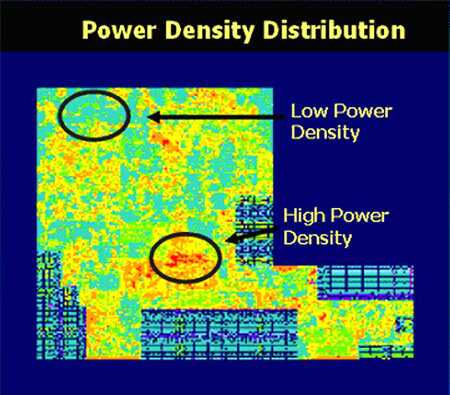

設計中的功耗,尤其是功率密度,通常非常不均勻,如圖6所示。功率密度“熱點”通常出現在插入時鐘緩沖器的區域。

圖6 - 功率密度圖

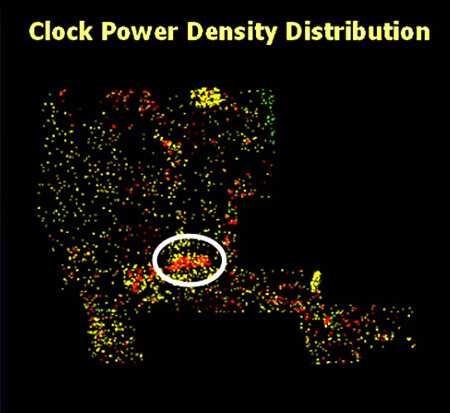

時鐘實例功率圖,如圖8所示,顯示了與圖7中的功率密度圖。電網優化解決方案應該將更多的金屬資源分配給可能具有比具有稀疏單元布局的區域更高的電壓降的區域。對于采用有線封裝設計的電源和分布問題更加局部化的倒裝芯片設計,情況尤其如此。

圖7 - 時鐘功率密度

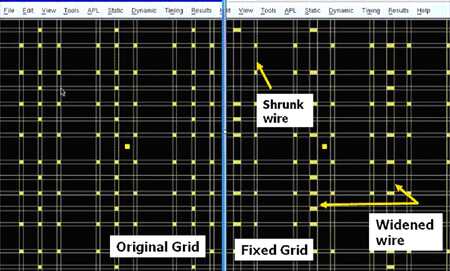

一旦完成詳細布局并且正在進行時序優化,電力和地面網絡的全局優化就不再可行。在這種情況下,需要對電網進行有針對性的修復以解決電壓降“熱點”。電網應僅在熱點區域加寬,在其他區域縮小,不會影響總電壓降。

解決方案應提供快速周轉時間,以解決可能導致的P/G問題來自設計迭代。用戶應該只能修復他們設計中的特定區域,限制對某些金屬層的修復,并定義修復的方式。

圖8說明了設計的電網如何運行自動修復解決方案后更改。左側面板顯示原始的均勻網格,而右側面板顯示固定網格,其中一些導線已經加寬而其他導線已經縮小。

圖8 - 非均勻的線柵固定

開蓋建議和修理

Decaps作為當地的充電水庫,它們的位置應該是以有針對性的方式完成,以將功率和地面噪聲降低到可接受的限度。然而,特殊的decap接頭增加了不必要的漏電流,同時降低了動態電壓降。沿著電源線和地線的電阻降的增加需要將decap放置在更靠近開關區域的位置。

設計師應該被引導到最有效的開蓋位置的位置,并且它們應該能夠自動重新定義細胞并去除放置位置以減少DvD。高壓降區域不一定必須重新設計,除非它影響通過該區域的路徑的時序或影響該區域中的單元的功能。因此,固定解決方案應該基于精確的動態功耗分析,并提供反饋到時序分析,并應確定需要使用開蓋放置或線尺寸調整來固定的區域。

開蓋放置解決方案應該在咨詢模式,向設計者提供關于需要減速的地方的反饋,以及通過在合法化的放置區域中放置decap來修復模式。它應滿足用戶指定的目標,同時遵守總泄漏電流和放置限制等約束。

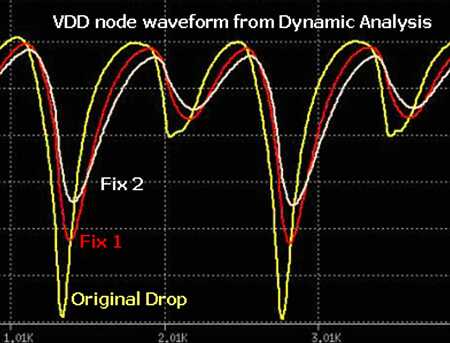

它應該提供根據用戶的規范通過使用電線更改或decap放置或兩者來解決問題的選項。圖9示出了在具有用于降低動態電壓噪聲的不同目標的兩個不同的去耦固定運行之后的實例的電源節點處的電壓噪聲。

圖9 - 對Vdd噪聲進行消隱固定結果

結論

縮短產品生命周期加快了新設計的推出速度。首先進入市場會顯著影響產品在這種環境中取得成功的機會。

掩模組的高價格以及與頻繁設計變更相關的成本要求設計團隊預測并解決設計失敗的原因。他們必須超越傳統的電網設計和分析技術來估計和減少P/G噪聲對設計時序和功能的影響。

在許多失敗的90nm設計中,電網噪聲最常被認為是失效源。其他設計團隊發現P/G噪音更明顯地表現在產量損失等問題上。下一代芯片需要采用整體的電源設計方法來解決這些問題,其中過度設計和保護帶不再是可行的選擇。

本文概述了功率感知物理設計該方法允許工程師設計芯片電源,以幫助減輕P/G噪聲引起的設計故障并避免后期設計變更。它突出顯示了使用商用解決方案生成的數據,該解決方案集成了動態電網噪聲的電網原型設計,優化,修復和驗證,可實現更快,更有效的設計收斂。

-

電源

+關注

關注

184文章

17839瀏覽量

251797 -

電網

+關注

關注

13文章

2112瀏覽量

59364

發布評論請先 登錄

相關推薦

可解決動態電網噪聲的電網原型設計方案

可解決動態電網噪聲的電網原型設計方案

評論