摘要:為了提高PCB 測試機(jī)的測試速度,簡化電路板的設(shè)計(jì),提高系統(tǒng)的可重構(gòu)性和測試算法移植的方便性,提出了一種基于FPGA的PCB測試機(jī)的硬件控制系統(tǒng)設(shè)計(jì)方案。 設(shè)計(jì)中選用Altera公司的現(xiàn)場可編程門陣列(FPGA)EP1K50,利用EDA設(shè)計(jì)工具Synplify、Modelsim、QuartusⅡ以及Verilog硬件描述語言,完成了控制系統(tǒng)的硬件設(shè)計(jì)及調(diào)試,解決了由常規(guī)電路難以實(shí)現(xiàn)的問題。

關(guān)鍵詞:PCB 測試;可重構(gòu)FPGA ;PC104 總線;Verilog

引言

PCB 光板測試機(jī)基本的測試原理是歐姆定律,其測試方法是將待測試點(diǎn)間加一定的測試電壓,用譯碼電路選中PCB 板上待測試的兩點(diǎn),獲得兩點(diǎn)間電阻值對應(yīng)的電壓信號,通過電壓比較電路,測試出兩點(diǎn)間的電阻或通斷情況。 重復(fù)以上步驟多次,即可實(shí)現(xiàn)對整個(gè)電路板的測試。

由于被測試的點(diǎn)數(shù)比較多, 一般測試機(jī)都在2048點(diǎn)以上,測試控制電路比較復(fù)雜,測試點(diǎn)的查找方法以及切換方法直接影響測試機(jī)的測試速度,本文研究了基于FPGA的硬件控制系統(tǒng)設(shè)計(jì)。

硬件控制系統(tǒng)

測試過程是在上位計(jì)算機(jī)的控制下,控制測試電路分別打開不同的測試開關(guān)。測試機(jī)系統(tǒng)由以下幾部分構(gòu)成: 上位計(jì)算機(jī)PC104 、測試控制邏輯(由FPGA 實(shí)現(xiàn)) 、高壓測試電路。 其中上位機(jī)主要完成人機(jī)交互、測試算法、測試數(shù)據(jù)處理以及控制輸出等功能。 FPGA 控制高壓測試電路完成對PCB 的測試過程。

本系統(tǒng)以一臺PC104 為上位計(jì)算機(jī),以FPGA為核心,通過PC104 總線實(shí)現(xiàn)上位機(jī)對測試的控制。

FPGA與PC104的接口電路

PC104總線是一種專為嵌入式控制定義的工業(yè)控制總線,其信號定義與ISA 總線基本相同。 PC104總線共有4 類總線周期,即8 位的總線周期、16 位的總線周期、DMA 總線周期和刷新總線周期。 16 位的I/O總線周期為3 個(gè)時(shí)鐘周期,8 位的I/O總線周期為6 個(gè)時(shí)鐘周期。 為了提高通信的速度,ISA總線采用16 位通信方式,即16 位I/O方式。 為了充分利用PC104的資源,應(yīng)用PC104的系統(tǒng)總線擴(kuò)展后對FPGA 進(jìn)行在線配置。正常工作時(shí)通過PC104總線與FPGA進(jìn)行數(shù)據(jù)通信。

FPGA與串行A/D及D/A器件的接口

根據(jù)測試機(jī)系統(tǒng)設(shè)計(jì)要求,需要對測試電壓及兩通道參考電壓進(jìn)行自檢,即A/D轉(zhuǎn)換通道至少有3 路。 兩路比較電路的參考電壓由D/A輸出,則系統(tǒng)的D/A通道要求有兩通道。 為了減少A/D及D/A的控制信號線數(shù),選用串行A/D及D/A器件。 綜合性能、價(jià)格等因素, 選用的A/D器件為TLC2543,D/A器件為TLV5618。

TLV5618是TI公司帶緩沖基準(zhǔn)輸入(高阻抗)的雙路12 位電壓輸出DAC,通過CMOS 兼容的3線串行總線實(shí)現(xiàn)數(shù)字控制。器件接收16 位命令字,產(chǎn)生兩路D/A模擬輸出。TLV5618只有單一I/O周期,由外部時(shí)鐘SCL K決定,延續(xù)16 個(gè)時(shí)鐘周期,將命令字寫入片內(nèi)寄存器,完成后即進(jìn)行D/A轉(zhuǎn)換。TLV5618讀入命令字是從CS的下降沿開始有效,從下一SCLK的下降沿開始讀入數(shù)據(jù),讀入16位數(shù)據(jù)后即進(jìn)入轉(zhuǎn)換周期,直到下次出現(xiàn)CS的下降沿。

TLC2543是TI公司的帶串行控制和11個(gè)輸入端的12 位、開關(guān)電容逐次逼近型A/D轉(zhuǎn)換器。 片內(nèi)轉(zhuǎn)換器有高速、高精度和低噪音的特點(diǎn)。 TLC2543工作過程分為兩個(gè)周期:I/O周期和轉(zhuǎn)換周期。I/O周期由外部時(shí)鐘SCLK決定,延續(xù)8、12或16個(gè)時(shí)鐘周期,同時(shí)進(jìn)行兩種操作: 在SCLK上升沿以MSB方式輸入8位數(shù)據(jù)到片內(nèi)寄存器;在SCLK下降沿以MSB 方式輸出8、12、16位轉(zhuǎn)換結(jié)果。轉(zhuǎn)換周期在I/O周期的最后一個(gè)SCLK下降沿開始,直到EOC信號變高,指示轉(zhuǎn)換完成。 為了與TLV5618的I/O周期一致,采用了MSB方式,使用CS的16 時(shí)鐘傳送的時(shí)序。

由于這兩種器件都是SPI接口,可將這兩器件連接至同一SPI 總線,通過不同的片選信號對不同的器件操作。 由于SPI接口協(xié)議復(fù)雜,而且從圖3 可以看出,這兩種器件的時(shí)序并沒有用到全部的SPI接口時(shí)序。為了實(shí)現(xiàn)符合以上邏輯的時(shí)序,減少標(biāo)準(zhǔn)SPI 接口IP 核對FPGA資源的浪費(fèi), 設(shè)計(jì)采用Verilog硬件描述語言用同步狀態(tài)機(jī)(FSM)的設(shè)計(jì)方法實(shí)現(xiàn),編寫ADC及DAC控制時(shí)序。程序?qū)嶋H上是一個(gè)嵌套的狀態(tài)機(jī),由主狀態(tài)機(jī)和從狀態(tài)機(jī)通過由控制線啟動的總線在不同的輸入信號情況下構(gòu)成不同功能的有限狀態(tài)機(jī)。 則由圖3 可知,D/A操作有4 個(gè)狀態(tài),A/D操作有7個(gè)狀態(tài)。 兩種狀態(tài)中有幾個(gè)狀態(tài)是相同的,故可用一個(gè)有限狀態(tài)機(jī)完成對串行A/D及D/A的操作。 程序?qū)嶋H上是一個(gè)嵌套的狀態(tài)機(jī),由主狀態(tài)機(jī)和從狀態(tài)機(jī)通過由控制總線啟動的總線在不同的輸入信號情況下構(gòu)成不同功能的較復(fù)雜的有限狀態(tài)機(jī)。 A/D及D/A操作共用唯一的驅(qū)動時(shí)鐘(SCLK) 及數(shù)據(jù)總線(SI、SO)。由于操作的寫周期有16個(gè)時(shí)鐘周期,讀周期有12個(gè)時(shí)鐘周期,模塊是在三個(gè)嵌套的有限狀態(tài)機(jī)中完成的。

系統(tǒng)設(shè)計(jì)中,將AD、DA操作封裝成一單獨(dú)模塊,由上層控制模塊輸出命令字及控制信號啟動本模塊的相應(yīng)操作,操作完成后(進(jìn)入idle狀態(tài)) ,本模塊發(fā)出相應(yīng)狀態(tài)信號至上層模塊。

FPGA 程序框架

FPGA 片內(nèi)程序是整個(gè)測試系統(tǒng)正確運(yùn)行的關(guān)鍵。 由自頂向下的FPGA 設(shè)計(jì)原則,將系統(tǒng)分為5個(gè)獨(dú)立的模塊, 即通信模塊(ISA) 、測試模塊(TEST) 、AD/DA 模塊、解碼模塊(DECODER) 、RAM 控制模塊(RAMCTL)。

ISA 模塊:系統(tǒng)通信及控制模塊,完成與上位機(jī)通信、命令字解釋、控制信號的產(chǎn)生等。系統(tǒng)根據(jù)上位機(jī)傳送的導(dǎo)通電阻、絕緣電壓等參數(shù)啟動ADDA模塊完成參考電壓的輸出;根據(jù)測試命令啟動測試模塊完成測試過程。數(shù)據(jù)在多個(gè)同步運(yùn)行的同步狀態(tài)機(jī)間傳送,較難控制的是多進(jìn)程間的數(shù)據(jù)通信與數(shù)據(jù)同步。

RAM控制模塊:在測試開始前,上位機(jī)將測試點(diǎn)的信息通過總線傳送至ISA模塊, ISA 模塊再將其存放到片內(nèi)RAM中;測試完成后,將RAM中的測試結(jié)果傳送到上位機(jī)。 在測試時(shí)測試模塊通過讀RAM中測試點(diǎn)的信息來打開相應(yīng)測試開關(guān),再將測試結(jié)果保存到RAM 中。 這樣兩個(gè)模塊都要求讀寫RAM 以實(shí)現(xiàn)兩個(gè)模塊之間的數(shù)據(jù)共享,這就要求有一控制信號將兩組讀寫信號線分別與RAM模塊相連接,RAM控制模塊即完成此功能。測試模塊(TEST):雖然測試過程有多種,如開關(guān)卡自檢、導(dǎo)通測試、絕緣測試等,但測試過程卻是相同的,即測試掃描。 測試的工作過程是:加比較電路參考電壓→打開待測點(diǎn)開關(guān)→延時(shí)→讀比較器結(jié)果→測試另一組測試點(diǎn)。 本模塊是按照不同的操作碼,進(jìn)入不同的測試過程。 測試結(jié)果與測試點(diǎn)編號一起組成13 位數(shù)據(jù)保存到RAM 中,并將原來測試點(diǎn)的編號信息覆蓋。

解碼模塊(DECODER):這一模塊掛在測試模塊(TEST) 之后,它完成開關(guān)編號到實(shí)際電路的映射。 由于測試針陣形式不同、譯碼電路與控制電路的硬件設(shè)計(jì)不同,上級模塊輸出的測試開關(guān)信息并不能直接作為輸出控制測試開關(guān)電路。 解碼模塊完成這兩者間的轉(zhuǎn)換。

AD/DA 模塊(AD/DA):設(shè)計(jì)SPI 總線接口對A/D 及D/A 器件操作,模塊以允許(adenable , daenable) 信號啟動,以busy信號作為轉(zhuǎn)換完成標(biāo)志信號,將A/D及D/A操作相對其它模塊進(jìn)行封裝。系統(tǒng)的每個(gè)模塊采用Verilog硬件描述語言編寫,采用多個(gè)多層嵌套的同步狀態(tài)機(jī)(FSM)完成整個(gè)系統(tǒng)的邏輯功能;每一模塊應(yīng)用仿真工具M(jìn)odelsim完成模塊的功能仿真,系統(tǒng)完成功能測試后;利用Altera 綜合布線工具QuartusII完成系統(tǒng)后仿真及綜合、布線、下載;充分利用Altera公司免費(fèi)提供的IPcore 對程序模塊進(jìn)行優(yōu)化;頂層設(shè)計(jì)采用方框圖輸入方式,模塊間的數(shù)據(jù)流由方框圖更直觀地表現(xiàn)出來。

結(jié)束語

基于FPGA的PCB測試機(jī)的硬件控制系統(tǒng),提高了PCB測試機(jī)的測試速度、簡化電路的設(shè)計(jì)。此外由于FPGA的可重構(gòu)特性,為系統(tǒng)的軟件算法以及硬件結(jié)構(gòu)的進(jìn)一步優(yōu)化升級打下了良好的基礎(chǔ),具有良好的應(yīng)用前景。

責(zé)任編輯:ct

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605999 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43177

發(fā)布評論請先 登錄

相關(guān)推薦

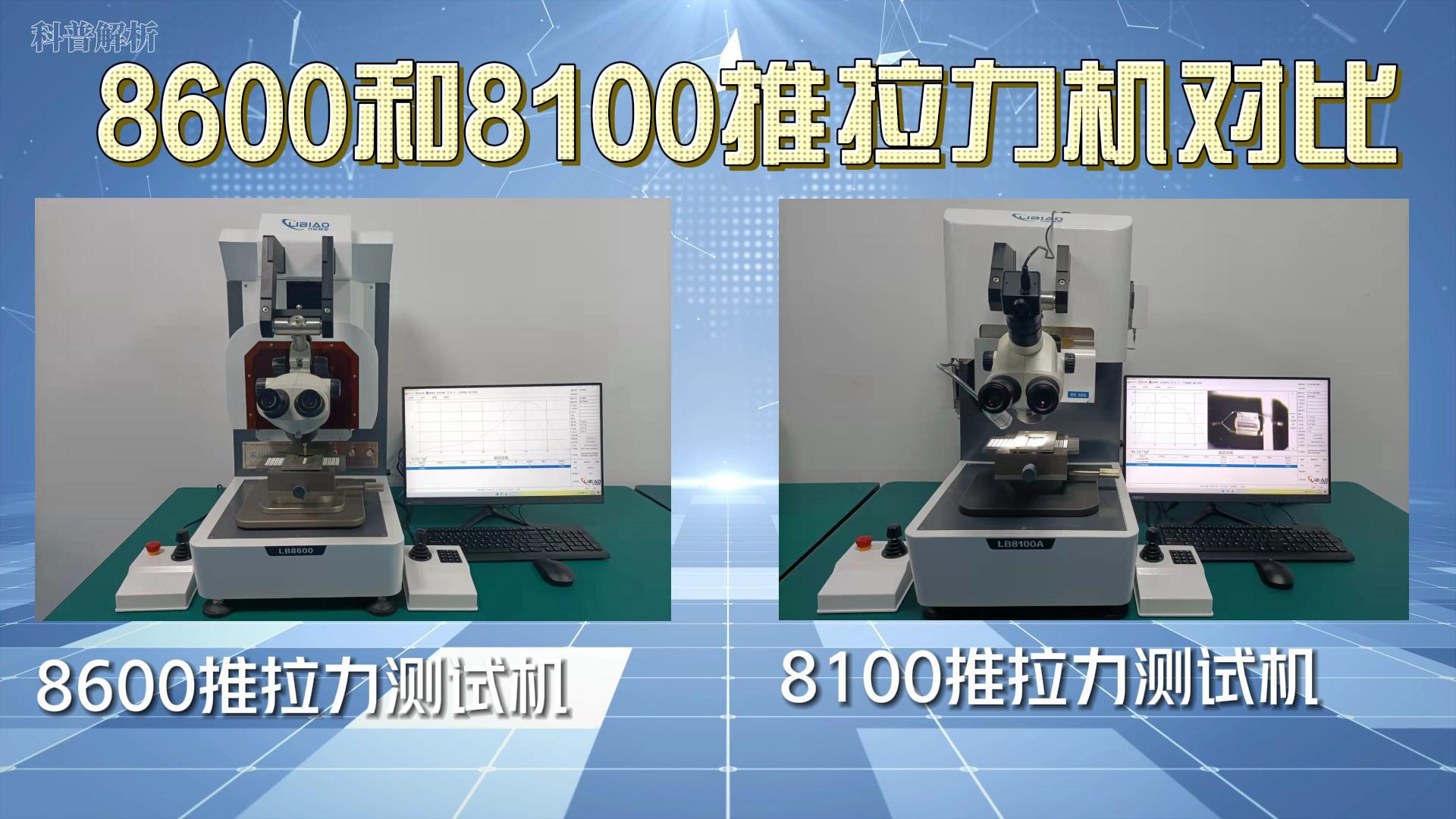

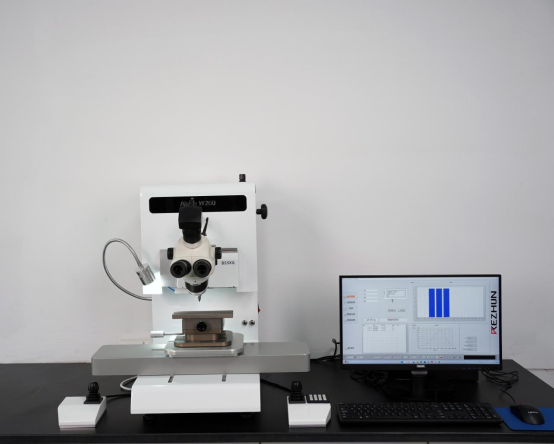

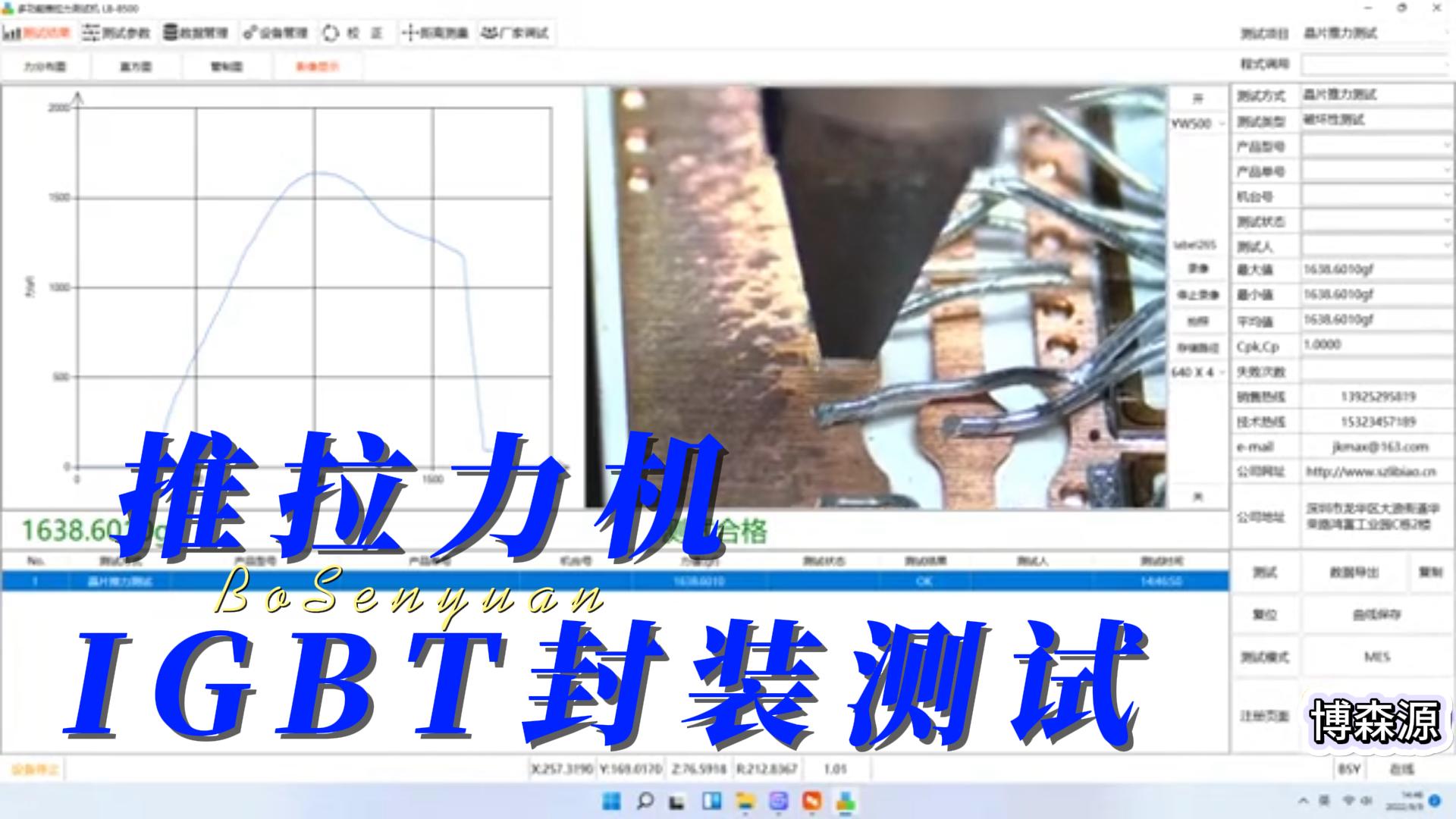

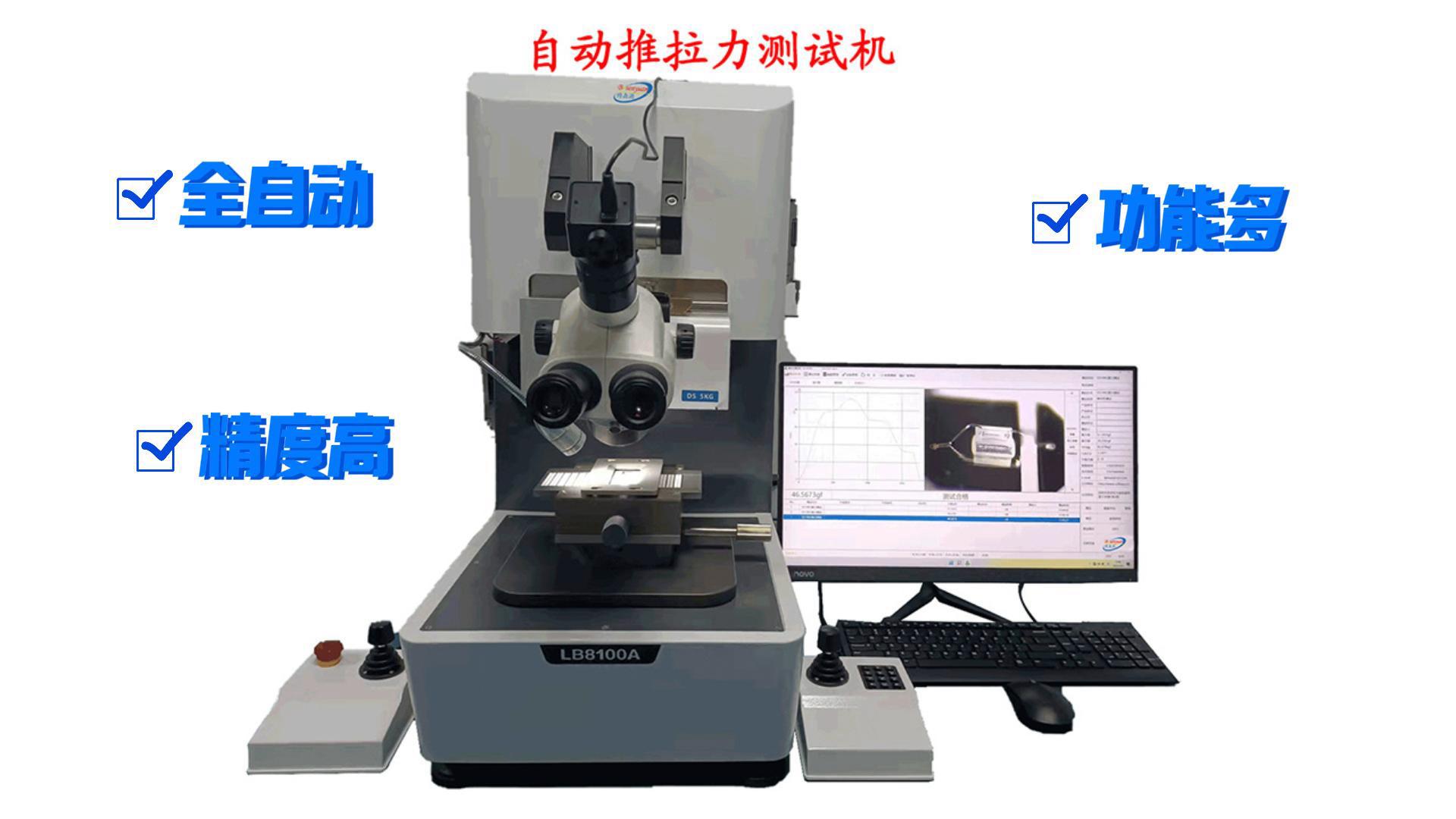

多功能推拉力測試機(jī):原理及應(yīng)用

鍵合拉力試驗(yàn)led推力測試機(jī)倒裝剪切力測試機(jī)#元器件精密推拉力測試機(jī)

多功能推拉力測試機(jī)測試費(fèi)用是多少?

多功能推拉力測試機(jī)可實(shí)現(xiàn)芯片貼裝剪切力測試

博森源推拉力測試機(jī)的硬件和軟件組成部分

推拉力測試機(jī)在各種工業(yè)應(yīng)用中,扮演著至關(guān)重要的角色

推拉力測試機(jī)器測試前的準(zhǔn)備有哪些?最全作業(yè)指導(dǎo)

廣立微推出全新T4000 Max半導(dǎo)體參數(shù)測試機(jī)

半導(dǎo)體芯片封裝推拉力測試機(jī)合理選擇需要考慮哪些方面?

基于FPGA的PCB測試機(jī)如何去設(shè)計(jì)硬件電路

基于FPGA的PCB測試機(jī)如何去設(shè)計(jì)硬件電路

評論