低功耗,高性能電路經(jīng)常受到電源相關(guān)問題的困擾。這種常見的情況經(jīng)常是由于神話(或誤用)的經(jīng)驗(yàn)法則。

這些經(jīng)驗(yàn)法則常常導(dǎo)致我們走向錯(cuò)誤的方向,讓事情變得更糟而不是更好。在本文中,我將重點(diǎn)介紹工程師最常犯的一些錯(cuò)誤,并分享一些為敏感電路設(shè)計(jì)清潔電源的基本規(guī)則。應(yīng)用這些規(guī)則將導(dǎo)致更高的性能,更低成本的設(shè)計(jì)和更少的設(shè)計(jì)迭代。

什么是敏感電路?

敏感電路是那些可以容易因電源噪聲而降級(jí)。這些電路通常包括振蕩器,LNA,收發(fā)器,混頻器和ADC。我可能會(huì)收到許多讀者添加到我的列表中的電子郵件,并且理所當(dāng)然,所以請(qǐng)將這些作為一些示例而不是全面的列表。

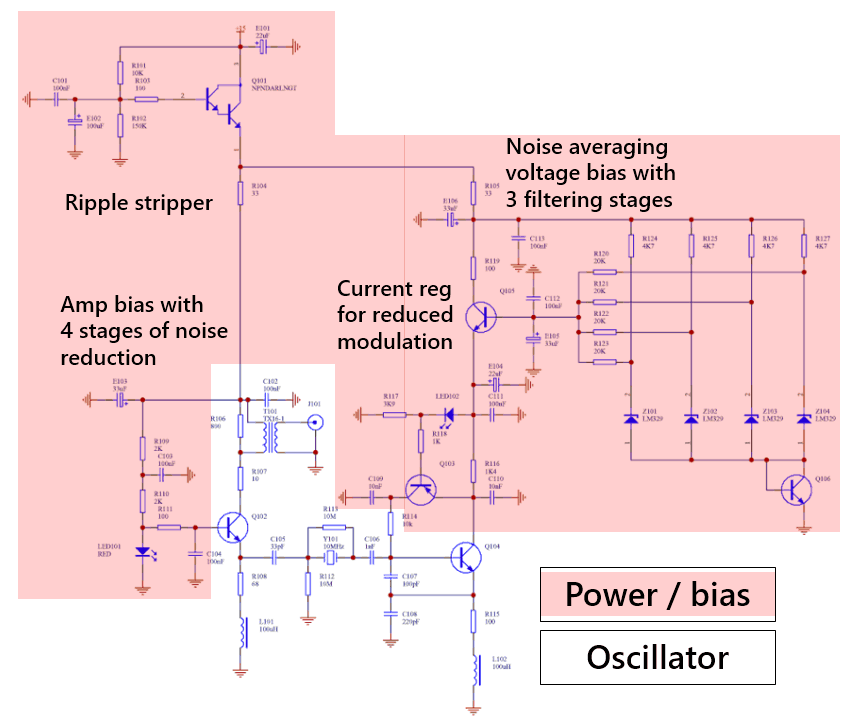

經(jīng)驗(yàn)豐富的振蕩器設(shè)計(jì)人員非常了解與之相關(guān)的挑戰(zhàn)。電源。這在圖1所示的振蕩器原理圖中非常明顯。本設(shè)計(jì)中大約75%的元件與電源有關(guān),而25%的元件與振蕩器有關(guān)。

圖。 1電路與白色振蕩器有關(guān),而電源電路則突出顯示。

敏感電路對(duì)什么敏感?

顯而易見的答案是電路對(duì)電源噪聲敏感,對(duì)嗎?圖1中的振蕩器電路可以表示為只有兩個(gè)連接(或RF用戶端口)的電路 - 電源輸入和振蕩器輸出,因此您可能會(huì)得出噪聲顯然是由電源產(chǎn)生的結(jié)論供應(yīng)。這個(gè)明顯的結(jié)論是工程師在為敏感電路設(shè)計(jì)電源時(shí)所犯的最常見錯(cuò)誤的原因。另外兩個(gè)重要問題是噪聲來自何處以及它是如何實(shí)現(xiàn)的?

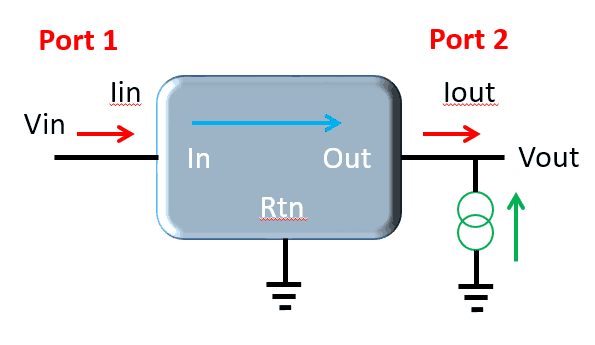

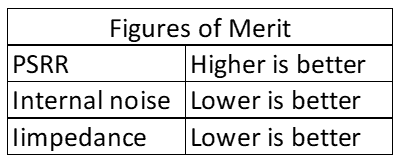

電源也可視為只有兩個(gè)連接(或端口)的電路 - 電源輸入和電源的輸出。這種簡(jiǎn)單的視圖,如圖2所示,無論電源是包括電壓調(diào)節(jié)器,無源噪聲濾波器還是僅連接在電源輸入和輸出之間的導(dǎo)線,都是有效的。電源輸出端的噪聲是通過不同路徑流向輸出端的獨(dú)立噪聲源的總和。例如,電源輸入端存在的電壓噪聲流過輸出端。該路徑定義為電源抑制比或PSRR。因此,電源的品質(zhì)因數(shù)是PSRR,并且更高的PSRR性能導(dǎo)致在電源輸出處出現(xiàn)的輸入噪聲更少。電源內(nèi)部也會(huì)產(chǎn)生噪聲。

對(duì)于開關(guān)穩(wěn)壓器,這很明顯,但即使是線性穩(wěn)壓器也會(huì)產(chǎn)生噪聲,并非所有穩(wěn)壓器都是相同的。因此,第二個(gè)品質(zhì)因數(shù)是自發(fā)電源噪聲。第三個(gè)噪聲路徑是電源呈現(xiàn)有限的非零輸出阻抗的結(jié)果。電源輸出的電流變化乘以電源阻抗,導(dǎo)致電源輸出電壓噪聲。這些電流擾動(dòng)可以由敏感負(fù)載電路,共享電源輸出的其他電路產(chǎn)生,或者甚至由于耦合到電源輸出的輻射電磁場(chǎng)產(chǎn)生。這導(dǎo)致了第三個(gè)品質(zhì)因數(shù);電源的輸出阻抗。

圖2簡(jiǎn)單的電源視圖突出了三個(gè)主要的噪聲源和路徑,導(dǎo)致三個(gè)品質(zhì)因數(shù)。

電源輸出端的噪聲量化為電源輸出的總和。來自這三條獨(dú)立路徑的噪音。

從前面的討論和公式1中,我們可以總結(jié)出三個(gè)電源的優(yōu)點(diǎn),為敏感電路供電,盡管這些品質(zhì)因數(shù)也廣泛適用于其他電路。

工程師在這些應(yīng)用中最常犯的錯(cuò)誤

解決(1)需要至少三個(gè)數(shù)據(jù):

電源噪聲對(duì)敏感電路性能的影響

敏感電路產(chǎn)生的噪聲電流。

敏感電路的阻抗

最常見的錯(cuò)誤是設(shè)計(jì)沒有這三個(gè)數(shù)據(jù)的電源。最常見的一個(gè)原因是盡管這些信息很關(guān)鍵,但它很少(如果有的話)作為電路規(guī)范或數(shù)據(jù)表的一部分提供,因此需要設(shè)計(jì)人員進(jìn)行測(cè)量。獲取這些數(shù)據(jù)對(duì)于設(shè)計(jì)具有成本效益的合適電源非常重要

明確的勝利之路

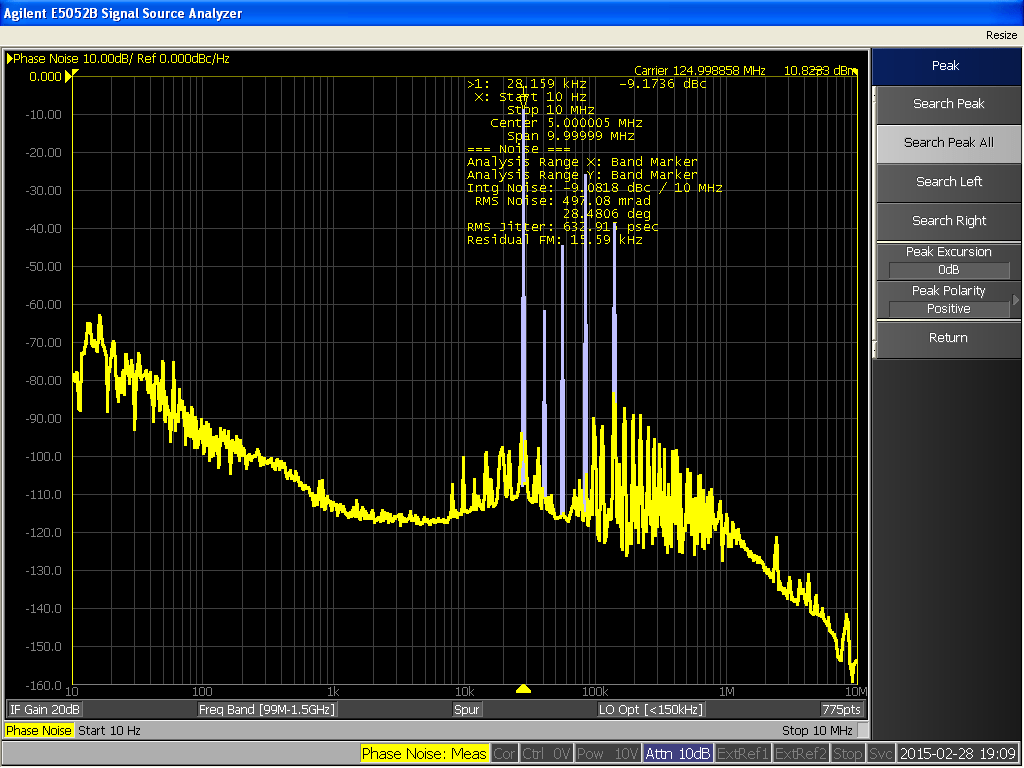

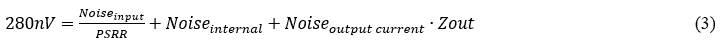

Don‘在獲得或測(cè)量敏感電路對(duì)電源噪聲的靈敏度之前,請(qǐng)執(zhí)行任何其他操作。這通常涉及在潔凈工作臺(tái)電源和敏感電路之間連接Line Injector設(shè)備(https://www.picotest.com/products_J2120A.html)。在監(jiān)視敏感電路的輸出時(shí)調(diào)制線路注入器,在圖3所示的示例中為振蕩器。電源由20mV,28kHz正弦波調(diào)制。測(cè)量結(jié)果顯示由電源調(diào)制信號(hào)產(chǎn)生的振蕩器輸出中的噪聲雜散,以及調(diào)制信號(hào)的一些諧波。

Fig。 3使用線路注入器設(shè)備將20mV,28kHz正弦波添加到電源中,并監(jiān)控產(chǎn)生的雜散。標(biāo)記在-9dBc處表示峰值,而基數(shù)約為-110dB。 20mV噪聲產(chǎn)生的雜散幅度為100dB。

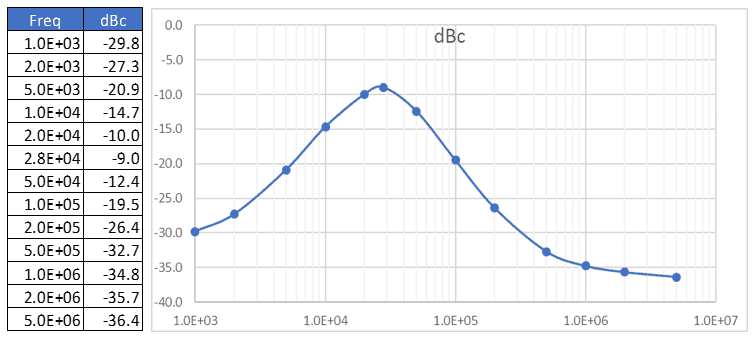

這個(gè)調(diào)制電源和監(jiān)測(cè)產(chǎn)生的雜散的過程在很多頻率上重復(fù),結(jié)果列表并繪制成圖,如圖.4。

圖4電源以多個(gè)頻率進(jìn)行調(diào)制,同時(shí)記錄振蕩器輸出中的相應(yīng)噪聲雜散。結(jié)果以圖形方式顯示,突出顯示了PLL的靈敏度。

圖4中的圖表顯示被測(cè)振蕩器對(duì)30kHz時(shí)的電源噪聲最敏感。該響應(yīng)是振蕩器內(nèi)部的鎖相環(huán)(PLL)的典型響應(yīng)。最大靈敏度的頻率是PLL電路設(shè)計(jì)的函數(shù),可以是幾kHz到幾十MHz的任何值。

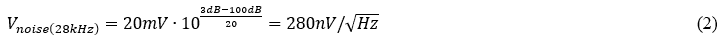

圖3中的雜散幅度約為100dB,從大約-110dBc延伸到峰值為-9dBc。由于電源噪聲導(dǎo)致3dB降級(jí),28kHz時(shí)的電源噪聲密度限制為最大值:

可以使用相同的步驟確定許多其他頻率的電源噪聲密度,從而提供與頻率相關(guān)的噪聲預(yù)算。代入(1)允許在三個(gè)噪聲源之間分配噪聲。

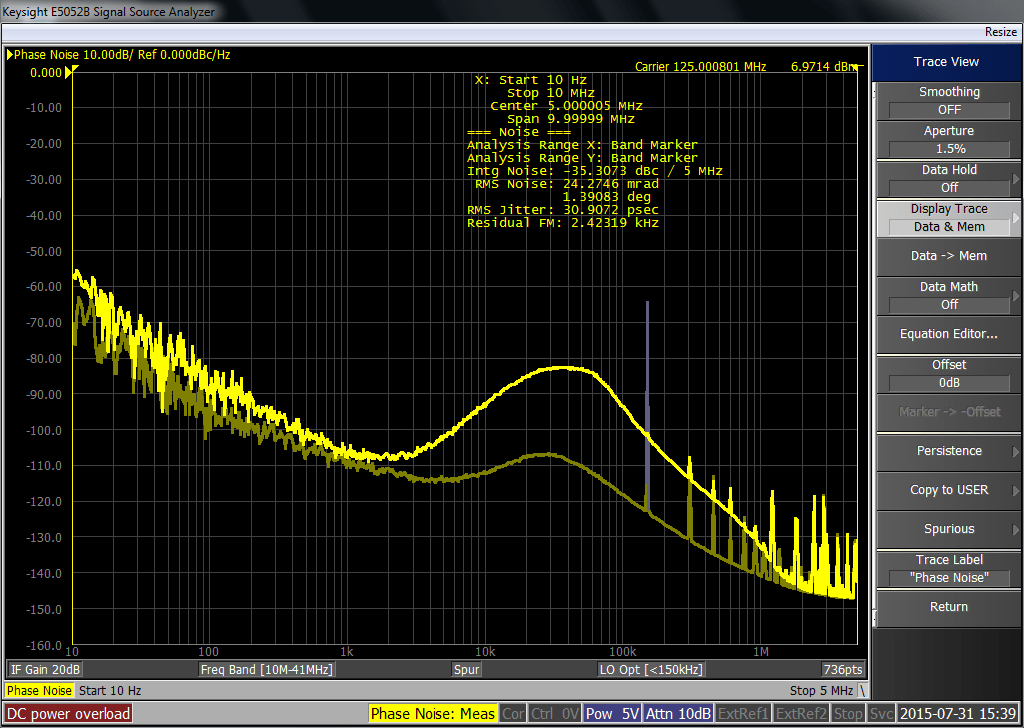

圖5中測(cè)量的相位噪聲曲線顯示了低噪聲低阻抗線性穩(wěn)壓器的結(jié)果,該穩(wěn)壓器直接通過2Ω串聯(lián)電阻為振蕩器供電。在這種情況下,這兩條曲線在28kHz處的差異大約為26dB。同樣,允許3dB降級(jí)會(huì)導(dǎo)致最大電源阻抗:

最小PSRR由輸入到電源時(shí)的最大噪聲確定供應(yīng)為:

超過這些要求超過幾分貝不會(huì)提高性能,因此無法證明更昂貴的電源。

圖5振蕩器相位噪聲使用低阻抗電源測(cè)量,并且在電源和振蕩器之間串聯(lián)2Ω。額外的2Ω導(dǎo)致28kHz時(shí)相位噪聲出現(xiàn)26dB的差異。》

第三種常見的失誤是(不恰當(dāng)?shù)兀┨砑予F氧體磁珠和陶瓷電容來過濾噪聲或糾正由此引起的不足。前兩個(gè)錯(cuò)誤。評(píng)估敏感電路的輸入阻抗非常重要,因?yàn)槊舾须娐穬?nèi)部通常有陶瓷電容。鐵氧體磁珠在低頻時(shí)可以非常電感,從而提高了電源的阻抗,因此需要電容來抵消電感。所需的電容可以由上面(4)中計(jì)算的磁珠電感值和輸出阻抗確定。例如,使用電感為2uH的磁珠:

電容器的ESR應(yīng)近似等于(4中計(jì)算的電阻) )以此為例:

請(qǐng)注意,所需的電容可能非常大。 降低 ESR和/或電容將導(dǎo)致阻抗諧振和降低的電路性能。最后一個(gè)考慮因素是該濾波電容的ESL可以與敏感電路內(nèi)部的任何陶瓷電容共振。假設(shè)濾波電容ESL為2nH(對(duì)電解電容合理猜測(cè)),則保持低Q值以避免阻抗諧振,要求陶瓷電容為:

同樣,如果該陶瓷電容器的ESR為0.14Ω,與(4)和(7)一致,則可實(shí)現(xiàn)最佳性能。這可能需要一個(gè)外部串聯(lián)電阻或一個(gè)ESR控制的陶瓷電容。

結(jié)論

如果按照以下方法設(shè)計(jì)敏感電路的最佳電源很簡(jiǎn)單我在這里概述了三個(gè)步驟。

首先,獲取電路電源靈敏度的數(shù)據(jù)。這通常意味著自己獲取數(shù)據(jù)或要求供應(yīng)商以類似于我在此處顯示的形式提供數(shù)據(jù)。

其次,使用測(cè)量來確定電路對(duì)電源電阻的敏感度。/p》

第三,確保你知道電路輸入電阻的阻抗。

參考文獻(xiàn)

S 。 M. Sandler,時(shí)鐘功率優(yōu)化取決于抖動(dòng)控制,電子設(shè)計(jì)2012年9月9日www.electronicdesign.com/analog/clock-power-optimization-depends-jitter-control

S上。 M. Sandler,對(duì)時(shí)鐘抖動(dòng)進(jìn)行故障診斷并識(shí)別PDN靈敏度, EEWeb 2016年4月11日www.eweweb.com/blog/eeweb/troubleshooting-clock-jitter-and-identifying-pdn-sensitivities

Keysight如何設(shè)計(jì)Power Integrity YouTube視頻系列www.keysight.com/find/how-to-videos-for-pi

解決時(shí)鐘抖動(dòng)問題, Keysight解決方案手冊(cè)http://literature.cdn.keysight.com/litweb/pdf/5992-1645EN.pdf?id=2767985

低相位噪聲設(shè)計(jì):Crystal Oscillatorshttp://www.ko4bb.com/~布魯斯/CrystalOscillators.html

-

敏感電路

+關(guān)注

關(guān)注

0文章

18瀏覽量

7633

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

從應(yīng)用實(shí)例看干擾敏感電路系統(tǒng)設(shè)計(jì)要點(diǎn)

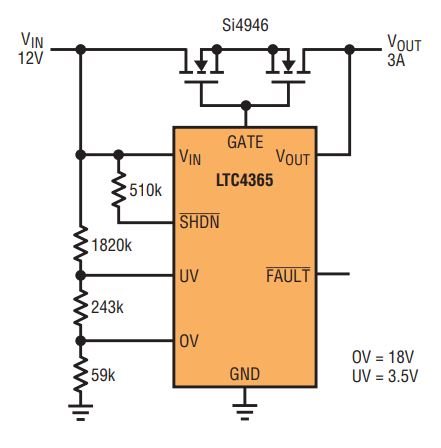

如何為敏感電路提供過壓及電源反接保護(hù)?

什么是敏感電阻_敏感電阻種類特點(diǎn)

什么是敏感電阻,敏感電阻的種類特點(diǎn)是什么

無需阻塞二極管即可保護(hù)敏感電路免受過壓和反向電源連接的影響

通過Intel Curie進(jìn)行運(yùn)動(dòng)敏感電路控制

為敏感電路提供過壓及電源反接保護(hù)!

為敏感電路設(shè)計(jì)清潔電源的基本規(guī)則概述

為敏感電路設(shè)計(jì)清潔電源的基本規(guī)則概述

評(píng)論