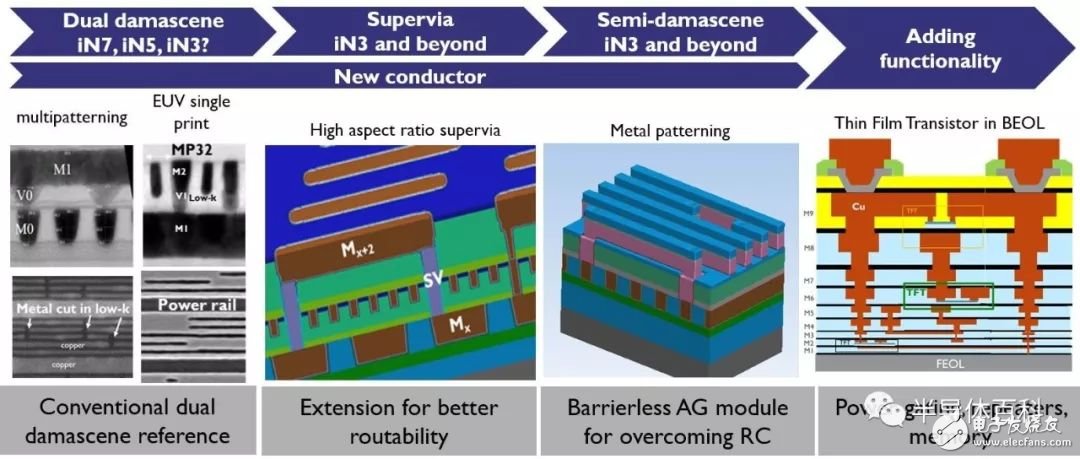

將互連擴展到3nm技術節點及以下需要多項創新。IMEC認為雙大馬士革中的單次顯影EUV,Supervia結構,半大馬士革工藝以及后段(BEOL)中的附加功能是未來的方向。IMEC納米互連項目總監Zsolt Tokei闡述了這些創新 ,這些創新已在ITF USA和最新的IITC會議上公布。

當今的互連技術

金屬互連 ,芯片后段(BEOL)中的微小布線,用于分配時鐘和其他信號,為各種電子系統組件提供電源和接地,并連接芯片前段(FEOL)的晶體管。互連線由不同的金屬層組成:本地(local Mx),中間層(intermediate),半全局(semi-global)和全局(global)線。總層數可以多達15個,而Mx層的典型數量范圍在3到6之間。這些層中的每一個都包含(單向)金屬線(或軌道)和介電材料。它們通過填充金屬的通孔結構垂直互連。由于在在90年代中期引入雙大馬士革銅制程和低k電介質(例如SiO2,SiCO(H)和氣隙,因此銅在邏輯和存儲器芯片應用中一直是金屬線和通孔的主力金屬。

傳統的CMOS技術節點縮放,導致互連金屬線節距減小。雖然FinFET晶體管的尺寸縮放預計會減慢,但后段金屬節距仍然會保持以0.7倍左右的速度縮放,以跟上所需的面積縮放。目前正在生產的最先進的互連技術(即10nm和7nm技術節點)其local M1層,金屬節距縮小至36nm,以適應前段的縮放。同時,為了保持后段的性能,業界已經開始采用鈷(Co)和氣隙(Air gap)來制作金屬互連。

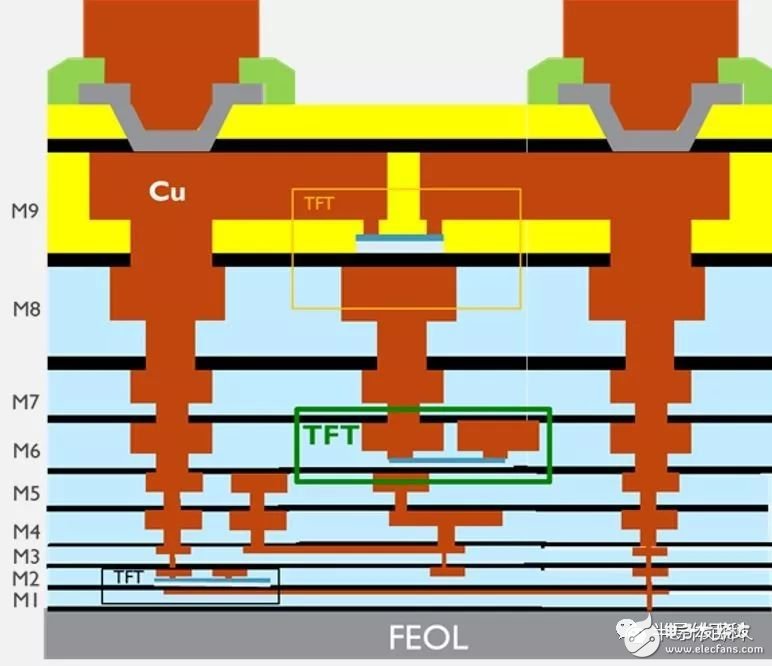

在中間互連層中集成薄膜晶體管(TFT)被認為是為BEOL增加額外功能的另一個機會。在該中間互連層中,通孔密度相對較低,這為諸如TFT等小晶體管提供了空間。這里,它們可用于各種應用,例如電源管理。BEOL中首批采用TFT的技術主要限于物聯網應用。

邁向3nm互連

低于5nm技術節點的器件尺寸縮小正變得越來越具有挑戰性。這主要是由于前段的電性和工藝漂移限制,以及后段線路中顯著的RC延遲和線路擁塞。RC延遲是由金屬線的橫截面積減小引起的,其導致互連系統的RC變高。這最終導致信號延遲和功耗的大幅增加。這些問題在幾個節點之前就開始了,每一代技術都在變得越來越糟。

為了繼續超越5nm技術節點的互連擴展,IMEC正在探索各種新的工藝創新,微縮助推器和材料。特別是,用于未來互連的工藝“工具箱”包括在雙大馬士革工藝中引入單次極紫外(EUV)光刻,與氣隙結合的半大馬士革工藝,以及諸如Supervia結構的微縮助推器以實現更好的可布線性。所有這些創新都需要新的導體材料,與傳統的Cu或Co相比具有更好的品質因數。“工具箱”與BEOL中的TFT集成相結合,可實現各種附加功能。在接下來的部分中,將更詳細地討論這些新穎的互連結構。

用于將互連擴展到3nm及以下的“工具箱”

雙大馬士革工藝

在轉向新的集成工藝之前,半導體行業將盡可能長時間地擴展當前的雙大馬士革工藝。將雙大馬士革工藝延伸到較小金屬節距的關鍵是引入單次EUV光刻以圖案化最密集的線(M1和M2)和通孔(V1),這降低了工藝復雜性。對于當前浸沒式光刻的多重顯影,單次顯影EUV將實現成本效益且具有更短的工藝流程。這種方法的真正效益將在制作低至少30nm節距的金屬線時體現出來。

在IITC2019展會上,IMEC展示了3nm 節點的雙大馬士革工藝TQV結果。M1層用單次顯影EUV工藝制作。為了實現M2 的21nm節距,IMEC提出了一種混合光刻方案,使用193i SAQP來制作線和溝槽,以及單次顯影EUV用于制作隔斷和通孔。此次TQV實現了無阻擋層的釕(Ru)金屬連線方案和介電常數k = 3.0的絕緣介質層。與前幾代產品相比,RC獲得了30%的改善,而且擁有相同的可靠性。

21nm間距雙大馬士革試驗車的RC特性

目前,IMEC團隊正在探索實現16nm金屬節距的可行性。這就需要多重顯影方案,由于工藝漂移和機械穩定性問題,16nm金屬節距依然挑戰重重。

半大馬士革工藝

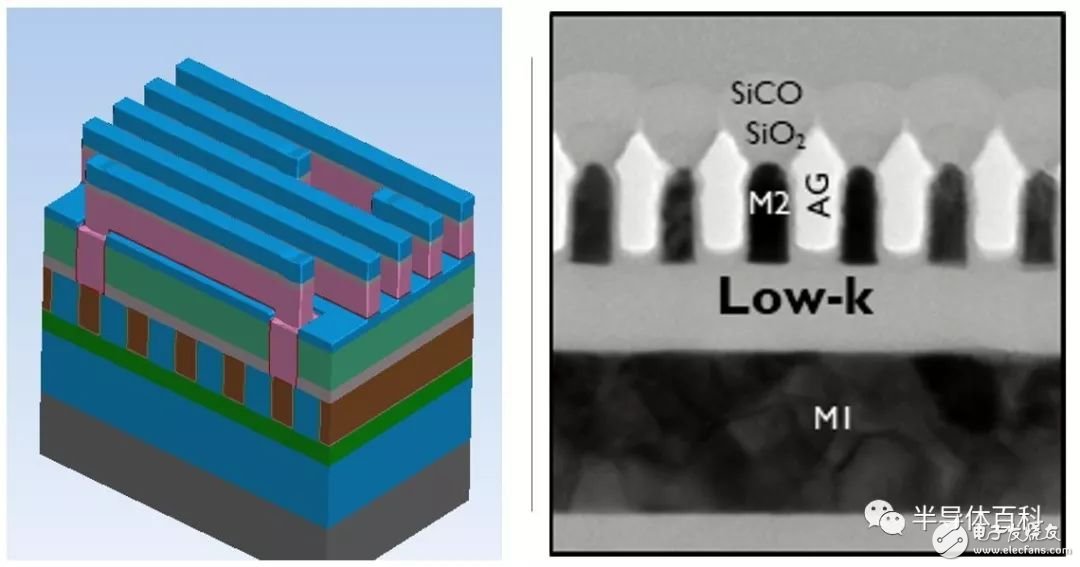

將基于大馬士革工藝擴展到16nm金屬節距的另一種有趣方法是引入半大馬士革工藝。它可以與傳統的雙大馬士革工藝結合使用。雙大馬士革和半大馬士革之間的本質區別在于省略了金屬的化學機械拋光(CMP)步驟。

半大馬士革開始于通孔開口的光刻并蝕刻介電膜。然后用金屬(例如Ru)填充通孔并過填充(意味著繼續沉積金屬),直到在電介質上形成金屬層。然后掩蔽并蝕刻金屬以形成金屬線。

與傳統大馬士革工藝相比,半大馬士革的真正優勢在于能夠降低工藝漂移并在金屬線之間形成氣隙(傳統電介質的替代品)。當采用釕(Ru)作為導體時,在電介質和導體之間不需要擴散阻擋層。在傳統雙大馬士革工藝中,在較高縱橫比下的電容增加被視為改善互連RC的主要障礙。需要更高的深寬比來降低電阻和工藝漂移,但是它們的積極效果被不希望的電容增加所消除。使用無阻擋層的釕(Ru)金屬線搭配氣隙的半大馬士革工藝可以解決這個問題。

早些時候,IMEC團隊展示了其工藝可行性。最近它與EUV單次顯影相結合,產生均勻的30nm金屬節距線,如下圖(右)。

半大馬士革工藝:示意圖和SEM切片

Supervia實現更好的可布線性

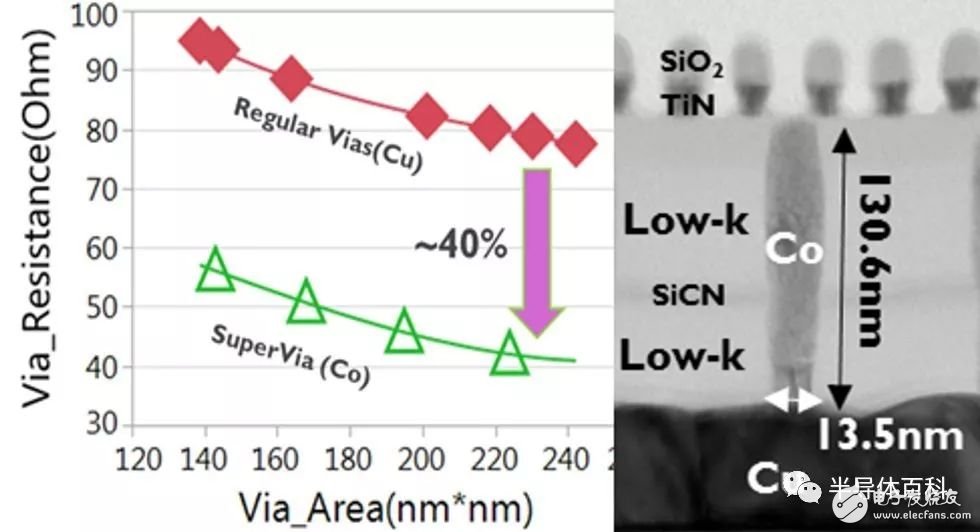

互連領域的下一個游戲規則改變者是Supervia結構,高深寬比的通孔,以最簡單的形式連接Mx層和Mx + 2層。Supervia屬于縮放助推器系列,用于減少軌道數量,因此可以降低標準邏輯單元的單元高度。

在其最簡單的形式中,Supervia通過以自對準方式繞過中間Mx + 1層,提供從Mx到Mx + 2金屬層的直接連接,Supervia和常規通孔可以在同一設計中共存。

(左)通孔電阻與面積關系(右)Supervia結構 第一個用例是SRAM結構和掩埋電源軌結構,即埋在芯片前段的電源軌,以幫助釋放互連的布線資源。例如,在2019年IITC,IMEC展示了具有高良率和低電阻率的Ru回蝕刻工藝(埋入式電源軌集成的關鍵工藝)。

為了將Supervia結構擴展到3nm節點之外,IMEC定義了一個Supervia工藝路線圖,其中包含第二代(從Mx到Mx + 3和Mx + 4)和第三代(從Mx到Mx+ 5)。這個最終的第三代,也被稱為‘Ubervia’,是非常復雜和仍遠未實現的。但它可以從Mx直接“跳”到更寬的金屬線,從而進一步降低RC。

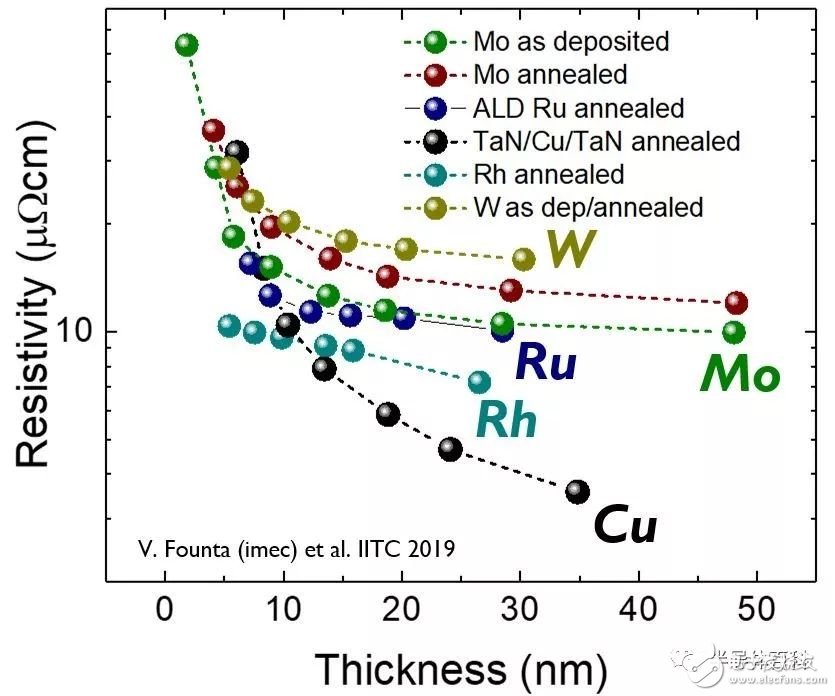

關鍵促成因素:替代導體

多年來,IMEC一直致力于尋找新金屬,以取代傳統的Cu,鎢(W)和鈷(Co)在各種互連中的應用。這些替代導體將是實現上述創新的關鍵,包括“下一代”雙大馬士革和半大馬士革工藝,以及Supervia結構。

尋求替代金屬的第一步:定義品質因數(FOM),以給候選材料進行排名。該FOM定義為體電阻率與金屬中載流子平均自由程的乘積。現在科學界廣泛認為Cu,W和Co是材料排名的基準點。具有最低FOM的金屬是銠(Rh),然后是鉑(Pt),銥(Ir),鎳(Ni),Ru,鉬(Mo)和鉻(Cr)。然而,排名不包括成本,退火敏感度或與電介質的粘附性等指標。例如,Ir和Rh對電介質的粘附性非常差,特別是Rh非常昂貴,甚至比金(Au)貴。在實驗方面,IMEC證明了Mo是一種非常有前途的互連金屬,特別是作為W的潛在替代品。關于替代金屬的工作已在2019年IITC上提出。

尋找替代導體:Mo的薄膜研究

該團隊還研究了二元和三元化合物作為傳統導體的替代品。特別是所謂的“MAX相”,其比純單質金屬有更好的性能。MAX相是由早期過渡金屬(M),A族元素(A)和碳或氮(X)組成的分層結構。

最后,還可以通過用石墨烯覆蓋連線來降低諸如Ru的金屬的電阻率。石墨烯已知具有原子級薄,并且具有高導電性和導熱性以及高載流能力。在IITC2019,IMEC證明了制造的石墨烯包覆的Ru線具有較低的電阻率和較高的熱穩定性。這些發現為碳/金屬互連提供了可能的途徑。

向BEOL添加功能

在高級節點芯片的中間M6到M8互連級別,通孔密度相對較低,可提供實現小晶體管的空間。薄膜晶體管足夠小且溫度兼容,可以完成這項任務,從而為BEOL增加了額外的功能。

BEOL中的TFT:示意圖

目標應用是服務器和移動應用的電源管理,雙V T邏輯電路,FPGA(具有大型SRAM陣列),用于電壓轉換的高壓I / O,用于神經形態概念的信號緩沖器(buffer)。它也可以在DRAM存儲器中找到它的方式,或者用于非易失性存儲器的選擇器(selector)。

最終的互連夢想是將它們用作中繼器,中繼器在當前設計中占據了很大一部分面積。但是,由于需要n型和p型TFT,后者對于實際實現來說還達不到要求。BEOL的其他挑戰包括可靠性,CMOS工藝技術的成熟度以及成本,盡管在這些“寬松”尺寸下,可以使用簡單的單次浸沒式光刻技術來提高其成本效益。

IMEC團隊最近在300mm晶圓上提供了功能性銦鎵鋅氧化物(IGZO)TFT的硬件演示,即使在高溫下也具有低漏電。

總結

在本文中,imec提出了幾種未來的方案,這些方案有望解決RC延遲問題,并將互連擴展到3nm技術節點及更高版本。通過啟用新工藝(例如半大馬士革),新的縮放助推器(Supervia,以獲得更好的可布線性),新材料(例如替代導體和氣隙)以及通過添加功能來減小面積和降低成本。

-

CMOS

+關注

關注

58文章

5735瀏覽量

236090 -

半導體

+關注

關注

334文章

27703瀏覽量

222628 -

IMEC

+關注

關注

0文章

58瀏覽量

22285 -

EUV

+關注

關注

8文章

608瀏覽量

86145

發布評論請先 登錄

相關推薦

蘋果iPhone 17或沿用3nm技術,2nm得等到2026年了!

意瑞半導體亮相第五屆汽車電驅動及關鍵技術大會

臺積電產能爆棚:3nm與5nm工藝供不應求

臺積電3nm制程需求激增,全年營收預期上調

臺積電3nm/5nm工藝前三季度營收破萬億新臺幣

臺積電3nm代工及先進封裝價格或將上漲

臺積電3nm產能供不應求,驍龍8 Gen44成本或增

三星電子:加快2nm和3D半導體技術發展,共享技術信息與未來展望

華光光電808nm高功率半導體激光芯片研究取得重大技術突破

實現3nm技術節點需要突破哪些半導體關鍵技術

實現3nm技術節點需要突破哪些半導體關鍵技術

評論