據(jù)報道,長鑫存儲技術(shù)有限公司(CXMT)公布了最新的DRAM技術(shù)路線圖,從其路線規(guī)劃來看,其研發(fā)的產(chǎn)品線包括DDR4、LPDDR4X、DDR5以及LPDDR5、GDDR6,雖然未公布具體時間節(jié)點,但產(chǎn)品發(fā)展線路與三星、SK海力士、美光等國際大廠DRAM發(fā)展大體一致。

目前,全球主要的DRAM廠商三星、SK海力士、美光等采用的是1ZnmDRAM技術(shù)。其中三星在2019年3月宣布將在下半年采用1Znm工藝技術(shù)量產(chǎn)8GbDDR4,生產(chǎn)率提高20%以上;美光也在8月份大規(guī)模生產(chǎn)1Znm16GbDDR4產(chǎn)品,SKHynix也采用第三代10nm級(1znm)工藝開發(fā)出了16GbitDDR4。

長鑫存儲正在使用其10G1技術(shù)(19nm工藝)來制造4Gb和8Gb DDR4存儲器芯片,目標在2020年第一季度將其商業(yè)化并投放市場,該技術(shù)將用于在2020下半年制造的LPDDR4X存儲器,雖然在工藝上不及國際DRAM原廠,但差距在一步一步的縮小。

長鑫存儲還規(guī)劃將采用10G3(17nm工藝)發(fā)展DDR4、LPDDR4X、DDR5以及LPDDR5產(chǎn)品,采用10G5工藝推出DDR5、LPDDR5以及GDDR6產(chǎn)品,該技術(shù)是使用HKMG和氣隙位線技術(shù),并在未來導(dǎo)入使用柱狀電容器、全能柵極晶體管以及極紫外光刻(EUV)工藝。

長鑫DRAM技術(shù)發(fā)展為何如此受關(guān)注?

DRAM是最常見的系統(tǒng)內(nèi)存,被喻為連接中央處理器的“數(shù)據(jù)高速公路”,廣泛用于PC、手機、服務(wù)器等領(lǐng)域,是集成電路產(chǎn)業(yè)產(chǎn)值占比最大的單一芯片品類。中國是DRAM芯片最大的應(yīng)用市場,然而自主產(chǎn)能卻相當(dāng)匱乏,其產(chǎn)能的95%被韓國三星、海力士、美國美光壟斷。長鑫存儲的出現(xiàn)填補了國內(nèi)DRAM的空白,有望突破韓國、美國企業(yè)在國際市場的壟斷地位。

長鑫12英寸存儲器晶圓制造基地項目,是中國大陸唯一擁有完整技術(shù)、工藝和生產(chǎn)運營團隊的DRAM項目,目標是打造設(shè)計和制造一體化的內(nèi)存芯片國產(chǎn)化制造基地,項目于2016年由合肥市產(chǎn)業(yè)投資(控股)集團有限公司和北京兆易創(chuàng)新科技股份有限公司合作投資。

當(dāng)時長鑫存儲項目與長江存儲和福建晉華并稱為中國存儲產(chǎn)業(yè)的三大探路者,備受業(yè)界關(guān)注。今年9月20日,長鑫存儲技術(shù)有限公司在大會上宣布:總投資約1500億元的長鑫存儲內(nèi)存芯片自主制造項目正式投產(chǎn),其與國際主流動態(tài)隨機存取存儲芯片(DRAM)同步的10納米級第一代8GbDDR4在大會上首度亮相,一期設(shè)計產(chǎn)能達每月12萬片晶圓,首批芯片今年底將會送到客戶手中。

中國科學(xué)技術(shù)大學(xué)特聘教授陳軍寧等業(yè)內(nèi)權(quán)威專家表示,長鑫存儲正式投產(chǎn)標志我國在內(nèi)存芯片領(lǐng)域?qū)崿F(xiàn)量產(chǎn)技術(shù)突破,擁有了這一關(guān)鍵戰(zhàn)略性元器件的自主產(chǎn)能。

長鑫存儲技術(shù)有限公司董事長兼首席執(zhí)行官朱一明透露,長鑫存儲投產(chǎn)的產(chǎn)品是現(xiàn)在全球市場上的主流產(chǎn)品,另一款供移動終端使用的低功耗產(chǎn)品也即將投產(chǎn)。

長鑫已開始DRAM新技術(shù)探索

長鑫存儲副總裁、未來技術(shù)評估實驗室負責(zé)人平爾萱在此前舉辦的中國閃存技術(shù)峰會(CFMS)上的介紹,合肥長鑫基于授權(quán)所得的奇夢達相關(guān)技術(shù)和從全球招攬的極具豐富經(jīng)驗的人才,長鑫存儲借助先進的機臺已經(jīng)把原本奇夢達的46納米DRAM平穩(wěn)推進到了10納米級別。公司也開始了在EUV、HKMG和GAA等目前還沒有在DRAM上實現(xiàn)的新技術(shù)探索。

DRAM是有它的極限的。平爾萱博士認為,我們可以通過改進,將極限推遲,如導(dǎo)入EUV及HKMG三極管以縮小線寬及加強外圍電路性能,就是DRAM產(chǎn)業(yè)的一個選擇,這在未來幾年將可以維持DRAM技術(shù)發(fā)展,滿足大數(shù)據(jù)時代的需求。

首先在EUV方面,平爾萱博士指出,EUV是繼193納米Immersion Scanner后又一個光刻機革命。它可滿足工藝精準度在持續(xù)微縮中不斷增加的要求。而DRAM又是一個十分密集堆疊的設(shè)計,且對信號要求十分嚴格,任何小的偏離都會對信號造成損失。那就意味著EUV技術(shù)的出現(xiàn)對DRAM技術(shù)的延展有很大的作用:如將線寬進一步減少以增加存儲密度。

“EUV主要是針對陣列。但外圍線路的增強及微縮也是近來DRAM技術(shù)發(fā)展的另一個機會”,平博士補充說。

他表示,在DRAM幾乎一半的外圍線路中,有一半是邏輯線路用的。在過往,這部分的CMOS一直都是用傳統(tǒng)的SiON/PolySiGate堆棧的。但這個堆棧在32/28納米階段碰到了瓶頸:一方面是SiON厚度已到極限,不能再薄了;另一方面,PolySi作為半導(dǎo)體材料,導(dǎo)電率也不足了,出現(xiàn)了嚴重的元器件性能不足。如在高端的圖顯DDR中,芯片性能速度明顯不足,這就需要引進更先進的HKMGCMOS提供更好性能。隨著DDR5的到來,HKMGCMOS的使用會越來越現(xiàn)實。

“由于DRAM制程中有電容這一段,因此HGMG制程的選擇需與電容制程匹配。所謂的GateFirst制程就可被選擇為DRAM邏輯線路CMOS制程”,平博士說。他進一步表示,通過引入HKMG,不但可以推動存儲密度進一步提高,接口速度也同步獲得了提升。

“為了繼續(xù)發(fā)展DRAM技術(shù),我們還需要在新材料、新架構(gòu)上進行更多探索,并與相關(guān)企業(yè)進行合作”,平博士說。他指出,回顧過去幾十年的DRAM發(fā)展,證明IDM是發(fā)展DRAM的必然選擇,而這正是長鑫存儲從一開始建立就堅持的。

-

DRAM

+關(guān)注

關(guān)注

40文章

2326瀏覽量

183868 -

DDR4

+關(guān)注

關(guān)注

12文章

322瀏覽量

40960 -

長鑫存儲

+關(guān)注

關(guān)注

2文章

38瀏覽量

9126

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電投資60億美元新建兩座封裝工廠

關(guān)于RISC-V學(xué)習(xí)路線圖推薦

未來10年智能傳感器怎么發(fā)展?美國發(fā)布最新MEMS路線圖

三星暫停兩大晶圓廠建設(shè)計劃

塔塔電子計劃在印度再建兩座晶圓廠

為企業(yè)先進制造工藝,中國臺灣新建兩座12英寸晶圓廠

英特爾公司加大俄亥俄州兩座晶圓廠投資額至280億

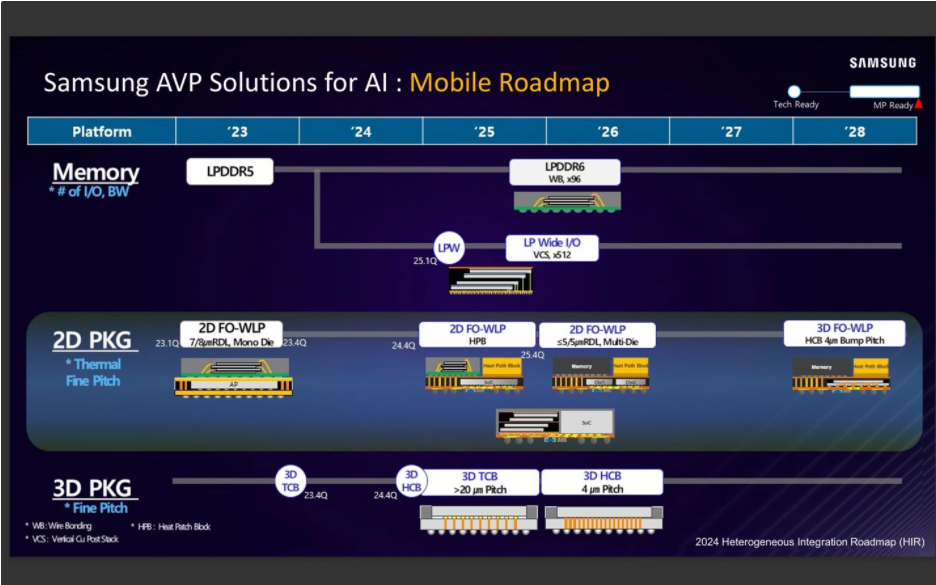

三星電子公布2024年異構(gòu)集成路線圖,LP Wide I/O移動內(nèi)存即將面世

鎧俠瞄準2027年:挑戰(zhàn)1000層堆疊的3D NAND閃存新高度

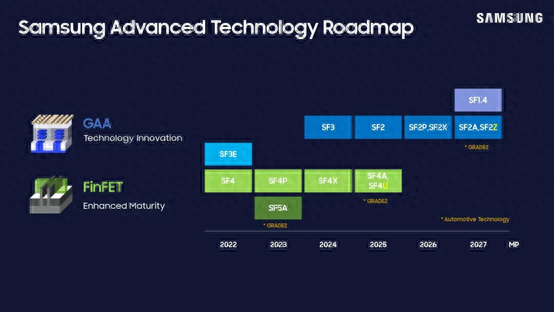

三星公布最新工藝路線圖

云計算公司CoreWeave將在英國開設(shè)兩座數(shù)據(jù)中心

事關(guān)衛(wèi)星物聯(lián)網(wǎng)!LoRaWAN 2027 發(fā)展路線圖重磅公布

公布最新技術(shù)路線圖!長鑫存儲計劃再建兩座 DRAM 晶圓廠

公布最新技術(shù)路線圖!長鑫存儲計劃再建兩座 DRAM 晶圓廠

評論