周期約束理論

首先來看什么是時序約束,泛泛來說,就是我們告訴軟件(Vivado、ISE等)從哪個pin輸入信號,輸入信號要延遲多長時間,時鐘周期是多少,讓軟件PAR(Place and Route)后的電路能夠滿足我們的要求。因此如果我們不加時序約束,軟件是無法得知我們的時鐘周期是多少,PAR后的結果是不會提示時序警告的。

周期約束就是告訴軟件我們的時鐘周期是多少,讓它PAR后要保證在這樣的時鐘周期內時序不違規。大多數的約束都是周期約束,因為時序約束約的最多是時鐘。

在講具體的時序約束前,我們先介紹兩個概念,在下面的講解中,會多次用到:

? 發起端/發起寄存器/發起時鐘/發起沿:指的是產生數據的源端

? 接收端/接收寄存器/捕獲時鐘/捕獲沿:指的是接收數據的目的端

建立/保持時間

講時序約束,這兩個概念要首先介紹,因為我們做時序約束其實就是為了滿足建立/保持時間。

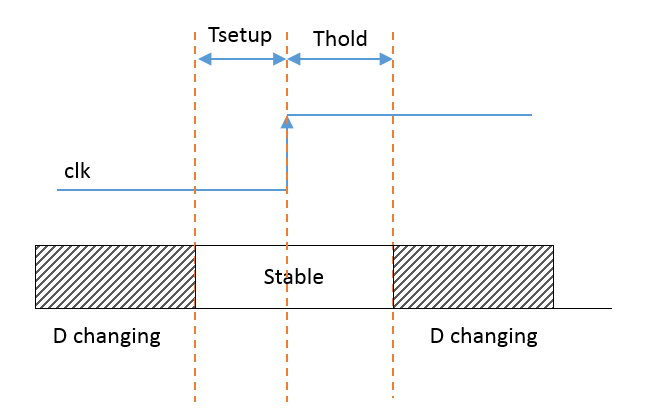

對于DFF的輸入而言,

? 在clk上升沿到來之前,數據提前一個最小時間量“預先準備好”,這個最小時間量就是建立時間;

? 在clk上升沿來之后,數據必須保持一個最小時間量“不能變化”,這個最小時間量就是保持時間。

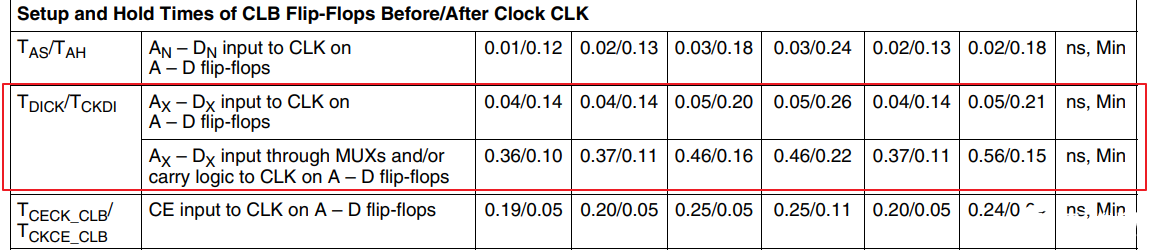

建立和保持時間是由器件特性決定了,當我們決定了使用哪個FPGA,就意味著建立和保持時間也就確定了。Xilinx FPGA的setup time基本都在0.04ns的量級,hold time基本在0.2ns的量級,不同器件會有所差異,具體可以查對應器件的DC and AC Switching Characteristics,下圖列出K7系列的建立保持時間。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605999 -

寄存器

+關注

關注

31文章

5363瀏覽量

121161

發布評論請先 登錄

相關推薦

FPGA實戰演練邏輯篇57:VGA驅動接口時序設計之4建立和保持時間分析

FPGA實戰演練邏輯篇59:VGA驅動接口時序設計之6建立和保持時間約束

VGA驅動接口時序設計數據的建立時間和保持時間

FPGA中的時序約束設計

基于FPGA與ad9252的時序約束高速解串設計

FPGA時序約束的建立和保持時間方法

FPGA時序約束的建立和保持時間方法

評論