CY7C68013A概述

USB接口有著速度快,成本低的優點,在現代計算機上已經成為了必備接口。USB2.0 HIGH-SPEED接口理論速度為480Mbit/S,實際使用帶寬在200M以上,在一些對可靠性以及實時性要求不是特別高的場合,USB簡單易用開發容易的特點使得其成為最佳的通訊接口選擇。賽普拉斯 EZ-USB?FX2LP? (CY7C68013A/14A)是高度集成、低功耗 USB 2.0 的微控制器。其接口速率可以達到96Mbytes/s,且成本僅僅十多元RMB。

CY7C68013A(FX2LP)同FPGA連接

我們在一些定制設備中使用了USB接口,現在市場上最主流的USB外設接口芯片為Cypress公司的CY7C68013A,為了實現高帶寬的通訊,CY7C68013需要工作在GPIF或者SLAVE FIFO模式,初學者往往對這兩種模式不是很清楚,結合我們已有的經驗,我們對兩種模式做一下簡要的說明:

GPIF模式適合CY7C68013主動同外部芯片通訊,GPIF通過幾個控制信號來實現狀態機的轉換,進而產生不同的時序。在外接SRAM、CMOS SENSOR、CPU、DSP等場合可以使用這個模式,其中DSP、CPU工作在從模式;

SLAVE FIFO模式適合同FPGA等自身可以跑狀態機的芯片配合使用。

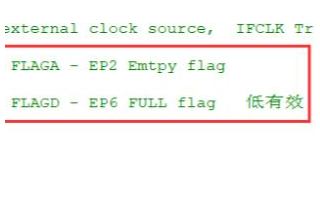

在利用CY7C68013同FPGA通訊的時候,一般使用SLAVE FIFO模式。EZ-USB_TRM2中第9章即是詳細講述SLAVE FIFO模式的。在CY7C68013中一共有4個端點,每一個端點都可以收或者發,對應的SLAVE FIFO有2條地址線用來選擇相應的端點緩沖區。SLAVE FIFO一個很重要的設置就是時鐘設置,其可以工作異步或者同步模式,在實際使用時,推薦同步模式,為了降低成本,可以使用CY7C68013自身產生的48Mhz時鐘,詳細的設置說明可以看Fig.9-6。SLAVE FIFO有4個標志引腳用來指示FIFO狀態(空、半滿、滿、自定義等),在FPGA中寫狀態機的時候需要用到這幾個引腳,特別注意的是FLAGD引腳可以用作SLAVE FIFO的片選,當總線上有不止一個設備的時候需要用到這個功能,其他時候可以不考慮。其他的引腳和標準的FIFO沒有什么特別,大家一看就可以明白。利用51程序將CY7C68013初始化好后,計算機同FPGA的通訊即可以打通。如果使用了多個端點,在FPGA上就要注意有一個有效的調度算法,以免某一個端點緩沖區內的數據遲遲不取出來導致通訊出錯。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

接口

+關注

關注

33文章

8691瀏覽量

151911 -

usb

+關注

關注

60文章

7980瀏覽量

266071

發布評論請先 登錄

相關推薦

CY7C68013A USB Board

fx2lp(cy7c68013A)與圖像傳感器接口相同的固件適用于fx2lp18嗎?

fx2lp slavefifo將LV和FV連接到RDY1和RDY0是強制的嗎?

使用CY7C68013A-56LTXC無法進行MPEG TS捕獲

使用CyUSB.dll和LabVIEW訪問FX2LP失敗

如何從bulkloop失敗示例開始做新的CY7C68013A?

CY7C68013A開發板使用說明

CY7C68013A中文資料

基于CY7C68013A的FPGA配置和通信接口設計

基于CY7C68013A芯片的USB鍵盤的設計

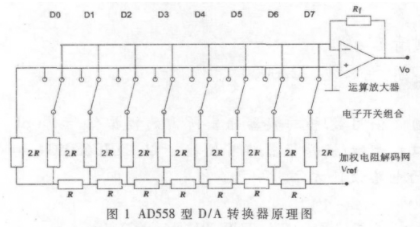

采用CY7C68013A和AD558芯片實現數/模轉換器輸出電路的設計

CY7C68013A FX2LP與FPGA連接的方法

CY7C68013A FX2LP與FPGA連接的方法

評論