我們生活在模擬信號(hào)的世界中,但在數(shù)字電子設(shè)備中,只有兩種狀態(tài):開(kāi)或關(guān)。使用這兩種狀態(tài),設(shè)備可以編碼,傳輸和控制大量數(shù)據(jù)。

從廣義上講,邏輯電平描述信號(hào)可以具有的任何特定的離散狀態(tài)。在數(shù)字電子學(xué)中,我們通常將研究限于兩個(gè)邏輯狀態(tài):二進(jìn)制1和二進(jìn)制0。

一、什么是邏輯電平?

邏輯電平是特定電壓或可以存在信號(hào)的狀態(tài),通常為“0/1” 或 “開(kāi)/關(guān)”或 “ON/OFF”或 “LOW / HIGH”等。

數(shù)字電子產(chǎn)品依靠二進(jìn)制邏輯來(lái)存儲(chǔ),處理和傳輸數(shù)據(jù)或信息,我們通常將數(shù)字電路中的兩個(gè)狀態(tài)稱為“開(kāi)”或“關(guān)”。

信號(hào)的強(qiáng)度通常由其電壓電平來(lái)描述,如何定義邏輯0(低)或邏輯1(高)?芯片制造商通常會(huì)在其規(guī)格中對(duì)其進(jìn)行定義,最常見(jiàn)的標(biāo)準(zhǔn)是TTL或晶體管邏輯。

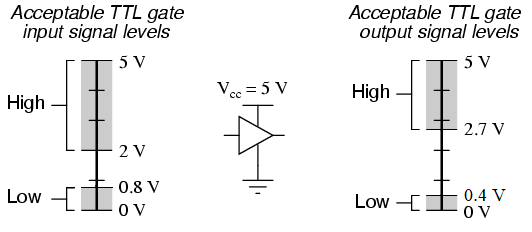

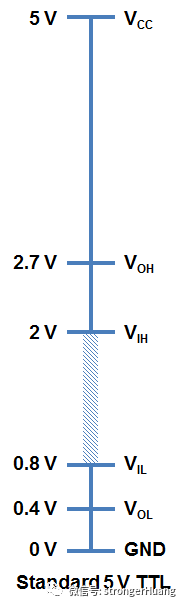

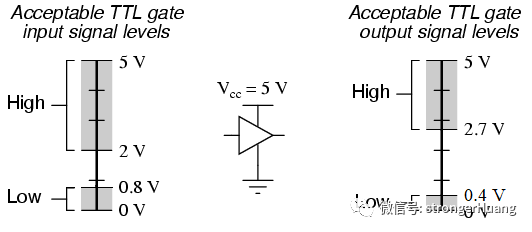

二、TTL邏輯電平TTL:Transistor-Transistor Logic,晶體管-晶體管邏輯。 我們使用的大多數(shù)系統(tǒng)都依賴于3.3V或5 V TTL電平,一般依靠雙極晶體管構(gòu)建的電路來(lái)實(shí)現(xiàn)切換并保持邏輯狀態(tài)。 在數(shù)字電路中,所謂“門(mén)”就是只能實(shí)現(xiàn)基本邏輯關(guān)系的電路。最基本的邏輯關(guān)系是與、或、非,最基本的邏輯門(mén)是與門(mén)、或門(mén)和非門(mén)。 邏輯門(mén)可以用電阻、電容、二極管、三極管等分立原件構(gòu)成,成為分立元件門(mén)。也可以將門(mén)電路的所有器件及連接導(dǎo)線制作在同一塊半導(dǎo)體基片上,構(gòu)成集成邏輯門(mén)電路。 TTL有許多閾值電壓電平需要知道,以5V TTL電平為例:

VOH:TTL設(shè)備將為HIGH信號(hào)提供的最小輸出電壓電平。

VIH:最小輸入電壓電平被視為高電平。

VOL:設(shè)備將為L(zhǎng)OW信號(hào)提供的最大輸出電壓電平。

VIL:最大輸入電壓電平仍被視為L(zhǎng)OW。

你會(huì)發(fā)現(xiàn),最小輸出HIGH電壓(VOH)為2.7V。基本上,這意味著驅(qū)動(dòng)HIGH的設(shè)備的輸出電壓將始終至少為2.7V。最小輸入HIGH電壓(V IH)為2 V,或者基本上任何至少2 V的電壓都將作為邏輯1(HIGH)讀入TTL設(shè)備。

你還會(huì)發(fā)現(xiàn),一個(gè)設(shè)備的輸出與另一設(shè)備的輸入之間有0.7 V的緩沖,有時(shí)稱為噪聲余量。

最大輸出低電壓(VOL)為0.4V,這意味著試圖發(fā)出邏輯0的設(shè)備將始終低于0.4V。

最大輸入低電壓(VIL)為0.8V。因此,任何讀入器件時(shí),低于0.8 V的輸入信號(hào)仍將被視為邏輯0(LOW)。

如果電壓在0.8 V和2 V之間,會(huì)發(fā)生什么?

答案:該電壓范圍是不確定的,無(wú)效狀態(tài),通常稱為浮動(dòng)狀態(tài)。如果設(shè)備上的輸出引腳在該范圍內(nèi)“浮動(dòng)”,則無(wú)法確定信號(hào)的結(jié)果。它可能在HIGH和LOW之間任意跳動(dòng)。

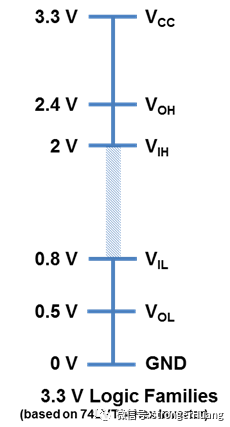

三、3.3 V CMOS邏輯電平

隨著技術(shù)的進(jìn)步,邏輯電壓越來(lái)越低,3.3V,1.8V,甚至1.2V。

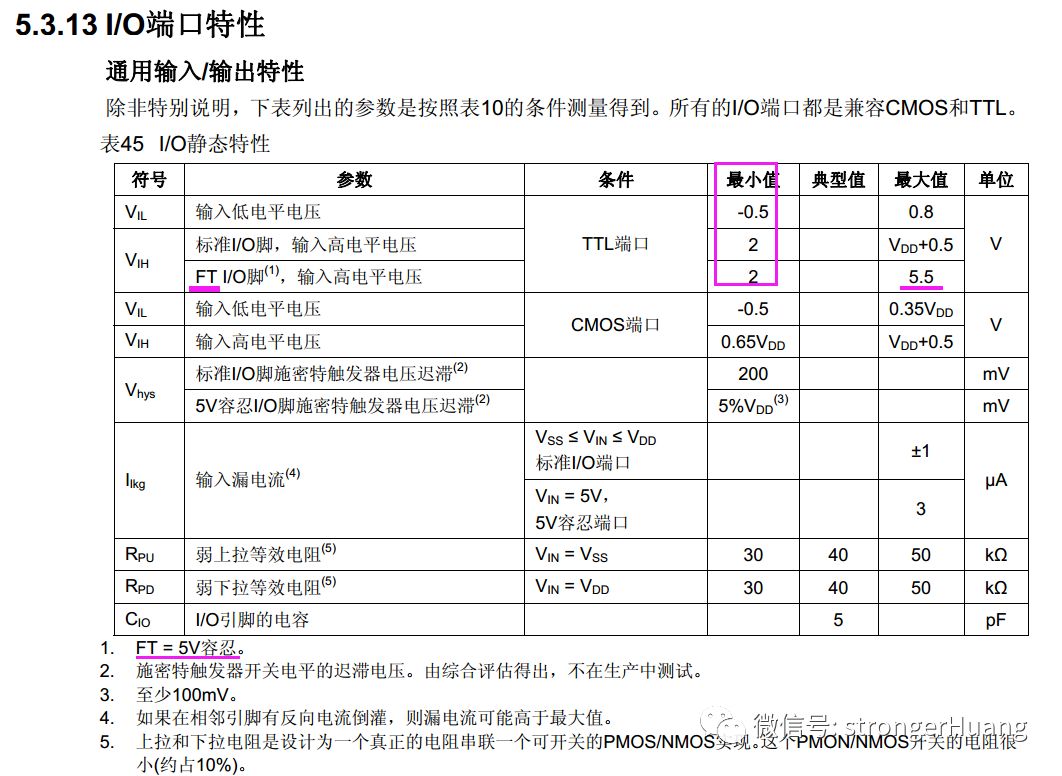

目前市面上大部分MCU的電壓都是3.3V,拿STM32來(lái)說(shuō),基準(zhǔn)電壓都是3.3V(當(dāng)然,支持5V輸入)。

之前寫(xiě)過(guò)一篇《STM32數(shù)據(jù)手冊(cè)中那些重要內(nèi)容》講過(guò)手冊(cè)中會(huì)指出邏輯電平的電壓。

四、邏輯電平轉(zhuǎn)換

目前常見(jiàn)的邏輯電平5V和3.3V居多,但如果使用兩種電平信號(hào)進(jìn)行通信,有些芯片能兼容,就不需要轉(zhuǎn)換。

但有些芯片不兼容,比如:3.3V器件,如果超過(guò)3.6V就會(huì)永久損壞,此時(shí)就需要轉(zhuǎn)換。

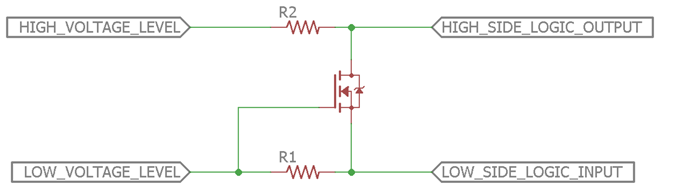

5V與 3.3V之間轉(zhuǎn)換的方式有很多種:三極管電路、光耦電路、集成IC轉(zhuǎn)換等。

1.三極管

2.光耦

3.集成IC轉(zhuǎn)換

-

三極管

+關(guān)注

關(guān)注

143文章

3622瀏覽量

122397 -

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42709 -

光耦電路

+關(guān)注

關(guān)注

0文章

12瀏覽量

7696

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TTL電平與信號(hào)降噪技術(shù)的區(qū)別

TTL電平與高電平信號(hào)的轉(zhuǎn)換

TTL電平的傳輸距離限制

TTL電平的工作原理詳解

TTL電平在數(shù)字電路中的作用

TTL電平標(biāo)準(zhǔn)的介紹與解析

TTL電平與CMOS電平的區(qū)別是什么

邏輯異或的定義和應(yīng)用 邏輯異或與邏輯與的區(qū)別

高電平輸入和低電平輸入是什么意思

邏輯電平輸出是什么意思

汽車(chē)類單電源單緩沖器邏輯電平轉(zhuǎn)換器SN74LV1T34-Q1數(shù)據(jù)表

靜電平衡導(dǎo)體內(nèi)部電勢(shì)為0嗎

cmos電平與ttl電平如何轉(zhuǎn)換 怎么判斷ttl電路高低電平

N溝道40 V,2.1 mOhm,180 A邏輯電平MOSFET PSMN2R0-40YLB數(shù)據(jù)手冊(cè)

雙向邏輯電平轉(zhuǎn)換器電路圖分享

邏輯電平0與1的世界

邏輯電平0與1的世界

評(píng)論