引言

在TDM over IP 和V5 VoIP Gateway等PSTN(公共交換電話網)應用中都涉及E1的選型及其接口的設計,IDT82P芯片的軟件可編程性能較好,模擬接口較穩定,內部可提供多種時鐘跟蹤模式。同時芯片內部提供豐富信令功能,可提供CAS信令的提取,提取內容輸出方式靈活。CPU通過Bus控制對E1模塊進行配置以及實現各種告警的監控和管理。

IDT82P

IDT82PIDT公司提供的一款8路E1/T1/J1接入,比原來的4路可直接節約1片,從成本和空間上的節約都做到了,此芯片采用雙電源3.3V和1.8V供電,功耗0.8W。另外不同于其他一些E1芯片的是它可用內部編程調節阻抗,以滿足不同的線路阻抗接入。線路側支持多種編碼, AMI/B8ZS(T1/J1)AMI/HDB3(E1),接收側靈敏度高,可達-36dB@772Hz和-43dB@1024Hz 。線路側支持多種幀格式(Super Frame, Extended Super FrAME)。信令支持格式HDLC和SS7。豐富的告警和性能處理。系統側可由線路側經幀處理單獨一路送出去,也可4路合成一路送出去。另外在系統側,可專門提供信令通道。控制接口可支持SPI和Intel/Motorola 多種管理接口。

IDT82P主要接口分為四類:業務接口、MPI接口、時鐘接口和調試接口(圖1)。

圖1 IDT82P2288功能

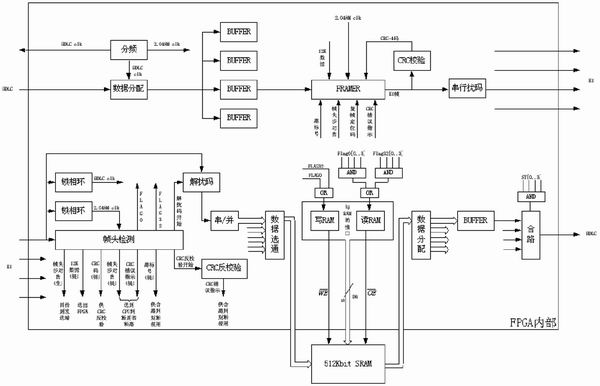

業務接口分為系統側和線路側。線路側為模擬側,和E1線路方向的信號對接;系統側為數字側,和TSI芯片的HW對接。從PSTN送來的E1/T1模擬信號進入芯片,經過增益調整后,由數據時鐘恢復單元恢復出數據,并提取出來線路上的時鐘信息后,解碼送入成幀器中成幀。如果設置了接收彈存,則成幀后的數據被放入彈存中。接收彈存的大小可以由軟件進行設置,最大容量為2幀,也可以將其關閉。在一過程中,抖動衰減模塊消除了模擬線上的部分抖動。同時性能管理模塊也會將產生的告警和其他統計信息上報到管理模塊中的相應寄存器中。系統側根據接收側的幀同步信號以及相應寄存器所設置的TS0偏移位置,從彈存中取出數據,送到接收HW上。發送方向處理過程和接收過程類似。在線模式下,線路側接收靈敏度E1/T1模式分別可達-43dB/-36dB;短線模式下可提供-10dB的靈敏度。線路側可支持三種電平接口,通過軟件編程設定。

IDT82P系統側HW可以支持復用和非復用兩種模式。復用模式將4條HW通過字節交錯方式,合并到1條8.192MHW總線上。使用復用模式有利于減少板間連線。TS0的位置由系統側幀同步信號以及接收發送TS0偏移寄存器共同確定。

芯片內部有性能管理模塊,可監控信號丟失、幀失步、AIS等多種告警。各種告警門限可以通過軟件設定。

IDT82P芯片的抖動特性可以滿足ITU、ETSI等組織相關標準對相應數的要求。

每個E1通道配備3個HDLC控制器,可提供標準的HDLC成幀,也可提供SS7這類非標準信令的成幀。提取出來的信令內容放置在芯片內部的FIFO中,由CPU定時取出。

MPI接口是主控制器對IDT82P進行配置、管理、監控的通道,是一異步、慢速的總線。支持地址鎖存以及非鎖存兩種尋址模式。可方便的和單片機、通用CPU對接。支持SPI和Intel或Motorala兩種CPU類型,數據寬度可設為8位。

時鐘接口包括線路時鐘和本地時鐘信號。IDT82P需要外部提供一個2.048M,32ppm以內的時鐘,普通晶振即可滿足要求。IDT82P可提供豐富的時鐘應用模式,作為應用于接入網位置的模塊,其線路側發送端使用系統側時鐘,接收端使用線路恢復時鐘。

IDT82P提供標準的JTAG口作為調試使用。提供本地環回、遠端環回以及凈荷環回三種環回模式。可提供任意時隙的PRBS測試碼流插入。調試手段豐富。

基于IDT82P E1 接口設計

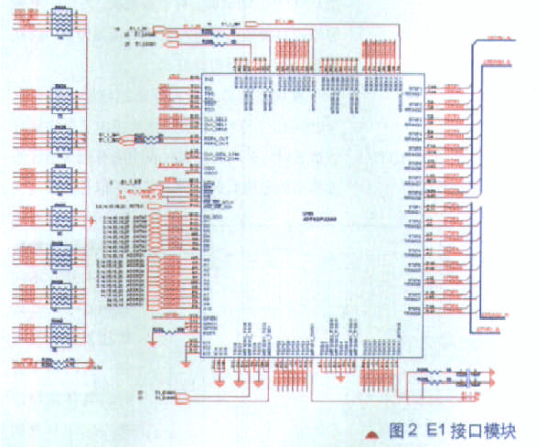

本模塊選用TDI公司的IDT82P,該芯片每片支持8路E1/T1/J1接口。軟件可編程性能較好,其他E1/T1/J1的類型轉換可以只通過軟件完成設定。E1接口模塊使用2片IDT82P,實現16路E1的接入。設計電路如圖2所示。

圖2 E1接口模塊

IDT82P線路側和外部E1線纜通過專用變壓器進行隔離。在變壓器靠近線纜側放置高壓防雷保護管,作為一級防護;變壓器靠近芯片端放置低壓TVS管,作為二級防護。線路側使用三進制編碼,默認碼型為HDB3,也可以通過軟件設定為AMI碼。

系統側使用復用模式,不同E/T1通道的時隙通過字節交錯的方式,復用成8.192Mbit/s HW。系統側時鐘和幀同步信號由FPGA根據系統時鐘提供。

信令的HDLC成幀不使用IDT82P內部的HDLC控制器。信令的HDLC成幀以及進一步處理均由CPU完成。

IDT82P的MPI口通過相應配置引腳的上下拉電阻,配置成Motorola 模式,數據寬度為8位,地址線10根。 通過MPI接口,CPU可以對E1模塊進行配置,以及各種告警的監控和管理。

2片IDT82P共恢復出來的16路線路接收時鐘送到FPGA中,在FPGA中作進一步處理。

本模塊采用單電源3.3V和1.8V供電。

JTAG口引到2×5的插座上,可供需要時使用。

測試結果

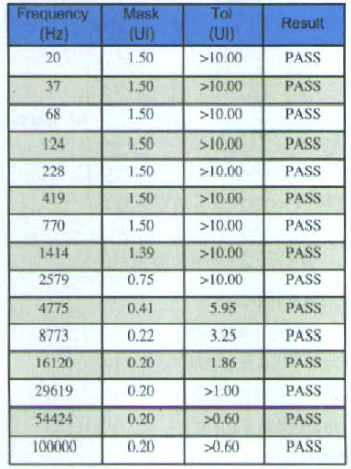

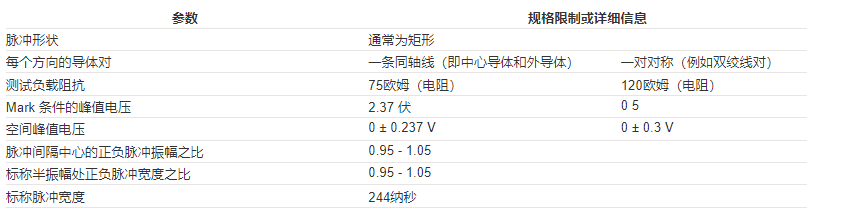

表1是我們在實際工程應用中所測得的E1傳輸抖動值。

經過高低溫測試其抖動均滿足G.823抖動要求,加之其高低溫下24小時誤碼為0,其它指標也很好,實踐證明它具有較好的性能和穩定性。

結語

本文主要分析了IDT82P的工作原理和其在VoIP中E1接口的應用實例,并且得出了相當理想的抖動測量值,且設計較易,成本不高。充分顯示其實際應用價值。但是它也有不足之處,就是在進行T1模式設計時,需外加PLL電路,加之隨著業務量的增加,對芯片通道數的要求也不斷提高。

責任編輯:gt

-

芯片

+關注

關注

456文章

51170瀏覽量

427225 -

阻抗

+關注

關注

17文章

961瀏覽量

46254 -

軟件

+關注

關注

69文章

5009瀏覽量

88066

發布評論請先 登錄

相關推薦

E1接口音頻編解碼器(立體聲/AES數字)

怎么判斷一個產品有沒有E1接口或者說E1接口是什么樣的?

E1成解幀器的設計

基于FPGA的HDLC轉E1傳輸控制器的實現

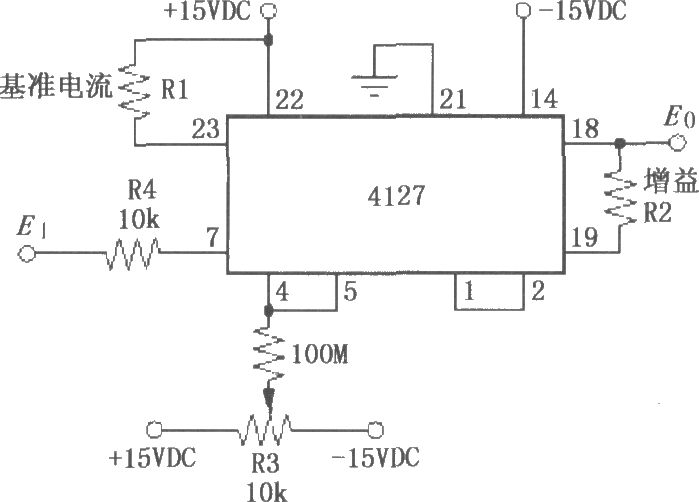

輸入電壓E1為負時的對數變換功能電路(對數放大器4127)

多路接口與E1協議轉換器設計

基于FPGA的以太網與E1協議轉換器的實現

IDT82P芯片的功能特點及如何實現E1模塊的接口設計

IDT82P芯片的功能特點及如何實現E1模塊的接口設計

評論