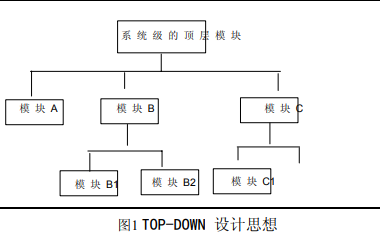

基于FPGA的SOC在嵌入式系統(tǒng)應(yīng)用越來越廣了,往往一個(gè)復(fù)雜系統(tǒng)使用一個(gè)單芯片基于FPGA的SOC就搞定了。比較流行的方案主要有Altera/xilinx兩家的方案。要用這樣的方案,首要需要掌握的是硬件描述語(yǔ)言。最為流行的硬件描述語(yǔ)言有兩種Verilog HDL/VHDL,均為IEEE標(biāo)準(zhǔn)。Verilog HDL具有C語(yǔ)言基礎(chǔ)就很容易上手,而VHDL語(yǔ)言則需要Ada編程基礎(chǔ)。另外Verilog HDL語(yǔ)言具有大量成熟的模塊,從某種角度說Verilog HDL更具生命力。 本文整理了一下Verilog HDL語(yǔ)言技術(shù)要點(diǎn),并分享給大家。如發(fā)現(xiàn)有錯(cuò)誤,歡迎留言指正。

Verilog HDL能干啥?

Verilog HDL的特點(diǎn):

可描述順序執(zhí)行或并行執(zhí)行的程序結(jié)構(gòu)

用延遲表達(dá)式或事件表達(dá)式來明確地控制過程的啟動(dòng)時(shí)間

通過命令的事件來觸發(fā)其他過程的激活行為或停止行為

提供了條件/循環(huán)等邏輯控制結(jié)構(gòu)

提供了可帶參數(shù)且非零延續(xù)時(shí)間的任務(wù)程序機(jī)構(gòu)

提供了用于建立表達(dá)式的算術(shù)運(yùn)算符、邏輯運(yùn)算符和位運(yùn)算符

實(shí)現(xiàn)了完整的表示組合邏輯基本元件的原語(yǔ)

提供了雙向通路和電阻器的描述

可建立MOS器件的電荷分享和衰減模型

可通過結(jié)構(gòu)性語(yǔ)句精確地建立信號(hào)模型

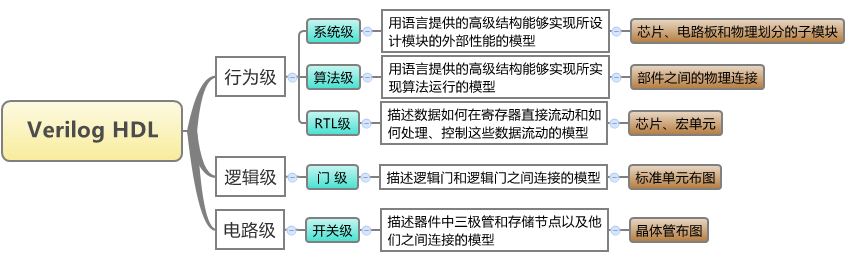

在學(xué)習(xí)Verilog HDL之前,先明確一下FPGA的設(shè)計(jì)抽象層次:

基本程序結(jié)構(gòu)

modulemodule_name(port_list) //聲明各種變量、信號(hào) reg//寄存器 wire//線網(wǎng) parameter//參數(shù) input//輸入信號(hào) output//輸出信號(hào) inout//輸入輸出信號(hào) function//函數(shù) task//任務(wù) .... //程序代碼 initialassignment alwaysassignment moduleassignment gateassignment UDPassignment continousassignment endmodule

啟示:描述的是模塊,其本質(zhì)是數(shù)字電路:

組合邏輯電路模塊:組合邏輯電路的特點(diǎn)是輸入的變化直接反映了輸出的變化,其輸出的狀態(tài)僅取決于輸入的當(dāng)前的狀態(tài),與輸入、輸出的原始狀態(tài)無關(guān)。

時(shí)序邏輯電路模塊:時(shí)序電路具有記憶功能。時(shí)序電路的特點(diǎn)是:輸出不僅取決于當(dāng)時(shí)的輸入值,而且還與電路過去的狀態(tài)有關(guān)。時(shí)序邏輯電路又稱時(shí)序電路,主要由存儲(chǔ)電路和組合邏輯電路兩部分組成。

數(shù)據(jù)類型及運(yùn)算符

變量名

變量名類似C語(yǔ)言,以一組字母、數(shù)字、下劃線和$符號(hào)的組合,且首字符須為字母或者下劃線。如

inputctrl_1;

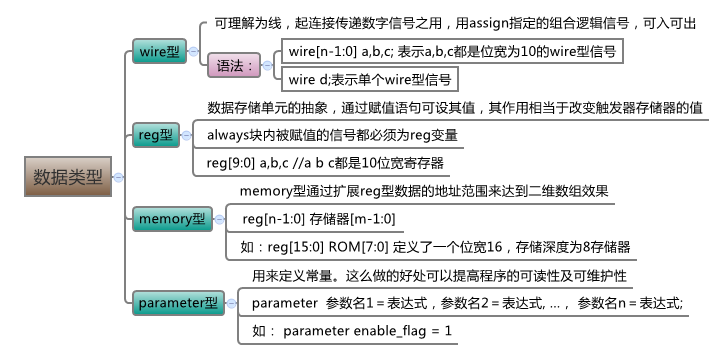

數(shù)據(jù)類型

將四種基本數(shù)據(jù)類型整理成一張導(dǎo)圖:

其中須注意的是,對(duì)于memory型存儲(chǔ)單元進(jìn)行讀寫,須指定地址,如:

reg[15:0]addr;//定義addr為16位位寬的存儲(chǔ)器變量 addr=1;//ok regaddr[15:0];//定義addr為1位位寬的16個(gè)存儲(chǔ)器變量 addr=1;//錯(cuò)誤 addr[0]=1;//正確 //又如: reg[15:0]addr[3:1];//定義3個(gè)位寬為16位存儲(chǔ)器 addr[1]=16'h0//16'指定位寬,h表示16進(jìn)制,0 addr[2]=16'b011//b表示二進(jìn)制

對(duì)于parameter變量的實(shí)用價(jià)值可讀性比較好理解,那么可維護(hù)性怎么體現(xiàn)呢?

熟悉C語(yǔ)言編程的,聯(lián)想一下宏,如果宏變了,有宏的地方全替換,這里parameter變量作用類似,如:

moduleDecode(A,F); parameterWidth=1,Polarity=1; …………… endmodule moduleTop; wire[3:0]A4; wire[4:0]A5; wire[15:0]F16; wire[31:0]F32; Decode#(4,0)D1(A4,F16); Decode#(5)D2(A5,F32); Endmodule

常量

parameter定義常量,那么對(duì)于常數(shù),整型常量即整常數(shù)有以下四種進(jìn)制表示形式:

二進(jìn)制整數(shù)(b或B)

十進(jìn)制整數(shù)(d或D)

十六進(jìn)制整數(shù)(h或H)

八進(jìn)制整數(shù)(o或O)

數(shù)字表達(dá)方式有以下三種:

<位寬><進(jìn)制><數(shù)字>這是一種全面的描述方式。

<進(jìn)制><數(shù)字>在這種描述方式中,數(shù)字的位寬采用缺省位寬(這由具體的機(jī)器系統(tǒng)決定,但至少32位)。

<數(shù)字>在這種描述方式中,采用缺省進(jìn)制十進(jìn)制。

x和z值

在數(shù)字電路中,x代表不定值,z代表高阻值。不確定是啥?高阻又是啥?記住verilog描述的數(shù)字電路,那么對(duì)于一個(gè)模塊的I/O就有可能是高阻,或者狀態(tài)不確定。

負(fù)數(shù):

一個(gè)數(shù)字可以被定義為負(fù)數(shù),只需在位寬表達(dá)式前加一個(gè)減號(hào),減號(hào)必須寫在數(shù)字定義表達(dá)式的最前面。注意減號(hào)不可以放在位寬和進(jìn)制之間也不可以放在進(jìn)制和具體的數(shù)之間。

-8'd7//-號(hào)直接放在最前面 8'd-7//這樣則不正確

實(shí)數(shù)

實(shí)數(shù)可用十進(jìn)制方式表述或者科學(xué)計(jì)數(shù)法描述,如:

//十進(jìn)制表示 1.0 20.234 //科學(xué)計(jì)數(shù)法表示 6e-4

模塊端口

input:模塊從外界讀取數(shù)據(jù)的接口,在模塊內(nèi)可讀不可寫

output:模塊向外部輸出數(shù)據(jù)的接口,模塊內(nèi)部可寫不可讀

inout:可讀寫數(shù)據(jù),數(shù)據(jù)雙向流動(dòng)。

學(xué)習(xí)硬件描述語(yǔ)言,一定要時(shí)刻記住,這是描述的是電路,風(fēng)格類C,但不是C!

表達(dá)式及運(yùn)算符

和C語(yǔ)言類似,運(yùn)算符也有三種:

單目運(yùn)算符(unary operator):可以帶一個(gè)操作數(shù),操作數(shù)放在運(yùn)算符的右邊。

二目運(yùn)算符(binary operator):可以帶二個(gè)操作數(shù),操作數(shù)放在運(yùn)算符的兩邊。

三目運(yùn)算符(ternary operator):可以帶三個(gè)操作,這三個(gè)操作數(shù)用三目運(yùn)算符分隔開。

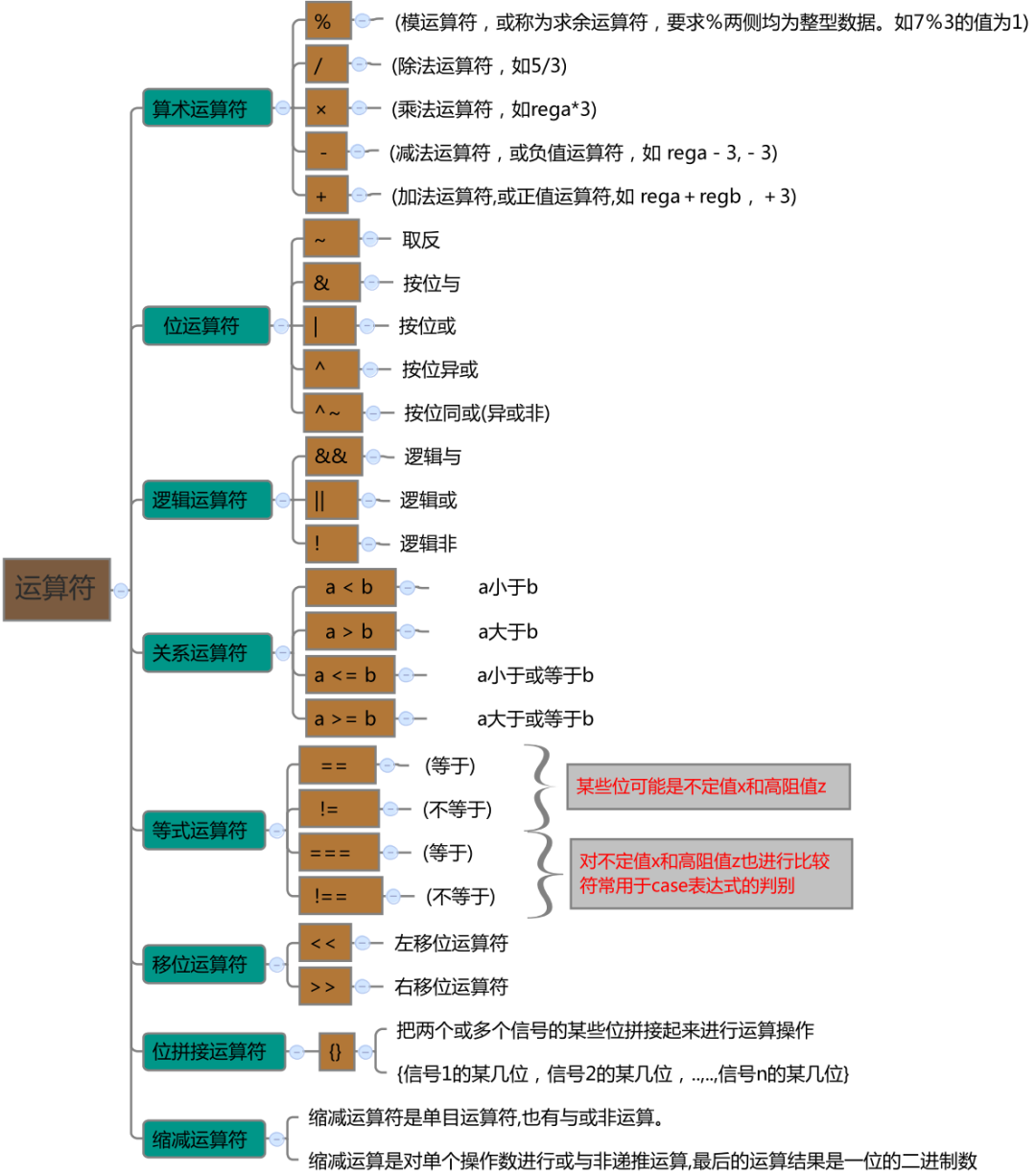

對(duì)于運(yùn)算符,整理了一張導(dǎo)圖:

大部分與C語(yǔ)言類似,除了等式運(yùn)算符、位拼接運(yùn)算符、縮減運(yùn)算符,這里放點(diǎn)例子方便理解:

//縮減運(yùn)算符 reg[3:0]B; regC; C=&B; //相當(dāng)于: C=((B[0]&B[1])&B[2])&B[3];//位拼接運(yùn)算符 {a,b[3:0],w,3’b101} //相當(dāng)于: {a,b[3],b[2],b[1],b[0],w,1’b1,1’b0,1’b1}

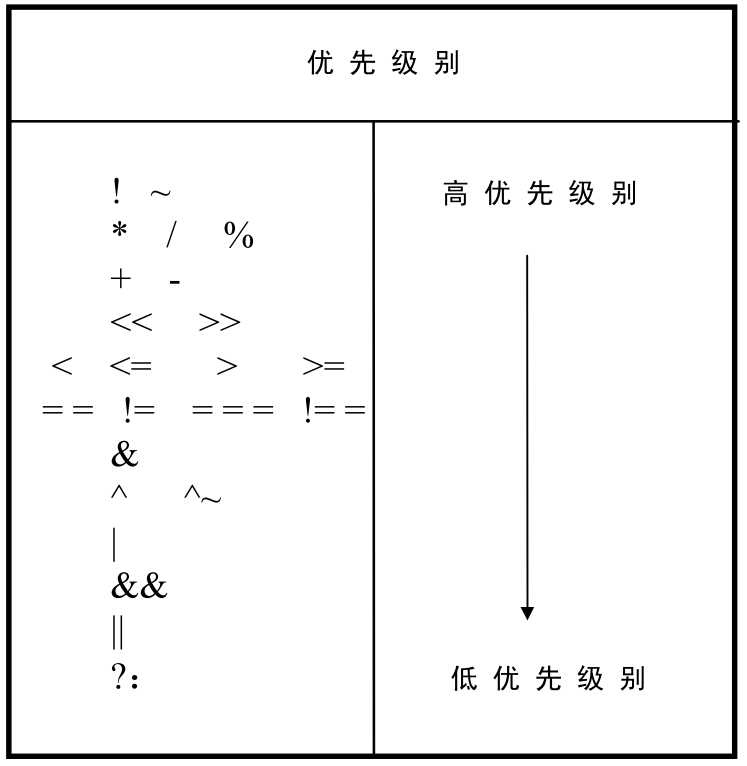

運(yùn)算符優(yōu)先級(jí):

賦值語(yǔ)句

非阻塞(Non_Blocking)賦值方式, 如 b <= a; 加粗是非阻塞的含義

塊結(jié)束后才完成賦值操作。

b的值并不是立刻就改變的。

這是一種比較常用的賦值方法。

阻塞(Blocking)賦值方式,如 b = a;

賦值語(yǔ)句執(zhí)行完后,塊才結(jié)束。

b的值在賦值語(yǔ)句執(zhí)行完后立刻就改變的。

可能會(huì)產(chǎn)生意想不到的結(jié)果。

塊語(yǔ)句

塊語(yǔ)句有兩種,一種是begin_end語(yǔ)句,通常用來標(biāo)識(shí)順序執(zhí)行的語(yǔ)句,用它來標(biāo)識(shí)的塊稱為順序塊。一種是fork_join語(yǔ)句,通常用來標(biāo)識(shí)并行執(zhí)行的語(yǔ)句,用它來標(biāo)識(shí)的塊稱為并行塊。

順序塊

塊內(nèi)的語(yǔ)句是按順序執(zhí)行的,即只有上面一條語(yǔ)句執(zhí)行完后下面的語(yǔ)句才能執(zhí)行。

每條語(yǔ)句的延遲時(shí)間是相對(duì)于前一條語(yǔ)句的仿真時(shí)間而言的。

直到最后一條語(yǔ)句執(zhí)行完,程序流程控制才跳出該語(yǔ)句塊。

begin 語(yǔ)句1; 語(yǔ)句2; ...... 語(yǔ)句n; end

并行塊

塊內(nèi)語(yǔ)句是同時(shí)執(zhí)行的,即程序流程控制一進(jìn)入到該并行塊,塊內(nèi)語(yǔ)句則開始同時(shí)并行地執(zhí)行。

塊內(nèi)每條語(yǔ)句的延遲時(shí)間是相對(duì)于程序流程控制進(jìn)入到塊內(nèi)時(shí)的仿真時(shí)間的。

延遲時(shí)間是用來給賦值語(yǔ)句提供執(zhí)行時(shí)序的。

當(dāng)按時(shí)間時(shí)序排序在最后的語(yǔ)句執(zhí)行完后或一個(gè)disable語(yǔ)句執(zhí)行時(shí),程序流程控制跳出該程序塊。

fork 語(yǔ)句1; 語(yǔ)句2; ....... 語(yǔ)句n; join

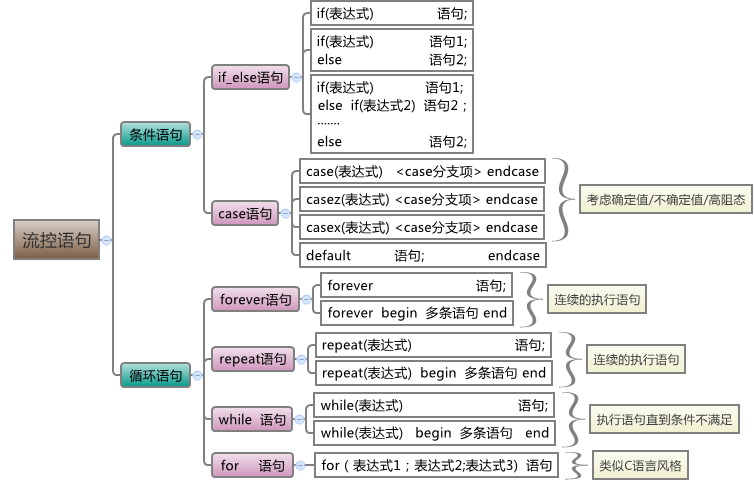

流控語(yǔ)句

流控語(yǔ)句風(fēng)格與C語(yǔ)言類似,僅僅需要注意的有下面幾點(diǎn):

if 語(yǔ)句別忘了考慮else的情況,如忘了處置則最終硬件會(huì)最終產(chǎn)生意想不到的后果

多條語(yǔ)句在條件內(nèi)部需要用begin/end對(duì)包起來。

case語(yǔ)句與C語(yǔ)言也有default分支,實(shí)際使用注意處置default分支

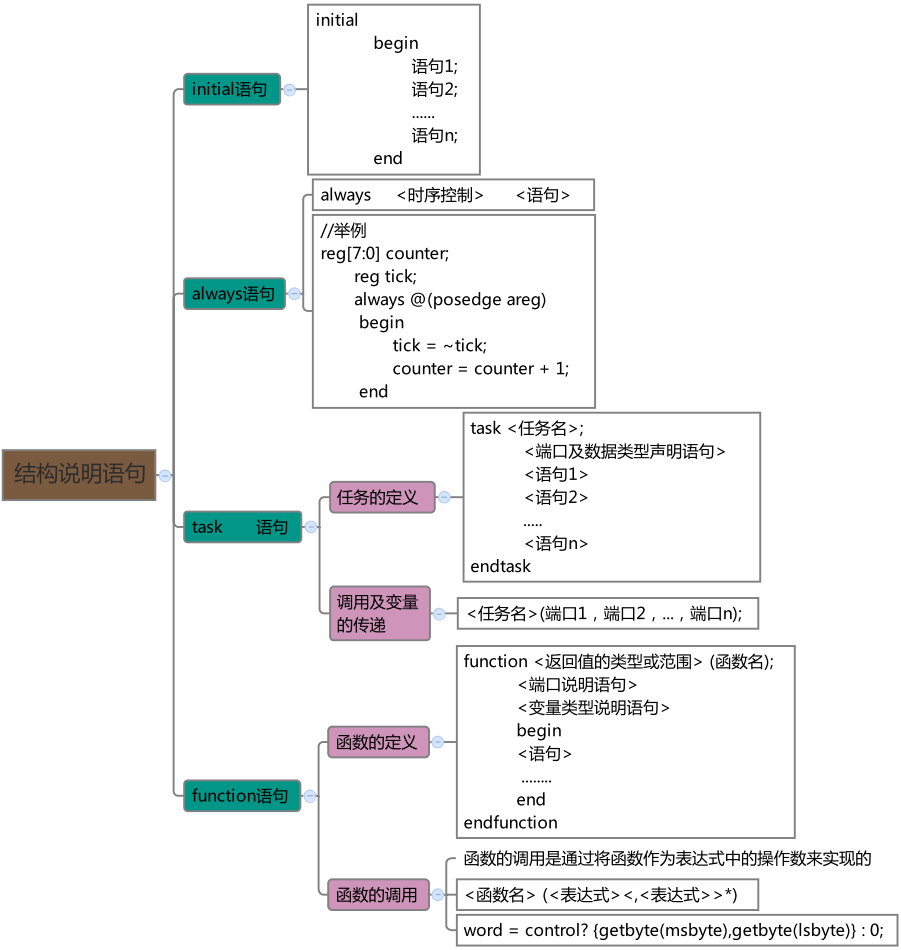

結(jié)構(gòu)說明語(yǔ)句

Verilog語(yǔ)言中的任何過程模塊都從屬于以下四種結(jié)構(gòu)的說明語(yǔ)句:

initial說明語(yǔ)句:只執(zhí)行一次

always說明語(yǔ)句 :是不斷地重復(fù)執(zhí)行

task說明語(yǔ)句

function說明語(yǔ)句

對(duì)于task/function的不同點(diǎn),使用時(shí)需要注意:

函數(shù)只能與主模塊共用同一個(gè)仿真時(shí)間單位,而任務(wù)可以定義自己的仿真時(shí)間單位。函數(shù)的定義不能包含有任何的時(shí)間控制語(yǔ)句,即任何用#、@、或wait來標(biāo)識(shí)的語(yǔ)句。

函數(shù)不能啟動(dòng)任務(wù),而任務(wù)能啟動(dòng)其它任務(wù)和函數(shù)。

函數(shù)至少要有一個(gè)輸入變量,而任務(wù)可以沒有或有多個(gè)任何類型的變量。

函數(shù)返回一個(gè)值,而任務(wù)則不返回值。

函數(shù)的目的是通過返回一個(gè)值來響應(yīng)輸入信號(hào)的值。任務(wù)卻能支持多種目的,能計(jì)算多個(gè)結(jié)果值,這些結(jié)果值只能通過被調(diào)用的任務(wù)的輸出或總線端口送出

在函數(shù)的定義中必須有一條賦值語(yǔ)句給函數(shù)中的一個(gè)內(nèi)部變量賦以函數(shù)的結(jié)果值,該內(nèi)部變量具有和函數(shù)名相同的名字。

系統(tǒng)函數(shù)和任務(wù)

在Verilog HDL語(yǔ)言中每個(gè)系統(tǒng)函數(shù)和任務(wù)前面都用一個(gè)標(biāo)識(shí)符$來加以確認(rèn),有這些系統(tǒng)函數(shù)和任務(wù)。

rtoi, setup, skew, setuphold, strobe, time, timefoemat, width, write, $recovery,

按字面意思理解,需要用到時(shí)查詢手冊(cè)即可。

編譯預(yù)處理

宏定義 `define

用法:

`define 標(biāo)識(shí)符(宏名) 字符串(宏內(nèi)容)

如:

//類似C宏替換 `definesignalhello

與C語(yǔ)言宏類似,除了關(guān)鍵字不一樣,也支持嵌套。組成宏內(nèi)容的字符串不能夠被以下的語(yǔ)句記號(hào)分隔開的,下面幾點(diǎn)需要注意:

注釋行

數(shù)字

字符串

確認(rèn)符

關(guān)鍵詞

雙目和三目字符運(yùn)算符

“文件包含”處理`include

用法:`include “文件名”

四點(diǎn)說明:

一個(gè)`include命令只能指定一個(gè)被包含的文件,如果要包含n個(gè)文件,要用n個(gè)`include命令。注意下面的寫法是非法的`include"aaa.v""bbb.v"

`include命令可以出現(xiàn)在Verilog HDL源程序的任何地方,被包含文件名可以是相對(duì)路徑名,也可以是絕對(duì)路徑名。例如:'include"parts/count.v"

可以將多個(gè)`include命令寫在一行,在`include命令行,只可以出空格和注釋行。

如果文件1包含文件2,而文件2要用到文件3的內(nèi)容,則可以在文件1用兩個(gè)`include命令分別包含文件2和文件3,而且文件3應(yīng)出現(xiàn)在文件2之前

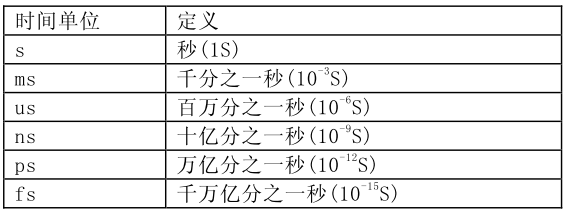

時(shí)間尺度 `timescale

`timescale命令用來說明跟在該命令后的模塊的時(shí)間單位和時(shí)間精度。使用`timescale命令可以在同一個(gè)設(shè)計(jì)里包含采用了不同的時(shí)間單位的模塊。用法:

`timescale<時(shí)間單位>/<時(shí)間精度>

//模塊中所有的時(shí)間值都表示是1ns的整數(shù)倍 //1ns/ps:1納秒/脈沖 `timescale1ns/1ps

注意:如果在同一個(gè)設(shè)計(jì)里,多個(gè)模塊中用到的時(shí)間單位不同,需要用到以下的時(shí)間結(jié)構(gòu):

用`timescale命令來聲明本模塊中所用到的時(shí)間單位和時(shí)間精度。

用系統(tǒng)任務(wù)$printtimescale來輸出顯示一個(gè)模塊的時(shí)間單位和時(shí)間精度。

用系統(tǒng)函數(shù)realtime及%t格式聲明來輸出顯示EDA工具記錄的時(shí)間信息。

條件編譯命令

`ifdef、`else、`endif

這與C語(yǔ)言用法類似,這里就不贅述了。

總結(jié)一下

Verilog HDL的語(yǔ)法與C語(yǔ)言的語(yǔ)法類似,但是一定要意識(shí)到Verilog HDL描述的是電路,光有代碼還不夠,器件可能運(yùn)行的結(jié)果并不是代碼想要的效果。另外要注意理解并行的概念,這里的并行是硬件在時(shí)鐘驅(qū)動(dòng)真的同時(shí)按照所設(shè)計(jì)的邏輯運(yùn)行。一些重要的概念:

阻塞〔Blocking〕和非阻塞〔Non-Blocking〕賦值的不同

順序塊和并行塊的不同

塊與塊之間的并行執(zhí)行的概念;

task和function的概念。

那么最好的學(xué)習(xí)辦法是什么呢?寫代碼、仿真、綜合、優(yōu)化布局布線,挖坑、踩坑、填坑,在錯(cuò)誤中總結(jié),漸進(jìn)明晰、不斷實(shí)踐總結(jié)。

-

C語(yǔ)言

+關(guān)注

關(guān)注

180文章

7614瀏覽量

137702 -

Verilog HDL

+關(guān)注

關(guān)注

17文章

126瀏覽量

50475

原文標(biāo)題:看思維導(dǎo)圖:一文帶你學(xué)Verilog HDL語(yǔ)言

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Verilog HDL設(shè)計(jì)的要點(diǎn)

基于Verilog HDL語(yǔ)言的FPGA設(shè)計(jì)

Verilog HDL華為入門教程

Verilog HDL語(yǔ)言在FPGA/CPLD開發(fā)中的應(yīng)用

Verilog HDL程序基本結(jié)構(gòu)與程序入門

Verilog HDL語(yǔ)言簡(jiǎn)介

VHDL和Verilog HDL語(yǔ)言對(duì)比

Verilog HDL程序設(shè)計(jì)與實(shí)踐

Verilog HDL硬件描述語(yǔ)言簡(jiǎn)介

Verilog HDL入門教程

基于FPGA Verilog-HDL語(yǔ)言的串口設(shè)計(jì)

Verilog HDL入門教程

Verilog HDL的基礎(chǔ)知識(shí)詳細(xì)說明

Verilog HDL語(yǔ)言技術(shù)要點(diǎn)

Verilog HDL語(yǔ)言技術(shù)要點(diǎn)

評(píng)論