1.引言

獨學(xué)而無友,則孤陋而寡聞;

2.背景介紹

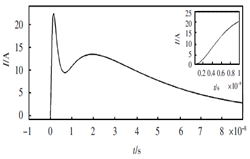

某控制器產(chǎn)品在做認證測試中,ESD ±6KV接觸放電出現(xiàn)通訊故障死機問題,需要重啟后可恢復(fù),針對此問題進行分析和整改。

3.分析與整改

3.1控制器組網(wǎng)與實驗點

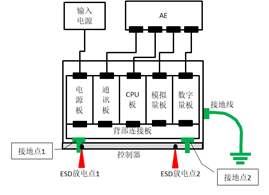

控制器組網(wǎng)與ESD放電點示意圖參見圖1所示。

(a)組網(wǎng)與放電點示意圖

(b)放電點實物圖

圖1 控制器組網(wǎng)及實驗點

3.2試驗現(xiàn)象

ESD接觸放電±6KV,對放電點1和放電點2進行試驗時(每個點放電3-6次左右),及放電點3(每個點放電10-20次左右)就會出現(xiàn)通訊故障,無法與上位機通訊,處于死機狀態(tài),需要重動恢復(fù)。放電點4試驗無問題。

3.3接地可靠性排查

3.3.1接地點阻抗測定

利用萬用表對蓋板接地點阻抗測定,結(jié)果如下:

表1 接地阻抗

注:ESD頻譜達到GHz頻段,利用萬用表進行機殼接地阻抗值是不準確的,但可以做為初步的定性分析判斷。

3.3.2機殼接地點變更排查

對控制器的接地點位置進行人為變更,對各放電點進行ESD實驗,驗證各接地的可靠性,詳細結(jié)果參見表2。

表2 機殼接地點變更實驗結(jié)果

3.3.3接地可靠性排查小結(jié)

(1)接地點位置變更后到2后,放電點2/3/4實驗沒有問題,但放電點1仍然會導(dǎo)致通訊故障死機;接地點位置變更后到1后,放電點1/4實驗沒有問題,但放電點2/3仍然會導(dǎo)致通訊故障死機。

(2)蓋板與機殼地搭接不良,接地點1/2/3接地阻抗較大,接地點4的阻抗可接受;

(3)整體的控制器蓋板與機殼的搭接設(shè)計不可靠,導(dǎo)致ESD測試中會出現(xiàn)問題。

3.4接地不良導(dǎo)致通訊故障死機問題分析

3.4.1ESD耦合機理分析

3.4.1.1ESD波形參數(shù)

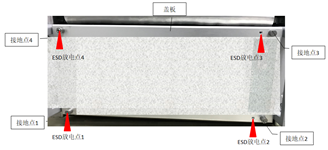

IEC61000-4-2標準中ESD放電電流波形參數(shù)如圖2所示[1],6KV的放電電流峰值為22.5(1±15%)A。

圖2接觸放電電流波形參數(shù)

3.4.1.2ESD頻譜特性

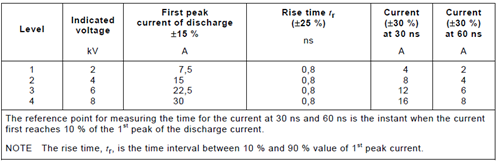

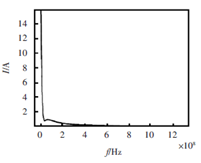

6KV等級ESD的放電電流與頻譜特性參見圖3和圖4所示[2]。ESD的幅值一般在頻率0~1.2 GHz 間,超過1.2 GHz 幅值基本衰減為0,整個頻率期間出現(xiàn)了2 次峰值.頻率在0~30 MHz 間,幅值逐漸衰減,并且衰減較快.然后隨頻率增加至60 MHz 時,幅值達到第二個峰值,隨著頻率繼續(xù)增加,幅值逐漸衰減至0。

圖3 6KV放電電流波形

圖4 6KV接觸放電電流頻譜

3.4.1.3ESD放電耦合機理分析

(1) ESD的干擾模式

ESD以共模干擾方式對控制器進行干擾,主要有以下幾種形式:

◆ ESD放電中形成的場耦合,一般發(fā)生在接地點良好,但接地位置附近有敏感信號或走線的情況:

◆ ESD放電電流在接地阻抗路徑中形成噪聲電壓Vnoise干擾敏感設(shè)備,一般發(fā)生在接地不良,接地阻抗較大的情況;

◆ ESD放電電流直接注入敏感信號中,一般發(fā)生在對pin進行ESD注入實驗的情況。

(2)結(jié)構(gòu)地分析:

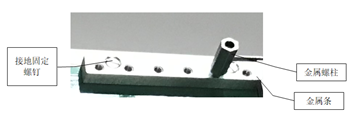

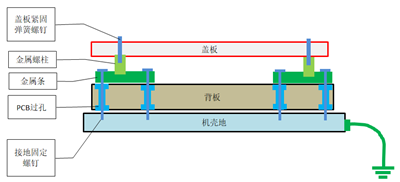

控制器蓋板接地的結(jié)構(gòu)層次:蓋板緊固彈簧螺釘→金屬螺柱→金屬條→接地固定螺釘→機殼地。PCB過孔無接地銅盤,與金屬條和機殼均無搭接。金屬條與機殼的搭接僅僅通過螺紋進行,搭接不可靠,阻抗大,結(jié)構(gòu)接地詳見圖5所示。

(a)蓋板接地點實物圖

(b)蓋板接地結(jié)構(gòu)示意圖

圖5 蓋板接地結(jié)構(gòu)

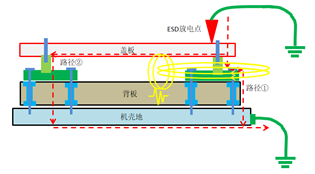

(3)干擾路徑與等效機理電路分析

◆ 當(dāng)蓋板與機殼地間的接地良好時,阻抗足夠低,與機殼形成等電位搭接,無壓差。

ESD的主要放電路徑為圖6中的①和②,因①的接地物理路徑較近,大部分干擾會從①路徑中流到大地。流過路徑①附近的電流形成的干擾場,會串?dāng)_周圍的敏感信號或敏感走線。

圖6 ESD放電路徑示意圖

◆ 當(dāng)蓋板與機殼地間的接地搭接較差時(搭接阻抗較大),ESD放電電流會在搭接點處形成噪聲電壓Vnoise。

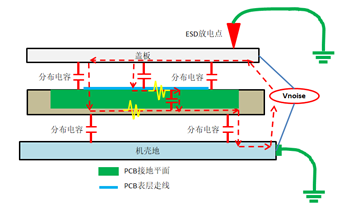

噪聲電壓通過蓋板與PCB板件的分布電容,形成干擾電流流過PCB,使得敏感干信號受干擾,參見圖7所示。

圖7 接地不良的ESD耦合機理示意圖

(4)干擾噪聲估算

通過接地阻抗測定與接地點變更ESD實驗結(jié)果,結(jié)合ESD的干擾機理,可以確定控制器為ESD放電電流在接地阻抗路徑中形成噪聲電壓Vnoise ,干擾了內(nèi)部敏感信號。

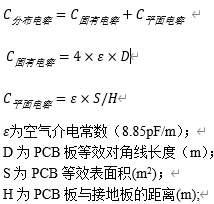

◆ PCB與結(jié)構(gòu)件間的分布電容估算

PCB板與蓋板間的分布電容可用以下公式進行估算[3]:

控制器的PCB尺寸為15cm*40cm,與蓋板距離3cm,與機殼距離2cm左右。PCB接地參考地層與蓋板間的分布電容約為33pf。

◆ 蓋板與機殼間搭接處的噪聲電壓估算

6KV接觸放電的放電電流峰值實測約為24A左右,接觸阻抗為0.3歐姆,電壓約為7.2V。

注:蓋板與機殼間的搭接阻抗為萬用表測試結(jié)果,實際的ESD頻段的搭接阻抗值要大于0.3Ω,本文暫以0.3Ω為例進行計算說明。

◆ 流過背板的電流:

I1=C*2πf*U=33pF*2*3.14*1.2GHz*7.2=0.25A。

注:為方便計算,ESD頻段擴展到1.2GHz。

◆ 流經(jīng)背板PCB參考地平面的噪聲電壓:

Vnoise=I1*Z=0.25A*3mΩ=0.75mV;

注:PCB的鋪地平面阻抗一般為mΩ級別,結(jié)合背板的過孔數(shù)量,估算PCB鋪地平面阻抗為3mΩ。

◆ 流經(jīng)背板PCB表層走線的噪聲電壓:

I2= C*2πf*U=3pF*2*3.14*1.2GHz*7.2=0.025A(流過通訊指示燈走線的電流)

Vnoise=L*di/dt=300nH*0.025A/(0.8ns)=9.4V。

注:背板表層通訊指示燈為最長走線,長度為20cm左右,走線寬度為10mil,電感量為300nH左右。指示燈走線與蓋板間的分布電容約為3pf。

3.4.2通訊故障死機問題原因排查

(1)通訊故障死機原因有二:通訊板受干擾或者CPU板受干擾。

進過排查,定位到是因為通訊指示燈走線過長(隔斷走線后無問題),導(dǎo)致ESD干擾耦合到背板通訊指示燈走線,噪聲電平達到9.4V的高頻干擾進入CPU板。9.4V的噪聲電壓足以干擾CPU板的敏感信號(1.2V、3.3V、5V等級的敏感信號),可以通過濾波電容、磁珠、TVS管等方法進行抑制。

圖8 通訊指示表層燈走線示意圖

(2)CPU導(dǎo)致死機原因有二:3.3V電源受干擾或時鐘受干擾。

通過前述分析,地平面上的噪聲電壓為0.75mV,不足以干擾3.3V電源。經(jīng)過排查確認ENC28J60的時鐘受干擾,導(dǎo)致出現(xiàn)通訊故障而死機。

3.5整改與驗證

因客戶要求不能整改PCB內(nèi)部電路及外觀可見措施,只能從結(jié)構(gòu)接地下手。

◆結(jié)構(gòu)地搭接整改:

針對蓋板與機殼間的四個接地點通過銅箔加強接地,整改措施如下。

| 整改前 | 整改后 |

◆實驗驗證:實驗采用±7KV等級無問題。

3.6落地設(shè)計

最終落地設(shè)計為背板的表面和底面四周進行鋪銅處理,加強蓋板與結(jié)構(gòu)地的搭接。實驗驗證無問題,落地措施參見下圖。

圖9 背板與機殼間的搭接處理

4.思考與啟示

(1)ESD干擾以共模形式串入PCB線路或通過空間場耦合干擾敏感信號,需要解耦分析;

(2)對于接地點可靠性的排查,可通過人為改變接地位置進行故障問題的分析;

(3)ESD抑制的一大手法是接地,要確保放電點與機殼地搭接的可靠性,保證搭接阻抗在ESD頻段范圍內(nèi)足夠小,不足以形成干擾電壓;

(4)PCB敏感信號或與敏感信號相關(guān)的信號線,避免在表層長距離走線而引起的干擾,無法避免時,注意信號換板連接器附近的濾波處理。

(5)ESD敏感信號在設(shè)計前期需要進行ESD干擾評估,特別是噪聲等級的評估,有利于抑制器件的選型,同時在PCB板進行干擾風(fēng)險規(guī)避是成本最低,效果最好的方法。

(6)ESD的抑制手段多樣化,除了接地對ESD干擾進行泄放外,還可通過濾波、屏蔽、瞬態(tài)抑制、隔離、放電敏感距離控制、采用絕緣類材料阻斷放電等等手段進行抑制,結(jié)合設(shè)計需求落地。

-

ESD

+關(guān)注

關(guān)注

49文章

2065瀏覽量

173379 -

接地

+關(guān)注

關(guān)注

7文章

780瀏覽量

45800

原文標題:ESD測試中接地不良引起的通訊故障死機問題分析

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Profinet IO通信故障原因及解決辦法

斷路器常見故障及解決辦法

常見墊圈故障及解決辦法 防漏墊圈的設(shè)計與應(yīng)用

電力電纜的常見故障及解決辦法 電力電纜與通訊電纜的區(qū)別

雷達探測器常見故障及解決辦法

PCBA板常見故障及解決辦法

常見穩(wěn)壓器故障及解決辦法

電力電容器的常見故障及解決辦法

常見MCU故障及解決辦法

萬用表常見故障及解決辦法

常見元器件故障及解決辦法

分析波峰焊時產(chǎn)生連錫(短路)的原因以及解決辦法

變頻器常見故障和解決辦法,這一篇就夠了,各大品牌都適用

ESD測試中接地不良引起的通訊故障死機的原因及解決辦法

ESD測試中接地不良引起的通訊故障死機的原因及解決辦法

評論