引言

VHDL是一種硬件描述語言,于1983年被IEEE制定為國際標準IEEE1076。近年來國內引進和出版了不少教材,使其在國內得到迅速推廣。由于VHDL最初目的是為了實現硬件的建模而被提出的,所以其措施能力超越了數字邏輯集成電路的范圍。而現有的EDA工具基本上只能支持VHDL的子集,特別是針對FPGA/CPLD器件進行的不同的綜合工具,其綜合子集并非統一,不少初學者很難掌握。即使是部分有經驗的設計者,對于通常高級語言中都會涉及的循環語句,在VHDL中往往也不能運用自如,甚至無法表達此類邏輯,從而限制了VHDL的應用水平。例如,VHDL的并行堆排序描述就是一個比較典型的例子。該實例十分類似通常數據結構的描述,推廣前景誘人;但只能通過仿真,卻不能在目前任何一個EDA工具進行綜合,導致無實用價值。

本文從高級語言涉及最多的Loop語句出發,討論如何在VHDL中解決這類問題。

1 無法綜合的Loop動態條件

VHDL中Loop表達式有三種體現形式:While……Loop、For……Loop和單獨的Loop語句。它還支持Next、Exit和標號,因此,循環語句的表達能力大于常規的C或PASCAL語言。程序1是利用For語句和While語句描述插入算法的部分代碼。

程序1 不可綜合的VHDL循環語句

……

for I in 2 to Length loop ---Length為一個變量

Temp:=MyList(I);

J:=I;

While(j》1)and MyList(j-1) MyList(j):=MyList(j-1);

j:=j-1;

End loop;

MyList(j):=Temp;

End loop;

……

對于第一個For語句,EDA工具Synplify綜合時將會給出無邊界的范圍錯誤提示。

@E:“H:.vhd”|for loops with unbound ranges should contain w wait statement

即使部分優秀的綜合工具,例如ORCAD Express、Mentor Grpahs QuickHDL等能夠綜合第一個For語句,也無法支持第二個While條例表達式。ORCAD Express將給出表達式不可靜態計算的錯誤提示。

。.vhd(45):Error,expression does not evaluate to a constant.

由于程序1在C程序員看來是沒有問題的,因此,初學者往往不能解決好此類問題,從而使學習陷入困境,無法充分利用VHDL來表述邏輯。

2 直接代換法

對于第一類無邊界的范圍錯誤問題,可以用循環的綜合機制轉化為相應的語句。例如下面代碼:

for I in 0 to 1 loop

Out_Bus(i)《=In_Bus(i);

End loop;

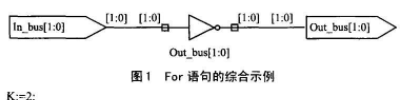

其對應綜合后的電路見圖1。

圖1 For語句的綜合示例

相應的,也可以用下列語句直接代入代換:

Out_Bus(0)《=In_Bus(0);

Out_Bus(1)《=In_Bus(1);

程序1可以采用下列VHDL代碼表示:

K:=2;

Temp:=MyList(2);

If(MyList(1) MyList(2):=MyList(1);

J:=1;

End if;

MyList(J):=Temp;

J:=3;

Temp:=MyList(3);

If(MyList(2) MyList(3):=MyList(2);

J:=2;

End if;

If(MyList(1) MyList(2):=MyList(1);

J:=1;

End if;

MyList(J):=Temp;

……

然而,這種使用方法要求設計者清楚循環條件一定會執行的次數,否則將無法實施。當循環次數比較大時,代碼編寫工作量將十分龐大,因此可以采用第二種方法——邊界擴充法。

3 邊界擴充法

邊界擴充法是指在邊界未定時,可以將邊界定為最大可能的范圍,即用靜態表達來替代。例如程序1的代碼可以改寫為:

constant MAX:integer=100; --MAX必須大于MyLen所有可能的取值

……

Out_loop:for I in 2 to MAX loop

Exit out_loop when I》MyLen; --MyLen為變量

Temp:=MyList(I);

countj:=I;

inter_loop:for j in I downto 2 loop

countj:=j;

exit inter_loop when MyList(j-1) MyList(j):=MyList(j-1);

End loop;

MyList(countj):=Temp;

End loop;

盡管這種方法可以處理未知邊界和未定表達式的情況,但十分消耗空間,特別是當MyLen相對MAX比較小的時候,代價非常大。此時,可以利用時間換空間的方法進行轉換。

4 計數器法

計數器法是指引入時鐘和計數器,用計數器對邊界條件進行控制,也可以將動態表達式直接代入轉化相應的靜態表達式。例如,上述代碼的For條件可以用下列代碼替換:

if(Reset=‘1‘)then

I:=2;

Elsif clk=‘1‘and clk‘event then

Temp:=MyList(I);

J:=2;

While(j》1)and MyList(j-1) MyList(j):=MyList(j-1);

j:=j-1;

End loop;

MyList(j):=Temp;

I:=(I+1);

If(I=MyLen+1)then I:=2;end if;

End if;

相比原來的代碼,引入了1個時鐘和1個復位。但綜合開銷最大的循環語句卻被取代了,因此,綜合產生門的數目將大幅度下降,但處理時間將相應延長到原來循環條件范圍。

本刊網絡補充版中發表了四個源代碼,分別為不可綜合例子、直接代換法、邊界擴充法和計算器法,內部都有相應注釋。其中計數器法改進為雙計數器方法。

結語

以上三種方法各有優缺點,不可一概而論,可以根據實際情況處理。直接代換法一般用于循環次數少的情況;邊界擴充法一般用于循環次數接近最大邊界時;計數器方法一般用于芯片內部時鐘相對信號時鐘快許多的情況。

責任編輯:gt

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

cpld

+關注

關注

32文章

1257瀏覽量

169633 -

vhdl

+關注

關注

30文章

817瀏覽量

128337

發布評論請先 登錄

相關推薦

在verilog中調用VHDL模塊

如何在vhdl代碼中編寫Expectation maximization algo

如何在VHDL代碼中實例化LVDS緩沖區嗎?

如何用VHDL、Verilog HDL實現設計輸入?

VHDL中Loop動態條件的可綜合轉化

vhdl數字系統設計

在PLD開發中提高VHDL的綜合質量

在沒有綜合工具情況下,如何設計數字電路?

使用FPGA設計數字電路時的綜合工具介紹

如何在VHDL中解決綜合工具使用轉化問題

如何在VHDL中解決綜合工具使用轉化問題

評論