1.寄存器

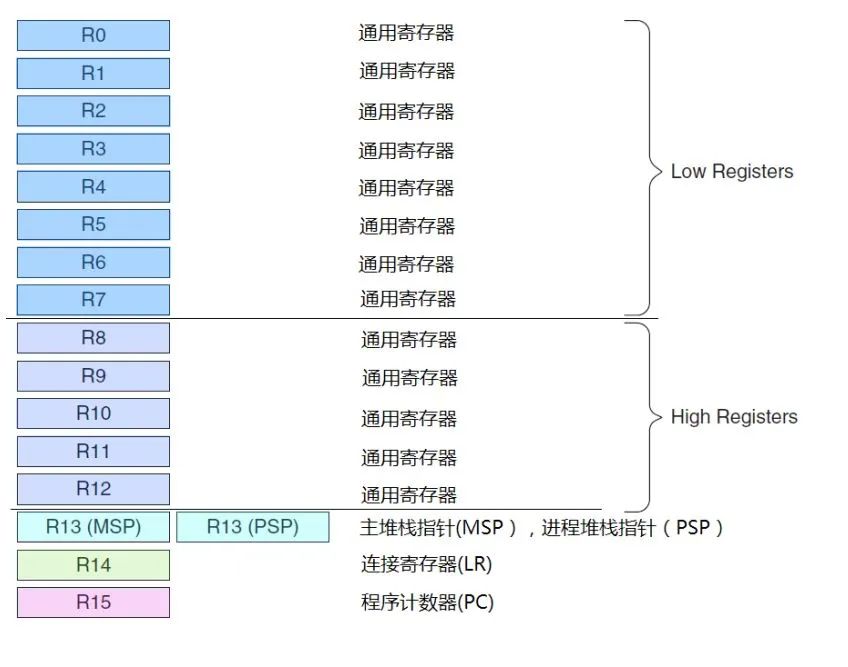

CM3擁有R0~R15通用寄存器和一些特殊功能寄存器

R0~R12這些通用寄存器,復(fù)位初始值都是不可預(yù)料的

2.CM3有R0到R15的通用寄存器組

注:絕大部分的16位thumb只能訪問R0到R7,而32位thumb-2可以訪問全部寄存器

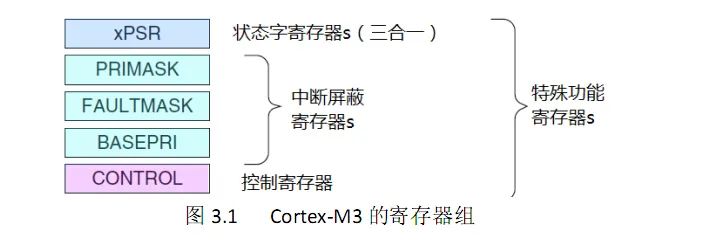

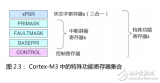

3.特殊功能寄存器

3.1程序狀態(tài)寄存器組(應(yīng)用程序PSR+中斷號PSR+執(zhí)行PSR)

3.2中斷屏蔽寄存器組:用于控制異常的除能和使能

3.3控制寄存器:用于定義特權(quán)級別和當(dāng)前使用哪個(gè)堆棧指針

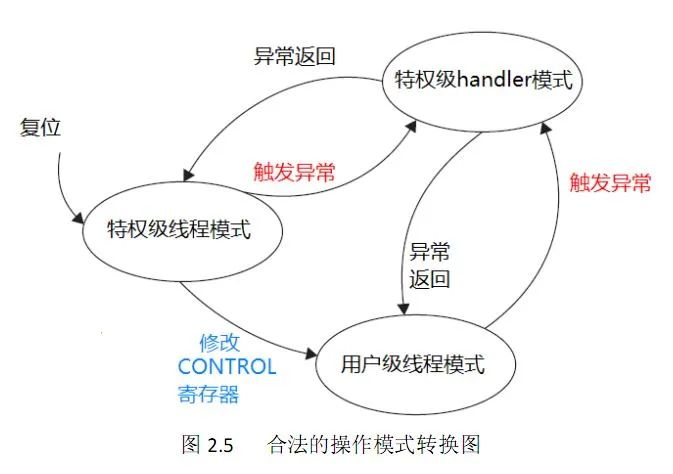

4.操作模式和特權(quán)級別:

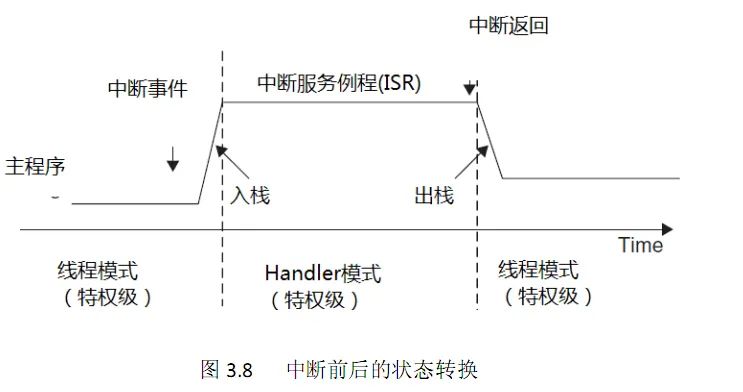

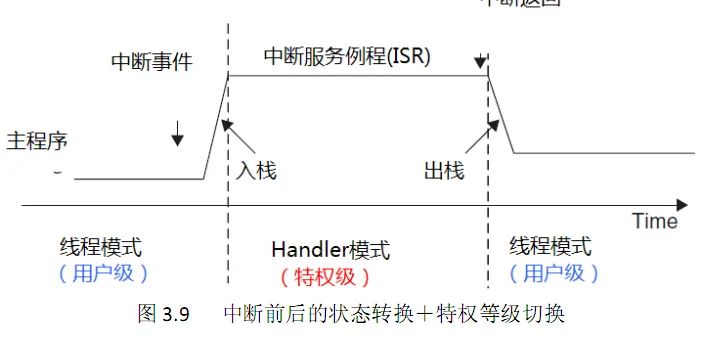

兩種操作模式(處理器模式):Handler模式和線程模式(用于區(qū)分異常服務(wù)例程的代碼和普通程序的代碼)

兩種特權(quán)等級:特權(quán)級和用戶級(是指在硬件層面上對存儲器訪問權(quán)限的設(shè)置)

注:CM3在運(yùn)行主程序(即線程模式)可以使用特權(quán)級別和用戶級別;但是異常服務(wù)例程(即handler模式)只能使用特權(quán)級別。當(dāng)處于線程+用戶模式時(shí)一些訪問權(quán)限將被禁止

將代碼區(qū)分成用戶級和特權(quán)級,有利于程序架構(gòu)的穩(wěn)定,如某一個(gè)用戶代碼出問題,不會使其成為害群之狗,因?yàn)橛脩艏墑e的代碼是禁止對一些要害寄存器操作的。

5.異常處理

5.1CONTROL[0]=0;

5.2CONTROL[0]=1;

CONTROL[0]只有在特權(quán)級別下可以訪問,若在用戶級別想訪問先通過"系統(tǒng)服務(wù)呼叫指令(SVC)"來觸發(fā)SVC異常,然后在該異常的服務(wù)例程中可以修改CONTROL[0]。

6.下面是各操作模式的轉(zhuǎn)換

7.異常和中斷

可以有11個(gè)系統(tǒng)異常和最多240個(gè)外部中斷(IRQ),具體芯片使用了多少要看芯片制造廠商。

作為中斷功能的強(qiáng)化,NVIC 還有一條NMI輸入信號線,具體做什么由芯片制造商決定,NMI(not masked interrupted)

8.向量表:當(dāng)一個(gè)異常被CM3內(nèi)核接受。對應(yīng)的異常Handler就會執(zhí)行,向量表用來決定Handler的入口地址。

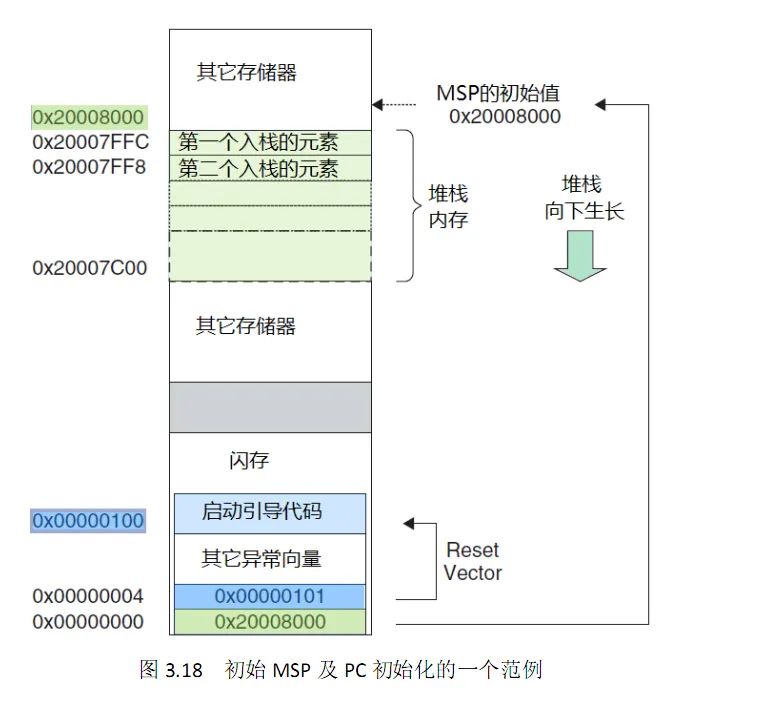

9.CM3的雙堆棧:主堆棧(MSP)和進(jìn)程堆棧(PSP)。是由CONTROL[1]控制的。

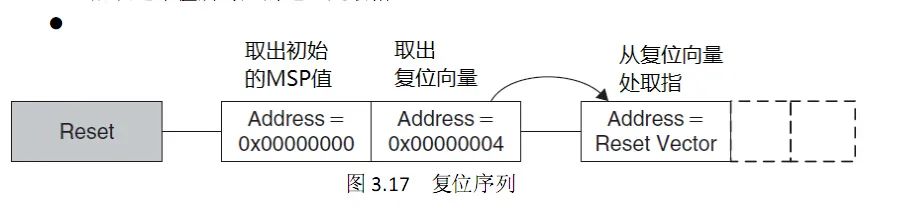

10.復(fù)位序列:

先從0X00地址取出MSP的值再從0x04地址取出PC的初始值,0X04處存的值是復(fù)位向量,而不是跳轉(zhuǎn)指令。

此處CM3與ARM及單片機(jī)不同。以前ARM都是從0X00地址開始執(zhí)行第一條指令,一般第一條指令都是跳轉(zhuǎn)指令

11.MSP及PC初始化的一個(gè)例程

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121178 -

Cortex-M3

+關(guān)注

關(guān)注

9文章

270瀏覽量

59591

原文標(biāo)題:Cortex-M3寄存器等基礎(chǔ)知識

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

cortex-m3中如何將AHB-AP 數(shù)據(jù)讀/寫寄存器中的內(nèi)容寫入RAM中?

Cortex-M3 技術(shù)參考手冊

LPC17XX系列Cortex-M3微控制器的寄存器相關(guān)資料詳細(xì)說明

寄存器的名稱和地址的映射詳細(xì)資料分析

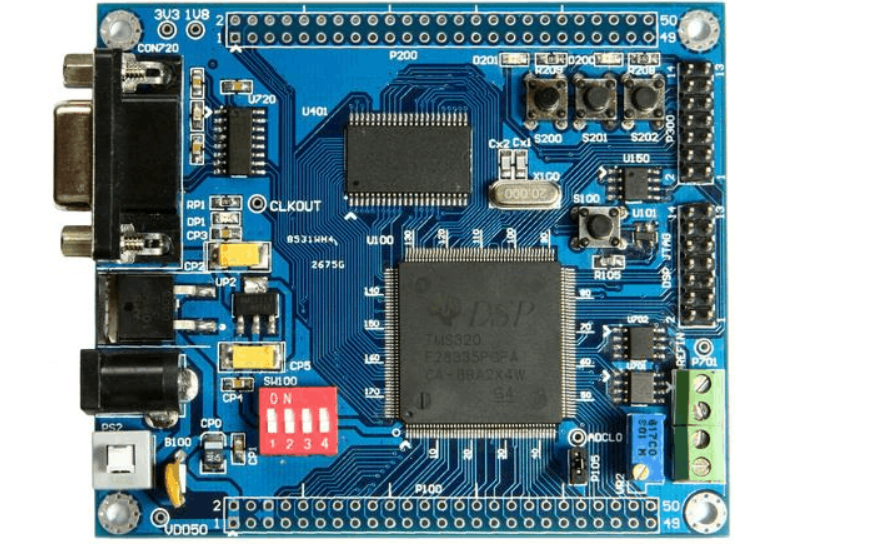

DSP28335 ACD寄存器的詳細(xì)資料說明

ARM Cortex-M3 內(nèi)核的不同功能模塊

Cortex-M3寄存器組資料下載

Cortex-M3處理器內(nèi)核與基于Cortex-M3的MCU關(guān)系

ARM Cortex-M3系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

Cortex-M3 內(nèi)部寄存器

Cortex-M3寄存器等基礎(chǔ)知識

Cortex-M3入門指南(二):寄存器

Cortex-M3寄存器的詳細(xì)資料匯總

Cortex-M3寄存器的詳細(xì)資料匯總

評論