作者:OpenSLee

1、Floating-Point IP支持的運(yùn)算操作

1)Multiply—乘法

3)Accumulator—累加

4) Fused multiply-add--融合乘加

5) Divide—除法

6)Square-root—平方根

7) Comparison—比較

8) Reciprocal—倒數(shù)

9)Reciprocal square root—倒數(shù)平方根

10)Absolute value—絕對值

11) Natural logarithm—自然對數(shù)

12)Exponential—指數(shù)

13)Conversion from floating-point to fixed-point—浮點(diǎn)轉(zhuǎn)定點(diǎn)

14)Conversion from fixed-point to floating-point—定點(diǎn)轉(zhuǎn)浮點(diǎn)

15) Conversion between floating-point types—浮點(diǎn)類型之間的轉(zhuǎn)換

2、Floating-Point IP接口

如下圖所示,Xilinx Floating-Point IP主要分為操作數(shù)s_axis_a,s_axis_b,s_axis_c,可編程操作s_axis_operation和輸出結(jié)果m_axis_result。

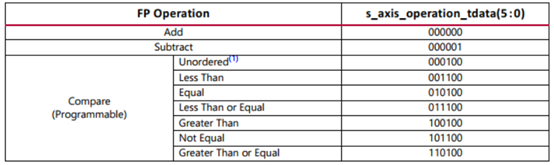

2.1 s_axis_operation_tdata

當(dāng)我們同時選擇加法和減法運(yùn)算或選擇可編程比較器時,將存在s_axis_operation通道。s_axis_operation_tdata的具體含義如下表所示。

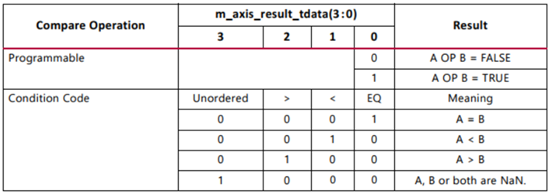

2.2 m_axis_result_tdata

如果是比較操作,則結(jié)果中的有效位取決于所選的比較操作。

3、AXI4-Stream Protocol

使用AXI4-Stream接口帶來了標(biāo)準(zhǔn)化,并增強(qiáng)了Xilinx IP LogiCORE?解決方案的互操作性。除了諸如aclk,acclken和aseten之類的常規(guī)控制信號外,所有往返于浮點(diǎn)運(yùn)算符核心的輸入和輸出均使用AXI4-Stream通道進(jìn)行傳輸。通道始終由TVALID和TDATA以及幾個可選的端口和字段組成。在浮點(diǎn)運(yùn)算符中,支持的可選端口為TREADY,TLAST和TUSER。 TVALID和TREADY一起執(zhí)行握手以傳輸消息,其中有效負(fù)載為TDATA,TUSER和TLAST。浮點(diǎn)運(yùn)算符對TDATA字段中包含的操作數(shù)進(jìn)行運(yùn)算,并將結(jié)果輸出到輸出通道的TDATA字段中。浮點(diǎn)運(yùn)算符本身并不使用TUSER和TLAST輸入,但是內(nèi)核提供了以與TDATA相同的延遲來傳送這些字段的功能。預(yù)期該功能可簡化系統(tǒng)中浮點(diǎn)運(yùn)算符的使用。例如,浮點(diǎn)運(yùn)算符可能正在處理流式打包數(shù)據(jù)。在此示例中,核心可以配置為通過分組數(shù)據(jù)通道的TLAST,從而節(jié)省了系統(tǒng)設(shè)計人員為該信息構(gòu)建旁路路徑的工作。

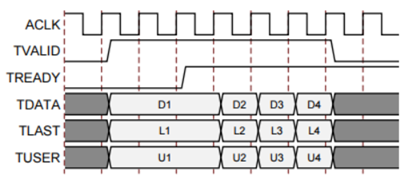

Basic Handshake:

如下圖所示,在AXI4-Stream通道中的數(shù)據(jù)傳輸。 TVALID由通道的源(主)側(cè)驅(qū)動,而TREADY由接收器(從屬)驅(qū)動。 TVALID指示有效負(fù)載字段(TDATA,TUSER和TLAST)中的值有效。 TREADY表示從機(jī)已準(zhǔn)備好接收數(shù)據(jù)。當(dāng)TVALID和TREADY在一個周期中都為TRUE時,將發(fā)生傳輸。主機(jī)和從機(jī)分別為下一次傳輸分別設(shè)置TVALID和TREADY。

編輯:hfy

-

接口

+關(guān)注

關(guān)注

33文章

8692瀏覽量

151922 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122144

發(fā)布評論請先 登錄

相關(guān)推薦

XADC IP核介紹

IP地址會被黑?

IP68防水試驗機(jī)的操作方法

12芯M16接口插拔操作要點(diǎn)介紹

優(yōu)秀的Verilog/FPGA開源項目-浮點(diǎn)運(yùn)算器(FPU)介紹

Floating-Point IP接口操作介紹

Floating-Point IP接口操作介紹

評論