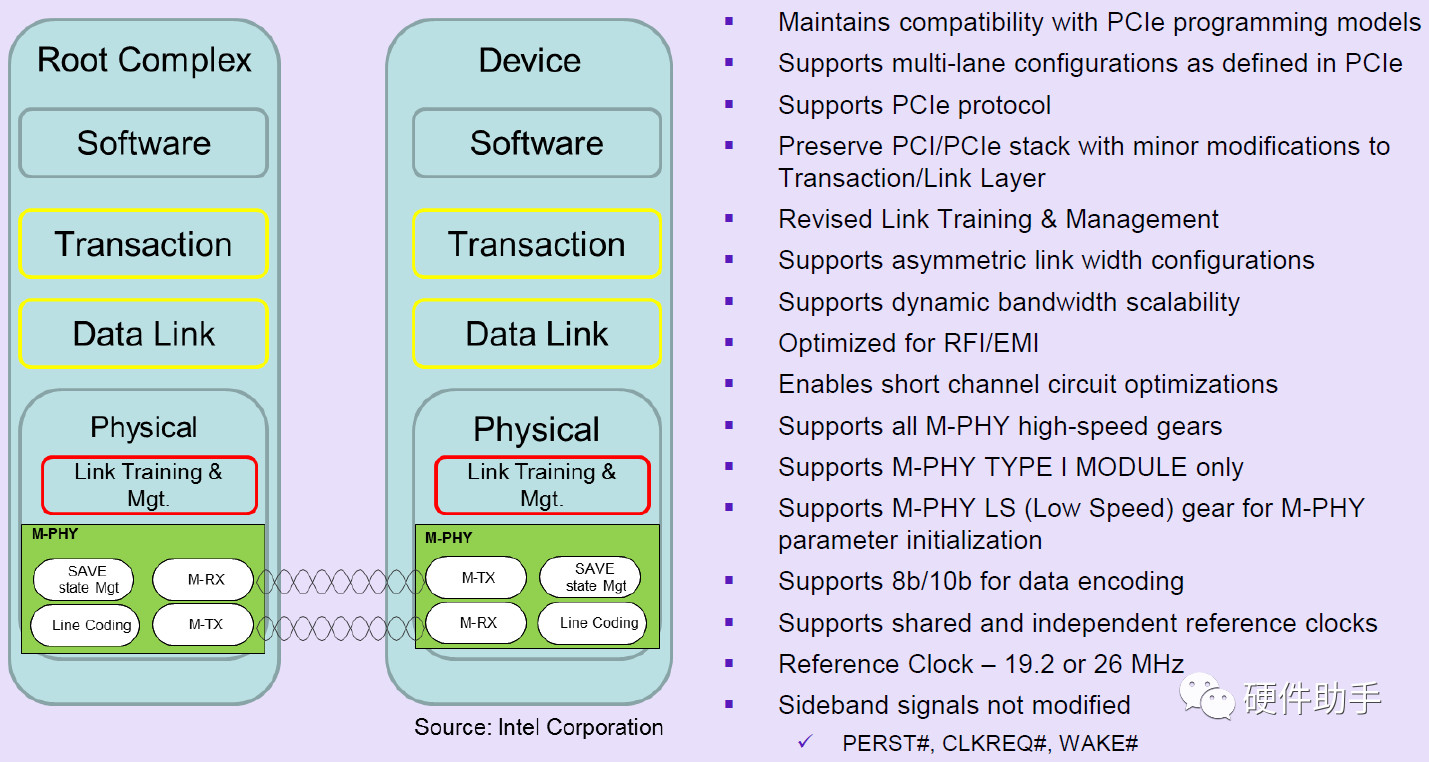

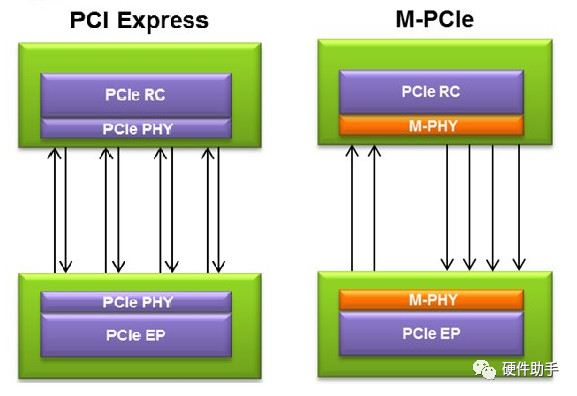

M-PCIe即Mobile PCIe,主要應用對象是智能手機等嵌入式設(shè)備。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于標準的PCIe總線,M-PCIe ECN主要的改動在物理層,通過引入M-PHY,旨在獲得更低的功耗以適應嵌入式設(shè)備的低功耗要求。

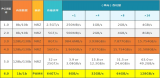

M-PCIe的主要特性如下:

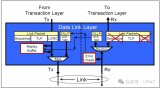

M-PCIe的上層協(xié)議層、事務(wù)層(TL)、數(shù)據(jù)鏈路層(DLL)和標準PCIe總線是兼容的。M-PCIe和PCIe設(shè)備的Link Training and Status State Machine (LTSSM)具有不同的設(shè)計,這主要是為了保證M-PHY獨特的低功耗特性。

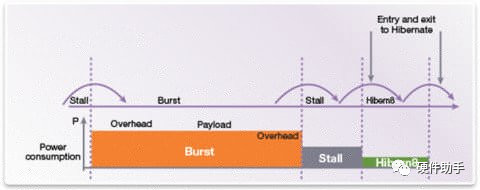

由于其工作模式與各個突發(fā)傳輸之間的關(guān)系,M-PHY甚至可以進一步降低功耗。在M-PHY設(shè)計中,PHY僅在實際傳輸時處于最大功率。在完成突發(fā)傳輸后,PHY進入超低功耗的“STALL”狀態(tài),此后不久就進入其最低功率的“HIBERN8”狀態(tài)。通過這樣的設(shè)計,可以使得M-PHY的功耗降至最低,從而延長電池壽命。

為了進一步降低功耗,M-PCIe系統(tǒng)可以實現(xiàn)非對稱鏈路,允許鏈路上不同數(shù)量的發(fā)送器和接收器。PCIe強制設(shè)備具有4個發(fā)送器和4個接收器,以滿足其對4個通道的PCIe-to-cellular帶寬的需求。而M-PCIe允許設(shè)備將發(fā)送器的數(shù)量減少到所需的量,并且在這種情況下,功耗會更低。

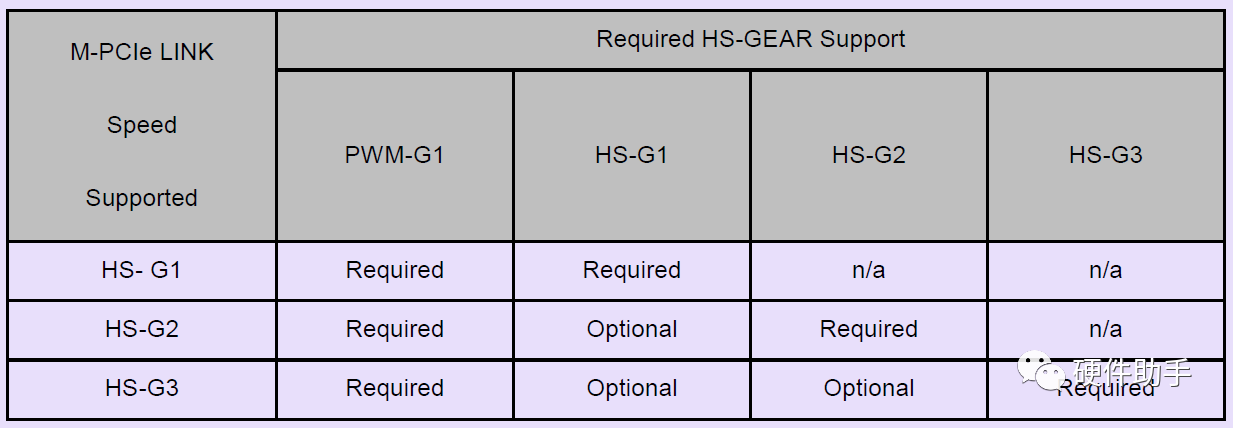

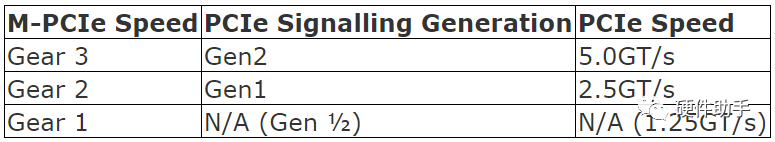

雖然M-PCIe規(guī)范允許設(shè)備比PCIe PHY消耗更少的功耗,但PCIe提供的速度也高于M-PCIe。一般而言,可以將M-PHY Gear M視為與PCIe Generation (M-1)相同的帶寬。

以上就是針對M-PCIe的簡單介紹,詳細可參考PCIe spec和MIPI M-PHY spec。

-

接收器

+關(guān)注

關(guān)注

14文章

2479瀏覽量

72212 -

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83186 -

PCIE總線

+關(guān)注

關(guān)注

0文章

58瀏覽量

13455 -

發(fā)送器

+關(guān)注

關(guān)注

1文章

259瀏覽量

26894

發(fā)布評論請先 登錄

相關(guān)推薦

PCIe 5.0市場加速滲透,PCIe 6.0研發(fā)到來

Teledyne LeCroy推出Summit M64 PCIe協(xié)議分析儀/訓練器

TeledyneLeCroy推出新PCIe協(xié)議分析儀Summit M64

pcie 4.0與pcie 5.0的區(qū)別

PCIe轉(zhuǎn)M.2適配器使用指南

PCIe 4.0與PCIe 3.0的性能對比

PCIE數(shù)據(jù)鏈路層架構(gòu)解析

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

只需一個PCIe插槽,4盤位快速抽取擴展PCIe5.0 M.2 SSD ,裝機實測

新思科技PCIe 7.0驗證IP(VIP)的特性

Mini PCIe接口和M.2接口連接器各有哪些優(yōu)點

pcie4.0和pcie3.0接口兼容嗎

深入解析PCIe及其在芯片行業(yè)的重要性

一文解析PCIx系列M-PCIe

一文解析PCIx系列M-PCIe

評論