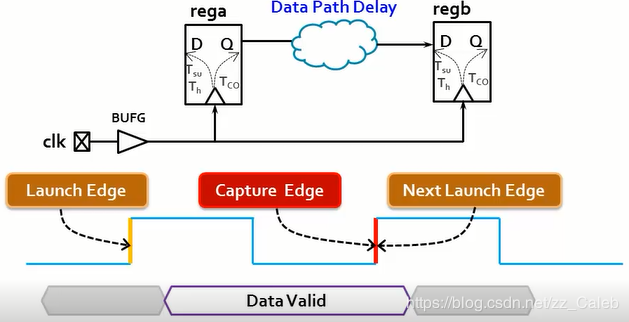

1、發起沿和捕獲沿(Launch edge & Capture edge)

①

② Launch edge是發送數據的時鐘邊沿,通常選擇上升沿。

③ Capture edge是捕獲段捕獲到該數據的時鐘邊沿。

④ 通常情況下這兩個邊沿會有一個時鐘周期的差別。

2、時序路徑(Timing path典型時序路徑有四種)

①

② 第一類時序路徑(紅色)

- 從device A的時鐘到FPGA的第一級寄存器的輸入端口。

③ 第二類時序路徑

- 兩個同步元件之間的路徑(rega到regb藍色)

④ 第三類時序路徑

- 最后一集寄存器到device B數據端口的路徑(黃色)

⑤ 第四類時序路徑

- 端口到端口的路徑(dinb到dinb綠色)

⑥ 我們要關注的是這些路徑的

- 起始點(start point)記作S

- 終止點(end point)記作E

-

- 前三條路徑的起始點,都是發送寄存器的時鐘端口,終止點都是接收寄存器的數據端口。

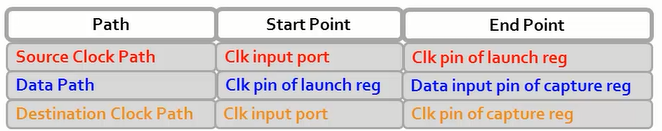

⑦ 常規時序路徑的組成

- 我們給出基本模型(可看出rega 和 regb時鐘是不同的)

-

- 源端時鐘路徑(紅色) 數據路徑(藍色) 和目的段時鐘路徑(黃色)

-

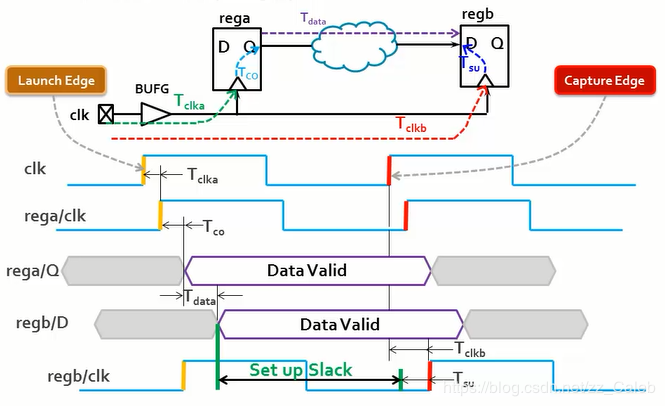

3、數據到達時間和數據需求時間

① 數據到達時間

-

- 數據在發送沿發送之后,經過多長時間會到達接收寄存器的數據端口,即到達regb的D端口的時刻,這個時刻就是數據到達時間。

- 我們需要選擇一個參考(基準)時間點。通常選擇launch edge作為零時刻基準點。

- 數據經過Tco時間,到達Q端口。

- 數據從Q端口,要經過組合邏輯,以及布線的線延時才能到達接收短的D端口(Tdata)。

- 故有公式如下:

-

- 選擇launch edge作為零時刻基準點。

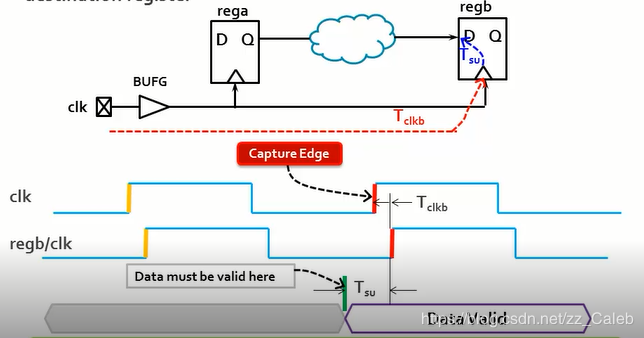

② 時鐘到達時間(clock Arrival Time)

- 觀察捕獲寄存器的時鐘。

-

- 選擇launch edge作為零時刻基準點。其實是launch edge加上一個時鐘周期。

4、建立時間的裕量和保持時間的裕量(Setup slack & Hold Slack)

① 建立時間(數據需求時間:Tsu)

-

- 數據可以被穩定的捕獲到的最小時間。

- 我們仍然關注捕獲寄存器。

- 數據需要在時鐘捕獲沿到達之前的一段時間,必須到達。相當于是數據到達regb的時鐘端口 和 regb的時鐘處于capture edge這兩個情況同時滿足的時候,才可以進行接收數據。

- 換句話就是說,數據至少提前時鐘Tsu的時間到達捕獲寄存器的數據端口。

- 數據所需要的時間是

-

- 其中Set up Uncertainty(一般是時間抖動造成的Uncertainty時間)。

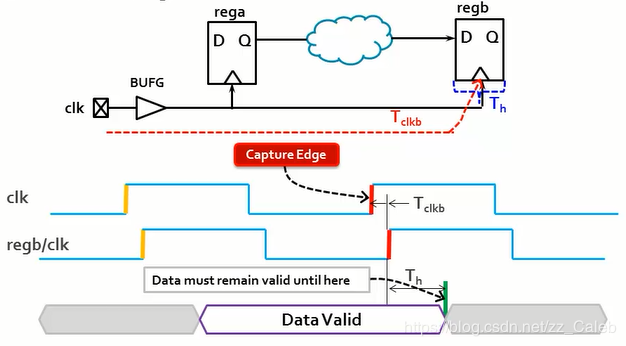

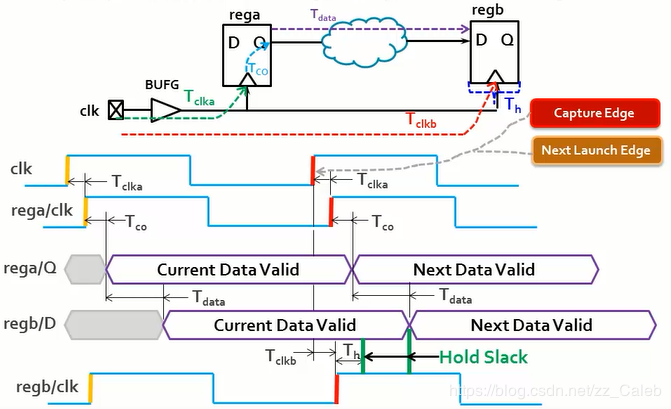

② 保持時間情況下的數據需求時間(Data Request Time-Hold)

-

- 當我們捕獲到數據之后,數據還應該穩定的存在一定時間。

- 除了有Tlckb的時鐘延時之外,還要看到捕獲寄存器本身的保持時間需求。

- Tclkb時鐘延時,然后數據到達后,至少還需要Th的保持時間。

-

③ Tsu和Th確定了數據的有效窗口。

- 數據有效窗口的起始沿就是Tsu

- 終止端口就是Th。

④ 建立時間裕量(Setup Slack)

- 在做時序分析時,我們的建立時間的需求可以滿足,那么這條路徑上發送的數據,就可以被目的寄存器穩定的捕獲到。

- 我們來看一下我們的模型:

-

- Tclka

- Tco

- Tdata

- Tclkb

- Tsu

- 數據需求時間(Tsu)-當前數據到達時間

-

-

⑤ 保持時間的裕量(Hold Slack)新的數據不能太早的到達,否則就破壞了原來的數據

-

- Tclka

- Tco

- Tdata

- Tclkb

- Th

- 新的數據到達時間-數據需求時間(Th)

-

-

⑥ 如果Slack為正,說明我們的時序是滿足的。

⑦ 為什么會出現Slack為負的情況?

- 對于Set up Slack為負的情況

- 數據延時太大,導致數據建立時間Tsu不夠了,見下圖:

-

- Hold Slack為負

- 時鐘的延遲太大,導致當前data的Capture time到來的時候,已經在傳下一個data了。

-

⑧ Tdata = Tlogic(組合邏輯,邏輯門的延時)+Tnet(布線,線的延時)

- Tlogic:主要和我們的代碼風格有關。

- Tnet:可能跟我們的布局布線的策略有關。

⑨ 系統的時鐘頻率Ts >= Tco + Tdata + Tsu這三者決定了系統的時鐘的最高頻率。

5、總結:

① 通常我們都是以Launch edge作為零時刻點(參考時刻點)

② 通常Capture edge time = Launch edge time + 1 clock cycle

③ Tsu和Th是芯片決定的。

編輯:hfy

-

寄存器

+關注

關注

31文章

5363瀏覽量

121198 -

時序分析

+關注

關注

2文章

127瀏覽量

22617

發布評論請先 登錄

相關推薦

時序分析基本概念介紹

時序分析和時序約束的基本概念詳細說明

FPGA設計中時序分析的基本概念

時序分析基本概念解析

時序分析的基本概念及常規時序路徑的組成

時序分析的基本概念及常規時序路徑的組成

評論