若要查看跨時(shí)鐘域路徑分析報(bào)告,可選擇以下內(nèi)容之一來查看:

A, Reports > Timing > Report Clock Interaction

B, Flow Navigator > Synthesis > Report Clock Interaction

C, Flow Navigator > Implementation > Report Clock Interaction

D,Tcl command: report_clock_interaction -name clocks_1

如圖1所示,點(diǎn)擊Synthesis-->Report Clock Interaction.

圖1 Report Clock Interaction

跨時(shí)鐘域路徑分析報(bào)告分析從一個(gè)時(shí)鐘域(源時(shí)鐘)跨越到另一個(gè)時(shí)鐘域(目標(biāo)時(shí)鐘)的時(shí)序路徑。跨時(shí)鐘域路徑分析報(bào)告有助于識別可能存在數(shù)據(jù)丟失或亞穩(wěn)態(tài)問題的情況.

運(yùn)行“Report Clock Interaction”命令后,結(jié)果將在“時(shí)鐘交互”窗口中打開。如下圖2所示,時(shí)鐘交互報(bào)告顯示為時(shí)鐘域矩陣,源時(shí)鐘位于垂直軸,目標(biāo)時(shí)鐘位于水平軸。

圖2 跨時(shí)鐘域路徑分析報(bào)告

A,No Path --用黑色框來表示:沒有從源時(shí)鐘到目標(biāo)時(shí)鐘的定時(shí)路徑。在這種情況下,沒有時(shí)鐘交互,也沒有任何報(bào)告。

B,Timed -- 用綠色框來表示:源時(shí)鐘和目標(biāo)時(shí)鐘具有同步關(guān)系,并安全地被約束在一起。當(dāng)兩個(gè)時(shí)鐘具有共同的主時(shí)鐘和簡單的周期比時(shí),該狀態(tài)由定時(shí)引擎確定。

C,User Ignored Paths--用深藍(lán)色框來表示:用戶定義的假路徑或時(shí)鐘組約束涵蓋從源時(shí)鐘到目標(biāo)時(shí)鐘的所有路徑。

D,Partial False Path--用淡藍(lán)色框來表示:用戶定義的偽路徑約束覆蓋了從源時(shí)鐘到目標(biāo)時(shí)鐘的一些時(shí)序路徑,其中源時(shí)鐘和目標(biāo)時(shí)鐘具有同步關(guān)系。

E,Timed (Unsafe)--用紅色框來表示:源時(shí)鐘和目標(biāo)時(shí)鐘具有異步關(guān)系。在這種情況下,沒有共同的主時(shí)鐘或沒有可擴(kuò)展的時(shí)段。

F,Partial False Path (Unsafe)--用橘橙色框來表示:此類別與Timed(Unsafe)相同,只是由于偽路徑異常,從源時(shí)鐘到目標(biāo)時(shí)鐘的至少一條路徑被忽略。

G,Max Delay Datapath Only --用紫色框來表示:set_max_delay -datapath_only約束涵蓋從源時(shí)鐘到目標(biāo)時(shí)鐘的所有路徑。

Report_clock_interaction呈現(xiàn)的報(bào)告并不是根據(jù)時(shí)序約束生成的,但是和時(shí)序約束有關(guān),它反映出用戶定義的偽路徑。

例:以wavegen工程為示例,點(diǎn)擊Report Clock Interaction,如圖3所示。

圖3 wavegen跨時(shí)鐘域路徑分析報(bào)告

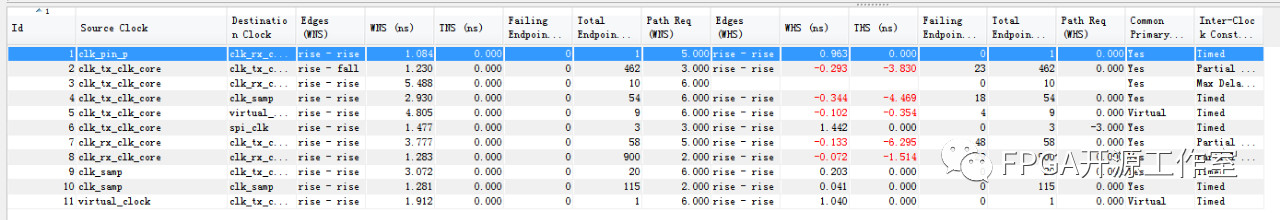

wavegen跨時(shí)鐘域路徑分析報(bào)上半部分已經(jīng)講過,下面來講下半部分,如圖4。

圖4 時(shí)鐘交互報(bào)告下半部分內(nèi)容

A,ID: 正在顯示的源/目標(biāo)時(shí)鐘對的數(shù)字ID。

B,Source Clock: 路徑源時(shí)鐘域。

C,Destination Clock: 路徑終端的時(shí)鐘域。

D,Edges (WNS):用于計(jì)算最大延遲分析(設(shè)置/恢復(fù))的最差裕度的時(shí)鐘邊緣。

E,WNS (Worst Negative Slack):為跨越指定時(shí)鐘域的各種路徑計(jì)算的最差裕度時(shí)間。負(fù)裕量時(shí)間表示路徑違反了所需的建立(或恢復(fù))時(shí)間的問題。

F,TNS (Total Negative Slack):屬于跨越指定時(shí)鐘域的路徑的所有端點(diǎn)的最差松弛違規(guī)的總和。

G,Failing Endpoints (TNS): 交叉路徑中的端點(diǎn)數(shù)量無法滿足時(shí)序要求。違規(guī)的總和對應(yīng)于TNS。

H,Total Endpoints (TNS):交叉路徑中端點(diǎn)的總數(shù)。

I,Path Req (WNS):定時(shí)路徑要求對應(yīng)于WNS列中報(bào)告的路徑。如果兩個(gè)時(shí)鐘中的至少一個(gè)時(shí)鐘的上升沿和下降沿都有效,則在任何時(shí)鐘對之間可能存在若干路徑要求,或者在兩個(gè)時(shí)鐘之間的路徑上應(yīng)用了一些時(shí)序異常。本專欄中報(bào)告的值并不總是最具挑戰(zhàn)性的要求。

J,Clock Pair Classification: 提供有關(guān)公共節(jié)點(diǎn)和時(shí)鐘對之間的公共周期的信息。從最高優(yōu)先級到最低優(yōu)先級:忽略,虛擬時(shí)鐘,無公共時(shí)鐘,無公共周期,部分公共節(jié)點(diǎn),無公共節(jié)點(diǎn)和清除。

K,Inter-Clock Constraints: 顯示源時(shí)鐘和目標(biāo)時(shí)鐘之間所有路徑的約束摘要。

編輯:hfy

-

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131799 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66887

發(fā)布評論請先 登錄

相關(guān)推薦

詳細(xì)解析vivado約束時(shí)序路徑分析問題

跨時(shí)鐘域的時(shí)鐘約束介紹

時(shí)序約束之時(shí)鐘組約束

ArcGIS的路徑分析

VIVADO從此開始高亞軍編著

調(diào)試FPGA跨時(shí)鐘域信號的經(jīng)驗(yàn)總結(jié)

Vivado時(shí)鐘分組約束的三類應(yīng)用

XDC路徑的鑒別、分析和約束方法

硬件設(shè)計(jì)中教你如何正確的約束時(shí)鐘

關(guān)于FPGA中跨時(shí)鐘域的問題分析

vivado多時(shí)鐘周期約束set_multicycle_path使用

vivado約束案例:跨時(shí)鐘域路徑分析報(bào)告

vivado約束案例:跨時(shí)鐘域路徑分析報(bào)告

評論