本文旨在讓無線電工程師熟悉一種現成的多用途軟件無線電(COTS SDR)平臺,該平臺可以縮短5G的開發時間。

COTS SDR傳統上一直用于軍用雷達和通信應用中,以獲得高性能和設計靈活性。最新的COTS SDR產品提供了含有集成化I/O、ARM處理器和大型FPGA的解決方案,還含有用于訪問、路由和處理數字數據的知識產權(IP)。這些特性,與優越的信號完整性、相位相干采樣和多信道收發機相結合,使得COTS SDR系統成為5G開發平臺的一種理想選擇。

COTS SDR的定義

為清晰起見,本文的每一節都劃分成了討論硬件、固件和軟件的各小節。硬件包括SDR印制電路板(PCB)和支持組件;固件包括用于邏輯和數字信號處理(DSP)功能的FPGA內部代碼;軟件是用固件控制FPGA并執行任意額外DSP功能的C代碼。

硬件

SDR取代了由RF濾波器、模擬下變頻器(即本振和混頻器)、帶通濾波器和解調器構成的傳統模擬系統(見圖1a)。這些固定的模擬系統局限于特定的功能,如AM或FM無線電。

圖1 傳統模擬通信接收機(a)與SDR接收機(b)、SDR發射機(c)的對比

而SDR利用了可編程DSP技術,可以靈活應對當今無線通信中日益增長的復雜性、精度和帶寬問題。要使用SDR,接收和發射功能都需要在天線和DSP之間進行數據轉換1。SDR接收機使用一只模數轉換器(ADC)將來自天線的RF信號轉換成數字采樣,并使用后續的DSP運算從信號中提取所需的信息(見圖1b)。SDR發射機接收要發射的數字信息,并執行必要的DSP運算以生成用于數模轉換器(DAC)的數字采樣,DAC的輸出驅動一只功放以傳送到天線(見圖1c)。因為這些無線電是軟件定義的,它們能夠在傳輸過程中在數微秒內用新的參數完成編程,或者通過從內部或外部存儲器簡單地加載新的固件實現針對不同目的的新配置。

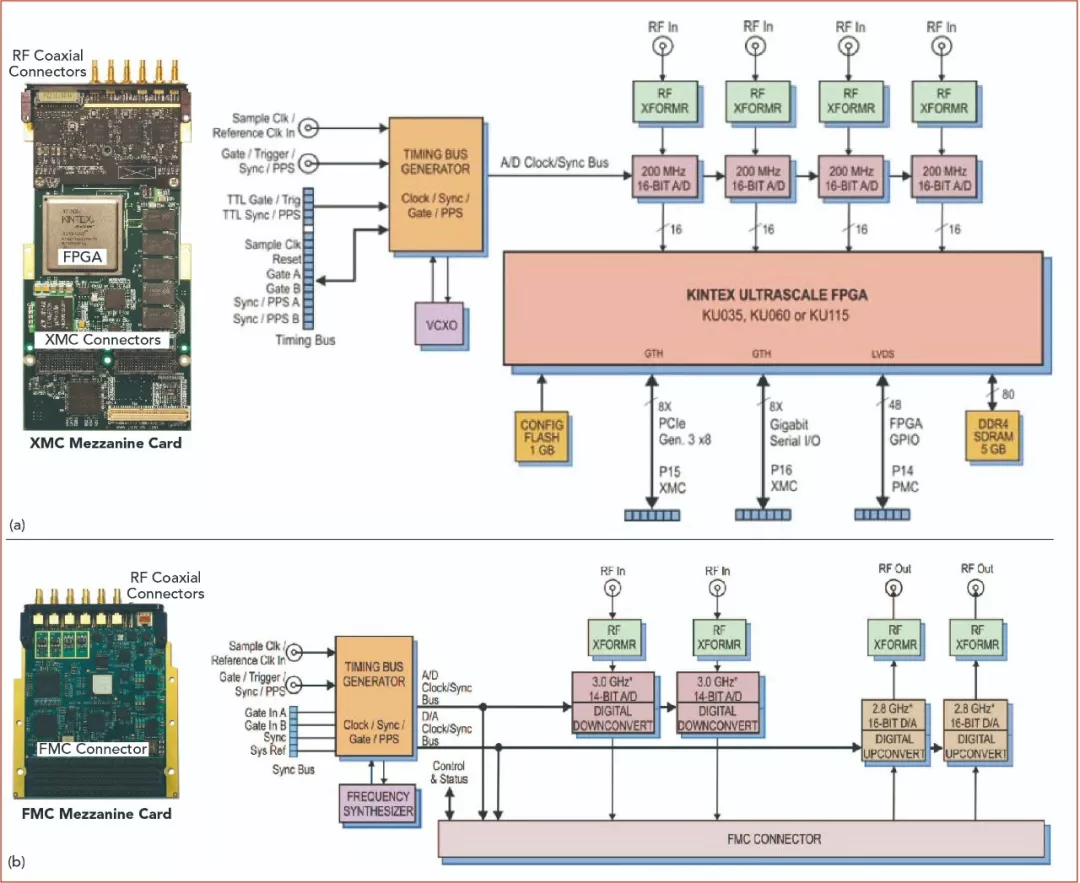

SDR通常是在一種稱之為“夾層卡(mezzanine card)”的特種PCB上實現的。當前一代是織構交變的夾層卡(XMC)或FPGA夾層卡(FMC)。圖2顯示了XMC和FMC及其相應的功能框圖。圖2a是有4個200MHz ADC通道的一塊XMC卡,圖2b是有2個3GHz ADC通道和2個2.8GHz DAC信道的FMC卡。每塊板都有一個用于可變采樣率的含多bit分數合成器的精確定時系統,定時系統被鎖定到一只板上的溫控晶振(OCXO)或一個參考輸入信號。這些定時系統通常接收來自網絡時間協議服務器或GPS接收機的外部同步信號,以滿足雷達或蜂窩系統的精確定時要求。ADC的相位相干采樣、FPGA DSP數據同步和DAC信號傳輸也需要精確定時。

圖2 XMC(a)、FMC(b)夾層卡及其功能框圖

XMC ADC有200 MSPS的最大采樣率,不用濾波即可捕獲100 MHz的Nyquist帶寬。數字無線電的一種常見技術是通過信號欠采樣獲得信道信息或中頻(IF)帶寬。欠采樣允許一只較低采樣率、較高動態范圍的ADC捕獲一個中心位于較高頻率的窄帶寬信號而不丟失信息。為了在這種情況下正確地工作,RF輸入通道和ADC必須容下這些較高頻率的信號。

在模數采樣之后,下一級通常是數字下變頻器(DDC),DDC進行頻率轉換和帶寬縮減。DDC通常是在FPGA中以IP固件實現的。

固件

FPGA是由未連接的邏輯、算法和信號處理的構件組成的,這些構件用IP固件配置以執行特定的功能。雖然對于極端的編程靈活性很理想,但固件開發復雜。為了簡化開發過程,一些COTS SDR制造商提供用于其電路板基本操作的FPGA IP。這通常包括了用于采集和傳輸數據的模擬和數字I/O功能,以及用于特定無線電功能的DSP IP,例如將數據傳送到系統的DDC、濾波器、信道化器和引擎。

DDC功能需要3個IP構件:數控振蕩器(NCO)本振、一個復數混頻器和多個數字濾波器,以取代傳統模擬無線電系統的功能(見圖1)。DDC的調諧級使用一個復數數字混頻器將感興趣的頻率轉換到基帶。由一只直接數字合成器(DDS) NCO驅動的一對乘法器,讓用戶能夠將接收機“調諧”到所需的頻率。采樣信號接著通過一只低通有限脈沖響應(FIR)濾波器來對信號進行1/10抽取以適應一個有限的信道帶寬。DDC的兩個主要優點是:1/10抽取帶來的更高的信噪比(SNR),以及調諧到信號窄帶中心頻率的能力。信號1/10抽取有效地降低了采樣率并減少了不相關的白噪聲,并且NCO能夠精確地數字調諧到單個Nyquist區內的一個特定載波頻率。

軟件

盡管廠商提供的FPGA IP可能滿足某個特定應用的指標,但系統的實現可能需要控制軟件來操作無線電。FPGA IP需要從一個軟件程序出發,跨過系統接口發出操作參數,軟件程序通常被寫成Windows或Linux環境下“C”可調用例程的電路板支持包(BSP)的函數。BSP包含庫函數和預編譯好的示例代碼,可以運行它們來測試電路板功能。其中一個功能是命令ADC捕獲數據并將其傳輸到FPGA,以便DDC中的進一步處理。處理后的數據可以存儲在存儲器中,或者傳輸到DAC以轉換回一個模擬信號并輸出以進行發射。這是使用BSP軟件庫函數和驅動程序開發的一個軟件程序的一例。如果用戶創建了任何新的FPGA IP,則必須編寫其它的控制軟件并將其納入BSP包中。

最新的COTS SDR技術

硬件

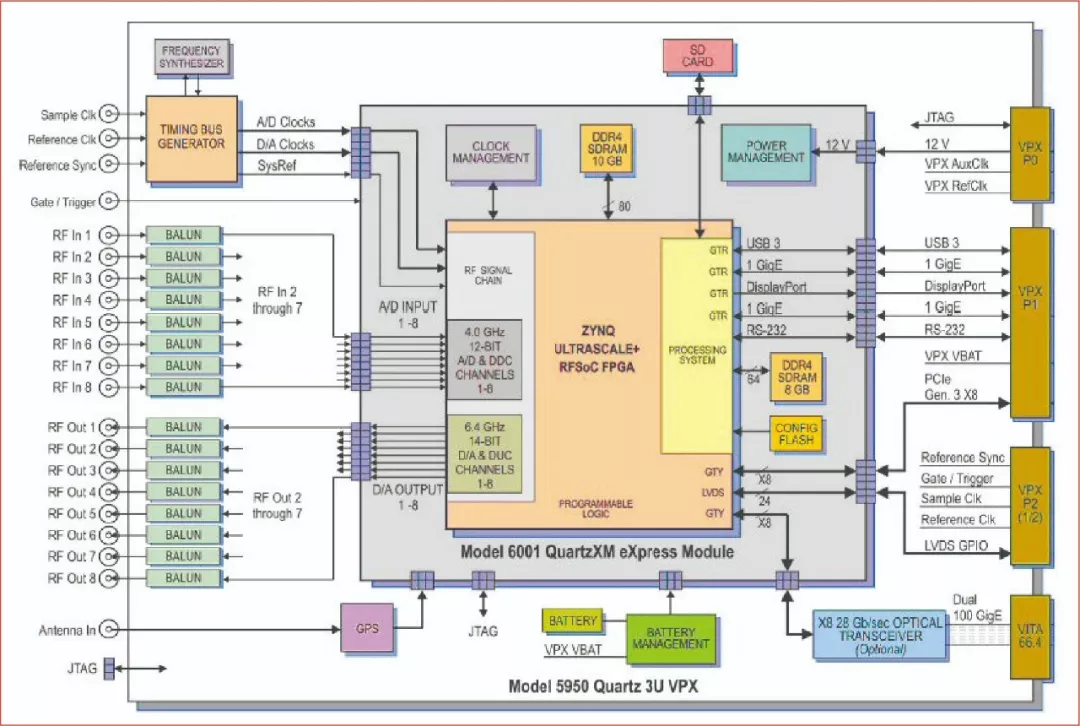

過去10年中,像Xilinx這樣的FPGA制造商一直在通過減小硅工藝節點的尺寸來改進技術,減少了器件的尺寸、重量和功率(SWaP)。2008年底,Xilinx Virtex-6系列采用了一種40 nm工藝制造,每個FPGA上有平均2000個DSP切片。2017年,Ultrascale系列采用了20 nm工藝,FPGA DSP切片增加到了約5500個。Xilinx最新的片上系統(SoC) RFSoC,在同一塊芯片上包含了FPGA結構和ARM處理器、ADC和DAC。16 nm工藝已經在每個器件上實現了超過4200個DSP切片、4個1.5 GHz的A53 ARM處理器、2個600 MHz的R5 ARM處理器、8個4 GHz的12位ADC和8個6.4 GHz的14位DAC。

圖3顯示了使用Xilinx RFSoC的一個COTS SDR實例的功能框圖,Xilinx RFSoC是Pentek公司5950 3U VPX板的核心元件。包含RFSoC的中心區域是可以插入一個3U VPX載體的全連接的模塊上系統(SoM)。同時,該器件可以像上一代FPGA一樣通過千兆位以太網端口進行控制,板上ARM處理器允許自主操作并具有與本地/外部網絡上的器件通信/控制的能力3。

圖3 Pentek公司基于Xilinx RFSoC的COTS SDR

固件

上一代FPGA使用如VeriLog或超高速集成電路描述語言(VHDL)的文本化硬件描述語言(HDL)編程。Xilinx的Vivado已包含了最新的符合AXI4標準的IP模塊。Xilinx的IP Integrator工具有代表HDL代碼的虛擬圖形化模塊,可以通過拖放布線相互連接。圖4顯示了一個VHDL編碼案例(見圖4a)以及相應的拖放圖形模塊(見圖4b)。這種更直觀的編程方式使得FPGA新手也能將表示FIR濾波器和DDC之類硬件的邏輯模塊連接在一起,以創建一個SDR。這種編程方法支持將廠商提供的硬件專用IP模塊與Xilinx的IP模塊快速集成,以創建一個可以工作的SDR。兩種類型的IP模塊可以組合在一起,以創建一個共用庫。

圖4 Xilinx的IP Integrator工具,顯示了VHDL編碼(a)和直觀的“拖放”圖形化模塊(b)

軟件

這些IP編程的進步,為COTS SDR廠商提供了創建一種單一BSP模塊的機會,該模塊與有某個場景中全部所需FPGA程序參數的一個IP模塊一致。一個案例是一種“時鐘控制BSP模塊”,它直接對應于一個“時鐘控制IP模塊”。

5G應用

最新一代的SDR技術正在改變游戲規則,COTS SDR制造商可以用它為開發5G無線電產品的工程師提供多通道SDR收發器。

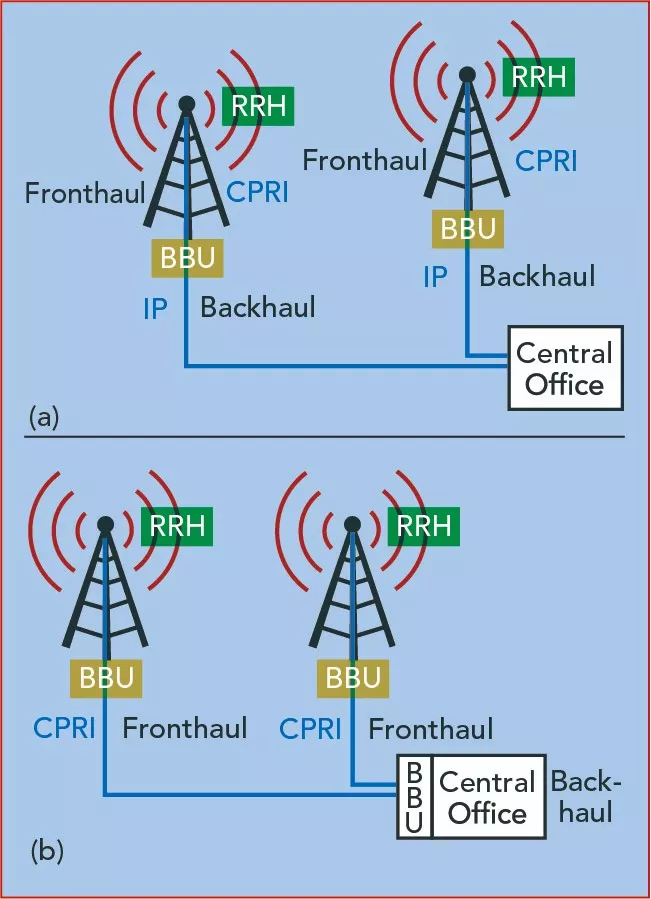

圖5圖示了分布式和集中式無線接入網絡,即D-RAN和C-RAN,之間的區別。通過LTE,傳統的D-RAN蜂窩站點正在被新的C-RAN取代,以提高數據傳輸效率、降低無線電成本。然而,由于RF路徑損耗的增大,5G的毫米波大規模MIMO架構需要分離,以使遠程無線電頭端(RRH)更靠近終端用戶。

圖5 分布式(a)和集中式(b)的RAN

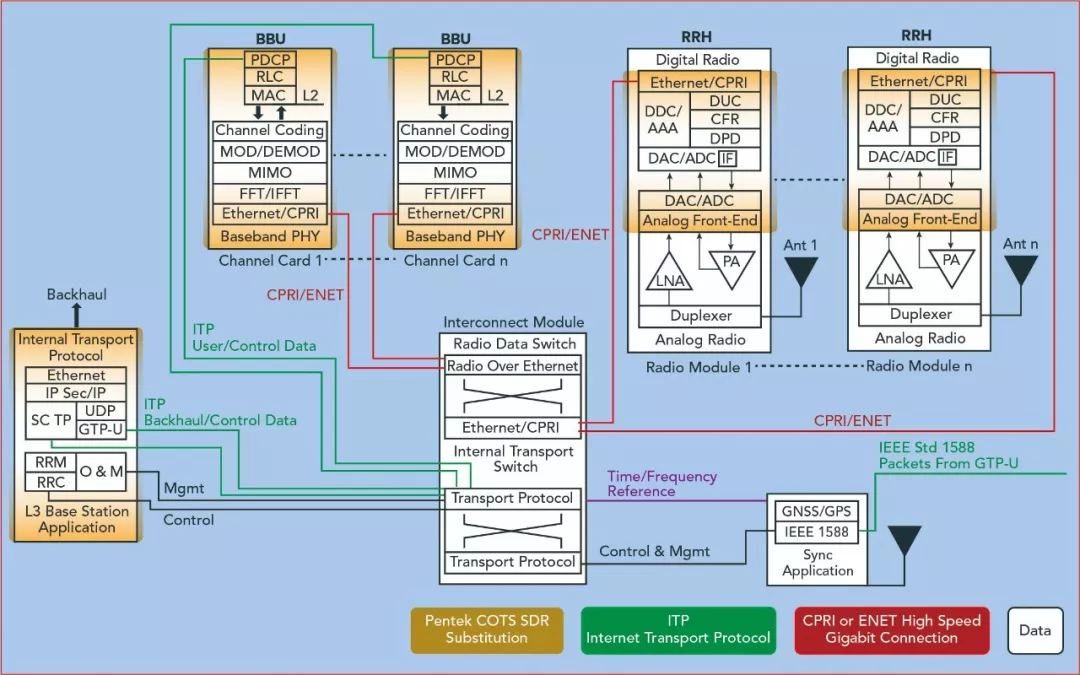

圖6示出了由基帶單元(BBU)、RRH、GPS時間/頻率源和一個互連模塊組成的一個C-RAN的功能框圖。突出顯示了幾個模塊,以提示COTS SDR的潛在應用。BBU位于一個中心局或“云中”的虛擬網絡之中,可以訪問用于回傳的多條光纖數據線。RRH位于更靠近最終用戶的外部位置。這個前傳連接案例中的BBU和RRH,根據系統要求,可以使用一個普通的公共無線電接口(CPRI)、開放的基站架構倡議(OBSAI)或標準的以太網連接。新的前傳概念,如可擴展的無線電接入網絡(xRAN)和開放無線電接入網絡(ORAN),未來將取代這些傳統的接口。

圖6 C-RAN的功能框圖,顯示了COTS SDR的用武之地

這些不同的傳輸模式選項與傳統的蜂窩、Verizon 5G技術論壇(5GTF)或3GPP 5G新無線電(NR)規范相結合配置,形成了一個復雜的異構網絡,需要一個靈活的開發平臺4。

硬件

圖7顯示了采用一塊COTS SDR板模擬C-RAN架構中的RRH的一個案例。含RRH的初始C-RAN的一部分示于圖7a中,包含了圖7b中的COTS SDR RRH。圖7a中框選的區域可以用圖7b所示的載波卡實現。定制的模塊化載波卡,包含了接收和發射放大器、一個GPS接收機和一個光電收發模塊。SoM內部包含了RFSoC以及用于電源管理、數據存儲和模擬/數字I/O的全部連接。通過一個雙工器將來自天線的輸入RF信號連接到接收低噪聲放大器,將其與功率放大器的高發送電平隔離,并將其連接到一個ADC通道。通過必要的IP,這個SoM和定制的載波組合件可以模擬初始RRH。

圖7 RRH的功能框圖(a),圖示了可以用一個COTS SDR實現的功能(b)

固件

一旦進入了FPGA架構,數字采樣將在DDC中進行1/10抽取、頻率選擇或調諧與濾波。DDC輸出的采樣,可以流向功率計模塊進行測量,并在閾值檢測器IP模塊中進行分類。這些處理過的采樣可以流向ARM處理器,以便在用于中繼的數字上變頻器(DUC)中進行上變頻前的波峰因數降低和數字預失真運算。DUC與DDC相反,采用頻率轉換和插值替代1/10抽取。數字化的I/Q采樣數據在數字無線電中打包,通過一個無線電數據交換機傳輸到BBU。由于信道和數據傳輸協議的多樣化,必須了解信號的最大數據吞吐量并確保充足的網絡容量。

軟件

根據所需的控制等級,可以為新的IP和ARM處理器、或ARM處理器與FPGA創建BSP例程,編程實現自主運行。

結論

本文的目的是使傳統無線電工程師熟悉COTS SDR供應商提供的最新硬件、固件、軟件和設計工具,表明SDR可用作5G開發的平臺。這些SDR平臺提供了卓越的信號完整性、高測試重復性和模塊化組件,可根據不斷變化的5G設計要求進行調整。5G的演進將需要實驗和優化的多輪開發迭代,采用COTS SDR系統作為起點將縮短產品上市時間。

編輯:hfy

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

Xilinx

+關注

關注

71文章

2171瀏覽量

122129

發布評論請先 登錄

相關推薦

多用途軟件無線電系統的5G設計解決方案

多用途軟件無線電系統的5G設計解決方案

評論