一、HDL的概念和特征

HDL,Hard Discrimination Language的縮寫,翻譯過來就是硬件描述語言。那么什么是硬件描述語言呢?為什么不叫硬件設計語言呢?硬件描述語言,顧名思義就是描述硬件的語言,它用文本的形式來描述電子系統硬件結構和行為,是一種用形式化方法來描述數字電路和系統的語言。正是因為如此,硬件與軟件不一樣,他不像軟件,你某天突發奇想,想實現某個的界面,搞搞代碼就OK了。硬件它是由實實在在的物理器件搭載而成,用抽象的語言怎么可能弄出一個電路來呢?

一門語言,總有那么一些特殊之處,不然人家就不認,HDL主要有下面一些特征:

①HDL語言既包括一些高級程序設計語言的結構形式,同時也兼顧描述硬件線路連接的具體結構。

②通過使用結構級描述,可以在不同的抽象層次描述設計。HDL語言采用自頂向下的數字電路設計方法。

③HDL語言是并行處理的,具有同一時刻執行多任務的能力,這個和高級設計語言串行執行的特征是不同的。

④HDL語言具有時序的概念。一般的高級語言沒有時序的概念,但在硬件電路中從輸入到輸出是有延時存在的,為了描述這一特征,需要引入時延的概念。因此HDL語言不僅可以描述電路的功能,還可以描述電路的時序。

二、Verilog HDL的發展歷史

1983年,Gateway Gesign Automation 硬件描述語言公司的Philip Moorby這個人(帶領團隊)首創了Verilog HDL。

1984~1986年,Moorby設計出第一個關于VerilogHDL的仿真器。

1987年,synopsys公司使用verilog HDL作為綜合工具的輸入。

1989年,cadence公司收購Gateway公司,因此verilog也成為的cadence的囊中之物。

1990年初,cadence公開發布verilogHDL,后來open verilog HDL international組織(由verilog使用者和計算機輔助工程供應商組成)指定標準。

1993年,幾乎所有的ASIC廠商都支持verilogHDL,OVI推出了verilog HDL 2.0版本。接著IEEE把verilog HDL 2.0 作為IEEE標準的提案。

1995年12月,IEEE制定了Verilog HDL的標準IEEE 1364--1995。

2000年,發展為IEEE 1364--2000.

最后,在2005年,verilog 的標準停止在了IEEE 1364--2005。05年以后,與verilog有關的system verilog了,verilog的標準就不再更新了,而是融入到system verilog中。我們現在用的verilog HDL,都是按照05年及其以前的標準制定的語法。

三、Verilog HDL 的描述能力

在前面已經講到,Verilog HDL可以在不同的的抽象層次進行描述電路下面的它們的具體層次分類:

描述級別抽象級別 功能描述 物理模型

行為級系統級用語言提供的高級結構實現所設計模塊外部性能的模型芯片、電路板和物理劃分的子模塊

算法級用語言提供的高級功能實現算法運行的行為部件之間的物理連接,電路板

RTL級描述數據如何在寄存器之間流動和如何處理、控制這些數據流動的模型芯片、宏單元

邏輯級門級描述邏輯門之間的連接模型標準單元布圖

電路級開關級描述器件中三極管和存儲節點以及它們之間連接的模型晶體管布圖

在這里說明一下,行為級描述中的系統級和算法級描述很少用Verilog HDL進行描述,而是用matlab 或者C++進行描述,邏輯級和電路級也幾乎不用Verilog HDL進行描述。真正用到的是寄存器傳輸級(RTL級),因此在描述RTL級的時候,Verilog HDL根據設計和語法的情況,有可以分為行為描述和結構描述,這個在以后的語法中會說到。

四、Verilog HDL的應用

Verilog HDL的一個大致情況以及說明了,那么Verilog HDL主要有哪些應用呢?毫無疑問,就是用它來進行數字邏輯設計了,只要是在FPGA(field programer gate array ,現場可編程邏輯門陣列)的邏輯設計和數字集成電路設計前端的邏輯設計中用到。下面就來談談FPGA的設計流程和數字IC設計的流程吧。

五、FPGA設計流程

這個設計流程我就不記錄,畢竟有一部分是跟后面的數字IC設計流程重復。

六、數字IC設計與流程概述

在開篇的時候,我先講一下IC設計分類跟設計流程,提前聲明一下,由于本人水平有限,加上沒有完全親身體驗過從設計規劃到工藝制造這一完整的設計流程,只是知道這一流程的某些步驟,因此本篇的設計流程是我根據我的一些實踐體會、一些文獻內容、一些網絡資料、與一些工程師的交談等得出的一個大體流程,這個流程也許跟一些公司的流程不一樣,如果有錯誤的地方,希望指出。本篇我主要記錄的內容是IC設計的分類跟IC設計的流程概述。沒錯,就只有這些內容,畢竟我比較垃圾,“狗嘴里吐不出象牙”,現在我們就看看這IC吧。

分類:

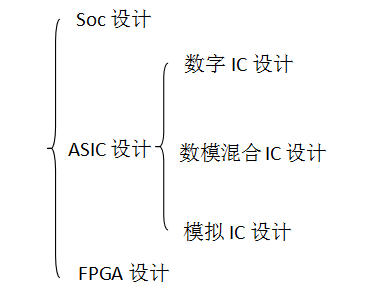

IC也就是集成電路,通俗的講也就是芯片了。我覺得芯片設計在現在來看,主要有Soc芯片設計、ASIC設計、FPGA設計,如下圖所示:

也許有人就出來抬杠了,說:“你這是在扯淡,不是還有功率IC這些分類么?!”。我這里是說主要,是根據大體的方向分的,功率IC嘛。。.可以算是數模混合里面,也有可以是模擬的里面,看你怎么做了。總之,大體分類就是這么一個情況了。

這里著重強調一下,我以后所說的,包括流程啊,設計概述啊,還是什么亂七八糟的,都是關于ASIC設計里面的,有時間我們再來掰扯掰扯SoC跟FPGA設計的問題,畢竟ASIC在向著SoC發展,此外FPGA也是不可忽略的一塊領域。模擬那些問題嘛,我不是很感興趣,就不在這里記載了,這里涉及的都是數字設計相關的。當然,這只是有時間哈,沒有時間,誰想理這些東西,還是好好地弄好自己的方向吧(我自己定下的方向是:數字IC(系統)設計,數字信號處理相關,至于詳細的方向嘛,可能是通信,也可能是圖像,也可能是音頻等等,到時候再說吧,現在每個領域都涉及一點再說。。。)。

廢話不多少,現在來看一下數字IC的設計流程吧。

流程:

設計之前——項目策劃

在設計之前,需要知道自己為什么要設計這么一個數字IC(系統)。因此在設計之前要進行項目策劃。

項目策劃呢,大概就是這么一個過程,首先市場部門(營銷部門)等有關部門(“有關”這個官方詞語,還是很好用的,哈哈)根據經濟狀況,對市場進行調研或者反饋,得出市場的需求;或者一些先進的有關領導,注意到某些比較現在或者將來發展比較好領域,決定要開發這么各個產品。于是開會,決定這個東西可以賺一筆的時候,就讓技術人員跟市場部的進行研究、論證,最后又開一次大會,決定:“好,就這么干!”。于是,一份項目策劃書就出來了。這個項目策劃書一出來,螞蚱都得在這一根繩上爬了。項目策劃書里面有啥內容呢,其實。。.我也不知道,md我又不是產品經理、或者什么部門老大,我怎么知道,但是,有小到消息說,里面有:對項目時間及資源的描述;對設計項目的目標描述;風險和成本的估計分析等(具體我也不清楚,我就一硅農,哈哈哈哈)。

OK,項目策劃完成了,下面就開始進行設計了。

設計ing——技術人員的活

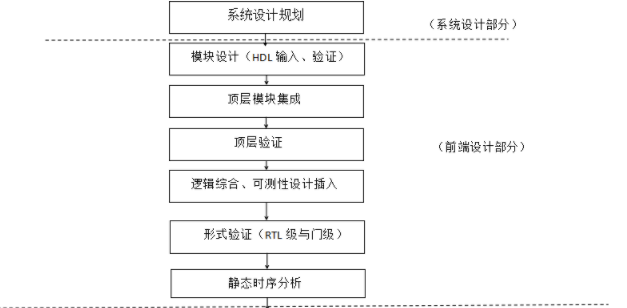

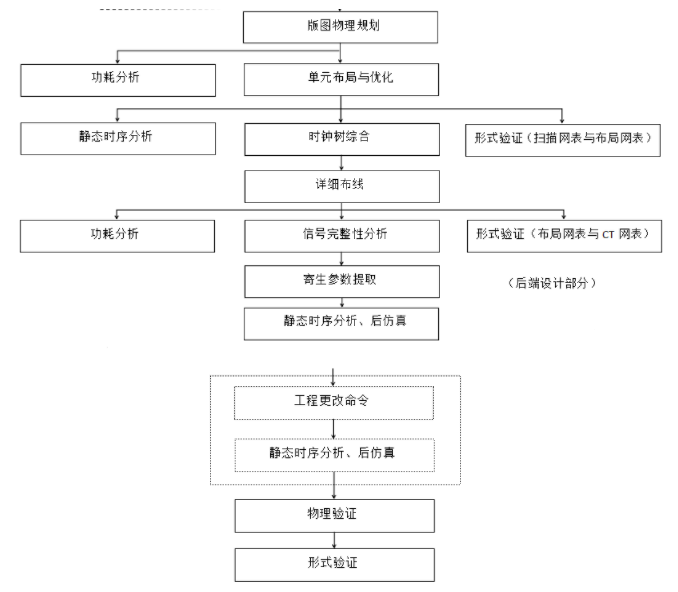

設計流程大概有下面這些步驟:系統總體規劃、模塊設計、頂層模塊集成、頂層功能模塊驗證、邏輯綜合、形式驗證、靜態時序分析、可測性設計插入、芯片版圖物理規劃、功耗分析、單元布局與優化、時鐘樹綜合、布線、信號完整性分析、寄生參數提取、后仿真、工程更改命令、物理驗證。用下圖表示流程可能更清晰一點:

z

簡單地,可以分成系統設計,前端設計,后端設計。前端設計主要是輸入、驗證、綜合;后端設計主要是APR(自動布局布線,也就是從floorplan→布局→布線)。當然,這些流程也不是完全順序操作下去的,此外,全部的數字IC系統設計也未必按照這個流程跑,當有錯的時候,也是需要返回去進修改的,這里我就不返回去了。下面是相關步驟的概述,每一部分包含的內容至少有一個章,這里僅僅是簡單介紹。

1、系統總體規劃(system global plan)

項目策劃完成,領導開始讓工人們干活。首先就是高級工人,系統算法工程師,根據要求,搞一堆算法來,看看哪一個比較符合老大的項目策劃書要求。系統架構工程師根據系統算法工程師提出的算法,想想怎么用詳細的特定功能硬件實現,發現算法的硬件實現比較坑爹,就去找系統算法工程師理論。然后這兩類系統工程師通過對系統的方案、設計、仿真跟各種撕逼之后(他們撕逼的內容聽說有這些:浮點數算法,軟硬件劃分,IC設計中數據的定點表示,定點算法表示,結構的并行性跟流水線,存儲器分配,還有其他等。。.),達到平衡點(就是算法能夠較好地使用良好架構跟電路的實現),一份系統設計規格書就出來了。至于系統設計規格書里面具體有什么,我們就不展開說明了。

2、模塊設計(module design)

高級的系統工程師完畢,就到我們這些螺絲釘,進行模塊設計了。模塊設計也還是分等級,人家有高級數字IC設計工程師。而真正專門寫模塊的呢,就是螺絲釘級的一般數字IC工程師,別稱”硅農”。。.透露一下,系統設計規格書里面就有進行模塊劃分的內容,這里就是進行設計模塊了。一般,模塊設計使用HDL語言進行輸入,輸入工具使用GVIM。寫完一個模塊了,(進行代碼設計規則檢查,這個靠檢查工具來工作了,檢查工具可以檢測幾百個設計規則,檢查的內容主要有:標準規則檢查、可重用性檢查、競爭條件檢查、可綜合性、可測試性、時鐘域、結構性、加速策略、用戶自定義的規則等),然后進行功能驗證,就是驗證你寫的這個電路是不是符合模塊的功能要求,使用的工具是synopsys的VCS。仿真通過之后,就可以把模塊提交上去了給上層負責管理頂層模塊的高級數字IC工程師了。有興趣的話,可以自己綜合一下自己負責維護的模塊。

3、頂層模塊集成(top level integration)

底層的的模塊寫完之后,開始進行模塊集成,新模塊跟復用的舊模塊集成,I/O,時鐘等模塊的基礎,把系統集成起來,構成整個系統后,就完成了系統模塊的集成。

4、頂層功能模塊驗證(top level verification)

頂層模塊集成完畢后,檢測集成之后模塊是否還能正常工作,驗證功能是否正確,各項指標是否完好等等。這里,數字IC驗證工程師就可以放大招了。驗證使用VCS進行。驗證是一門雜活哇,各種方法學UVM之類的,還是我們硅農的小模塊驗證比較好。

5、邏輯綜合(logic synthesis)

邏輯綜合就是通過EDA工具把頂層的HDL模塊,在一定的約束情況下,映射到制造廠家標準單元庫元件的門級電路的過程。通過這個步驟,從HDL代碼,得到了門級網表,也就是得到了電路。具體的有關綜合的知識將在后文聯合synopsys的綜合工具design compiler進行記載。

6、形式驗證(formal verification)

形式驗證,就是對設計過程中不同階段的輸出結果進行邏輯功能一致性的對比,根據電路的結構,判斷兩個設計在邏輯功能上是否對等。有關形式驗證的知識將在后文中記載。

7、靜態時序分析(static time analysis,STA)

靜態時序分析,就是通過EDA工具,提取電路中所以路徑的延遲信息進行分析,計算出信號在路徑上的延時,檢查時序是否滿足設定的時序約束要求。靜態時序分析將在后文中結合synopsys的PT工具進行記載。

8、可測性設計插入(design for test,DFT)

可測性設計是指:在進行電路的前端設計時,就預先規劃、設計出如何在樣片中進行電路的測試方案和辦法,并通過邏輯綜合過程完成芯片內部專用測試結構的插入,一遍在芯片形成后能按照預先制定的方案進行相應的電路功能測試的一種設計方法。也就是進行可測性設計,就是在原有的電路中插入專門測試的電路(插入電路)。

上面的部分基本前端設計的部分,是我后面內容主要涉及的內容,后面的主要是后端設計的部分,這后端設計就是專業名詞特別多,而且還中英互聯,很少讓人討厭。所以后端的部分知識按照常規來介紹了

9、版圖物理規劃(floor-plan)

這一步驟主要是通過對EDA工具進行輸入標準單元庫、標準I/O庫、綜合后的網表、各種約束文件等,規劃好讓EDA工具完成各模塊的位置擺放、電源網絡的設定、I/O信號出口位置、同時確定面積、封裝、工藝、噪聲、負載能力等參數。

10、功耗分析(power analysis)

在完成版圖物理規劃后,需要進行功耗分析。功耗分析可以確定電源引腳的位置和電源線的寬度是否滿足要求。對整個版圖進功耗分析,即要進行動態功耗分析跟靜態功耗分析,找出主要的功耗單元或者模塊,以供優化。

11、單元布局與優化(placement & optimistic)

根據floor-plan中的布局規劃,擺放網表中調用的所以標準單元,EDA工具自動對時序約束、布線面積、布線擁堵等綜合考慮標準單元的擺放,從而依靠EDA工具完成電路的布局設計跟優化。

EDA主要進行自動對floor-plan的具體工作的標準單元實現:確定各功能模塊的位置和整個芯片的尺寸;確定I/O buffer 的位置,定義電源和地PAD的位置;定義各種物理的組、區域或模塊,對大的宏單元進行放置;設計整個供電網絡,基于電勢降和電遷移進行拓撲優化;通過布局調整、約束修改、屬性添加、密度、高速信號分析等手段達到優化的目的。

12、時鐘樹綜合(clock tree synthesis,CTS)

要了解時鐘樹綜合,那么就得中斷什么是時鐘樹。時鐘樹就是分布在芯片內部的的寄存器跟數字的驅動電流構成的一種樹狀結構的電路。時鐘樹綜合就是EDA工具按照約束,插入buffer,使時鐘的源頭(時鐘根節點)到達各個需要時鐘驅動的器件(各葉子節點,如觸發器)的時間基本一致的過程。時鐘樹綜合通常使用EDA工具自動進行。

13、布線(routing)

布線就是完成模塊、節點的相互連線。EDA工具可以分成全局布線和詳細布線。一般情況下先使用EDA工具布線,然后在人工干預的情況下局部自動或者手工進行連接一些比較關鍵地連線,進行修復連接上的問題和時序約束上的問題。注意,關鍵路勁跟時鐘上的連接線要盡量最先連接,以免繞線,導致時序問題。

14、信號完整性分析(signal competition analysis)

信號完整性分析是通常是進行分析噪聲。隨著器件尺寸的下降,器件的供電電壓、噪聲容限均下降。也就是說,也許由于某一根導線可能電阻過大,帶來的壓降過大,導致器件的供電電壓達不到而不能正常工作等等的一系列問題。對這些問題進行分析,是信號完整分析的一部分。

15、寄生參數提取(parasitic extraction)

根據布線完成得版圖提前RC(電阻電容)參數文件。對EDA工具輸入相應的工藝參數(廠家提供)后,EDA工具根據這些參數和版圖實際幾何形體的面積計算出RC值,然后通過存儲從而提取出RC參數。提取出來的RC參數,可以直接用于靜態時序分析,也可以在計算出相應的路徑延時時,用于反標功能后仿真。

16、后仿真(post-layout simulation)

后仿真也叫門級仿真、時序仿真、帶反標的仿真。它是通過采用外部激勵和布局布線后產生的標準延時文件(*.sdf),對布局布線后的門級電路網表進行功能和時序驗證,來檢驗門級電路是否符合功能要求。

17、工程更改命令(engineering change order,ECO)

在設計的最后階段發現個別路勁有時序問題或者邏輯錯誤時,通過芯片內部專門留下的寄存器跟組合邏輯,對設計部分進行必要的小范圍的修改和重新連線。

ECO在是在網表上做文章,在非必須的情況下(如時間充足,人員充足),不要進行ECO。

18、物理驗證(physical verification)

物理驗證主要是一個對版圖的設計結果是否預定要求而進行的驗證過程。

首先是通過DRC(design rule check,設計規則檢查)對版圖設計中的約束違規情況進行檢查,以保證各層版圖都符合設計的要求。然后是進行LVS(layout vs. Schematic,版圖網表與電路原理圖比較),進行版圖網表跟原始電路圖的一致性對比檢查,即通過版圖寄生參數提取工具得到一個有版圖寄生參數的電路圖,將它跟原理電路圖進行比較,以確保版圖設計與原要求的電路圖的邏輯功能一致性。

此外還有一些需要進行ERC,即電氣規則檢查。這里不詳述了。

編輯:hfy

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606059 -

IC設計

+關注

關注

38文章

1302瀏覽量

104290 -

Verilog HDL

+關注

關注

17文章

126瀏覽量

50478

發布評論請先 登錄

相關推薦

Verilog HDL應用及數字IC設計與流程概述

Verilog HDL應用及數字IC設計與流程概述

評論