引言

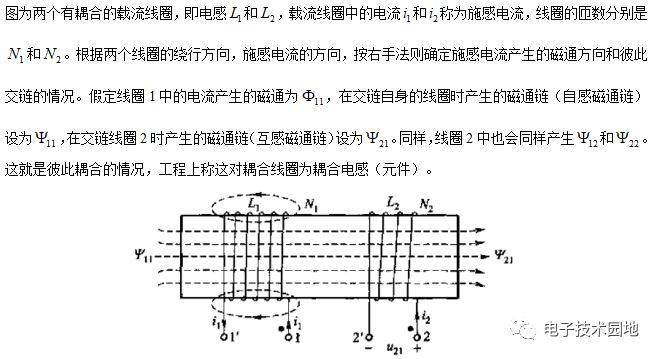

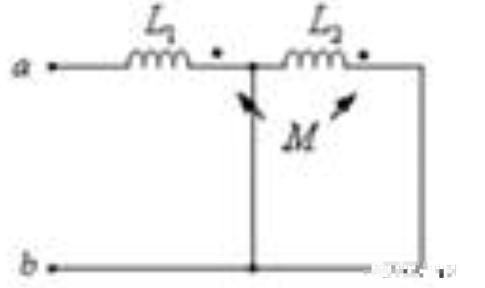

耦合電感常用于多相電源拓撲,充分利用其相間磁耦合電流紋波相抵消的技術優勢。使用普通分立式電感時,一般只在多相降壓轉換器輸出抵消電流紋波。當這些電感通過磁耦合時,電流紋波抵消作用到所有電路元件:MOSFET、電感線圈、PCB走線[1-6] 。所以,所有相開關操作僅影響到單相,從而減小電流紋波幅值、頻率倍增。減小電流波形的RMS有助于提高電源轉換效率,或減小磁元件、獲得較快的瞬態響應,并進而減小輸出電容需求。

耦合電感與傳統電感設計的對比

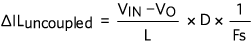

傳統非耦合降壓轉換器的峰-峰電流紋波可表示為式1,其中VIN為輸入電壓,VO為輸出電壓,L為電感,D為占空比(對于降壓轉換器,D = VO/VIN),Fs為開關頻率。

(式1)

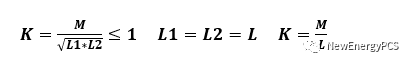

對于帶有耦合電感的降壓轉換器,當D IN = 12V轉換為核電壓(0.5V至2.5V)。通過式2,很容易看到電路和磁元件參數對電流紋波抵消的影響。

(式2)

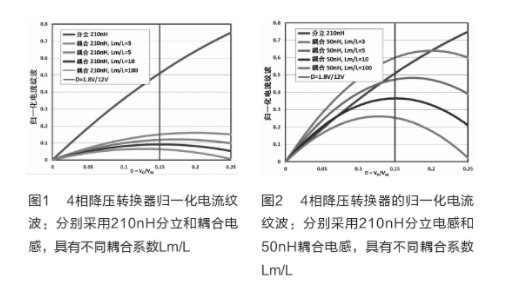

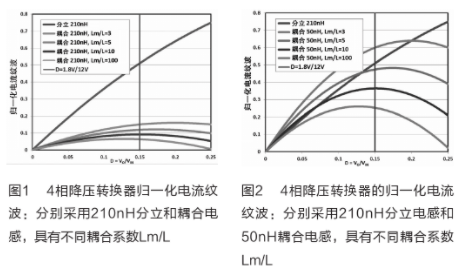

與式1相比,式2中的附加乘數取決于應用條件,隨占空比、耦合系數以及耦合相數變化。圖1所示為分別采用210nH分立或耦合電感的4相降壓轉換器的歸一化電流紋波。用 電流紋波對電流紋波進行歸一化,即D = 0.5時分立電感的紋波(所以D = 0.5時,分立電感的歸一化電流紋波為1)。如曲線所示,對于12V轉換為1.8V的典型應用,D = 0.15。

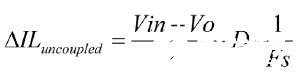

從圖1可以看出,所有電源電路中由于采用耦合電感使得紋波電流大幅抵消。注意,在有些占空比下,電流紋波抵消明顯大于D = 0.15的情況。耦合電感的幾條曲線說明了耦合系數Lm/L的影響:Lm/L = 3 - 7范圍內的耦合比較實用,有些Lm/L值比較理想化、不太現實,例如10和100。如果采用分立電感的初始設計比較合理,電流紋波可以接受,那么采用耦合電感可以減小電感值并達到D = 0.15下同等的電流紋波。這種條件下,50nH/相的耦合電感可提供與210nH分立電感同等的電流紋波,如圖2所示。

相同的峰-峰電流紋波對應同等的電流波形RMS,使得所有支路的導通損耗和開關損耗相近,效率也相近。帶來的優勢是:50nH電感的瞬態性能比210nH提高4倍以上,而且,您可以徹底脫離大數值、不可靠、價格昂貴且體積較大的輸出電容,只是留下本已存在的高性能陶瓷電容。

注意,對于具有快速瞬態響應的設計,陶瓷電容總是必需的。因為只有低ESR和ESL的電容能夠滿足負載快速變化時的瞬態要求。通常增加大電容來解決分立電感的低電流擺率和相關的能量儲存問題。如果是采用耦合電感,僅僅陶瓷電容就足以滿足多數要求。

耦合電感的優勢不止于此。耦合電感設計為負耦合,當各相電流相等時,來自所有線圈的互感磁通彼此抵消。后一種情況通常出現在多相應用,尤其是采用電流模式控制的架構。只有漏磁通將能量儲存在耦合電感中,所以圖2所示例子的能量儲存對應于50nH/相(而非210nH/相)。這意味著,與分立式電感相比,耦合電感小得多,并且/或者具有較高的額定飽和電流。

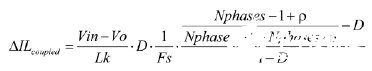

針對將12V轉1V、為微處理器供電的典型4相方案,對兩種磁元件配置進行比較:商用的高效分立電感FP1308R3-R21-R與 50nH耦合電感CL1108-4-50TR-R,網上提供相應的數據資料[7-8]。假設分立電感在PCB的 距離為0.5mm,分立電感所占電路板面積大約為722mm2;耦合電感則只需大約396mm,已經能夠提供好得多的性能,如圖3所示。同時,分立電感在室溫+25℃時Is = 80A (無疑在較高溫度下更差),而耦合電感在+105℃時的飽和電流高于110A/相。可實現占位面積減小1.8倍以上,飽和電流提高1.5倍以上。

為了更好地體會耦合電感的尺寸優勢,可考慮在該4相方案中使用分立電感(物理尺寸更窄),但這樣的電感會降低額定飽和電流,或者電感值比210nH小。后一種情況將進而增大電流紋波、降低效率。

假設為理想耦合(即Lm/Lk極大),可簡化式2用來降低磁耦合電流紋波的乘數,將式2簡化為式3[3]。可以明顯看出這種耦合方案的優勢與Nphases的關系,當然在很大程度上也與占空比相關。更確切地說,針對不同應用,可以從占空比D = 0或D = 1區域獲取更大優勢。

(式3)

現在介紹利用耦合電感優勢的方法。耦合電感電流紋波抵消的式2可歸納為式4。

(式4)

使用較熟悉、較方便的參數,可根據參考文獻得出式4的品質因數(FOM)9。

(式5)

式5表示FOM適用于特定的占空比D范圍:

,其中系數k在

范圍內變化。

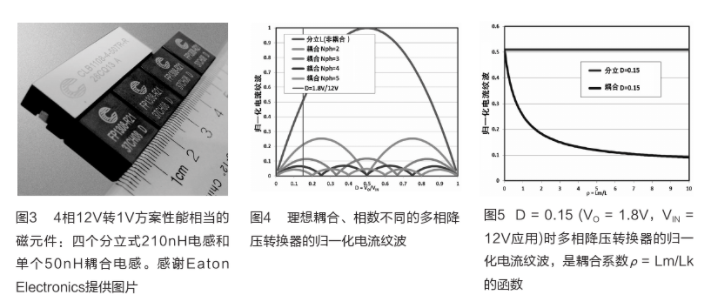

圖4所示為整個占空比范圍內,不同相數下電流紋波的減小。繪制電流紋波曲線時,假設為理想耦合,L值相同。很明顯,增加耦合相數比較有利。

注意,對于采用分立元件的一般方案,針對給定輸出電流正確增加相數是一種在成本、尺寸方面都很有優勢的方法。對于在單芯片集成多個開關相的商用化集成方案,也非常具有吸引力。

圖4也標記了一個特殊的占空比:D = 0.15,對應于實際例子VO = 1.8V,VIN = 12V。該條件繪制成圖5所示曲線,表明耦合系數ρ = Lm/Lk對抵消電流紋波的影響。觀察圖4,D = 0.15時,分立電感的歸一化電流紋波大約為0.5,如圖5紅色曲線所示。相同條件下,如果耦合系數非常低,4相耦合電感具有相同的電流紋波;隨著耦合系數增大,電流紋波大幅減小,見圖5。注意,電流紋波在開始下降非常快,在耦合系數較大時達到平坦,建議耦合系數大約為3至5。利用這種方法,可實現 的電流紋波抵消。

設計要點

假設我們從采用分立電感的多相降壓轉換器開始設計,目標是利用耦合電感提高系統性能。如果當前的分立電感設計具有合理的電流紋波,轉換器效率也滿足客戶要求。對于耦合系數相對實用的4相降壓轉換器,從式5得到的預期FOM曲線如圖6所示。

觀察圖6,D確定在大約0.15,可將FOM = 4作為設計目標。圖7所示為得到的電流紋波:紅色曲線表示分立電感L的初始電流紋波;兩條曲線表示不同耦合系數下L的電流紋波; 兩條曲線表示L/4時的電流紋波。與預期一樣,D大約為0.15時,分立電感L和耦合電感L/FOM = L/4的電流紋波相當。

注意,根據應用的不同,目標占空比范圍可能不同,所選FOM可能高于D≈0.15時的數值。對于典型設計,選擇FOM = 4,其中利用50nH耦合電感代替210nH高效分立電感,如圖3所示。正如預期,小得多的電感值必須滿足飽和電流指標要求,所以耦合電感尺寸比傳統方案小得多。選項FOM = 4也使瞬態條件下的電流擺率提高4倍,所以輸出電容可減小大約4倍。

上述設計過程可應用到任意相數。注意,所選FOM不一定單單為了改善瞬態性能。根據應用條件和客戶要求優先級的不同,可折中選擇FOM,例如直接減小電流紋波,進而降低電路各處的傳導損耗。例如,選擇FOM = 4時,可以只將電感值降低2.6倍(同時也減小了提高的瞬態性能),使電流紋波減小、效率提高1.5倍。

隨著耦合電感進入不同的電源應用領域,毫無疑問將有許多不同客戶從該專有技術中受益。

責任編輯 LK

-

轉換器

+關注

關注

27文章

8743瀏覽量

148040 -

電源電路

+關注

關注

48文章

1001瀏覽量

65320 -

耦合電感

+關注

關注

0文章

77瀏覽量

20162

發布評論請先 登錄

相關推薦

電源設計小貼士:松散耦合電感和緊密耦合電感構建電源

電源設計小貼士:SEPIC耦合電感

耦合電感的技術優勢及與傳統電感設計的對比

耦合電感與傳統電感相比有什么優勢

耦合電感與傳統電感相比有什么優勢

評論