挑戰和響應認證需要 MAC 發起者和 MAC 接收者根據隱藏的秘密和公共數據計算消息認證代碼。發起者通常是 SHA-1 身份驗證者或帶有 SHA-1 引擎的受保護內存。MAC 接收方是應用程序的主機處理器。本應用筆記介紹了 DSSHA1 可合成 SHA-1 協處理器,它可以在專用集成電路 (ASIC) 或現場可編程門陣列 (FPGA) 中實現,作為 DS2460 SHA-1 協處理器或基于微處理器的實現的替代方案.

質詢和響應身份驗證基于消息身份驗證代碼 (MAC) 的計算。該方法涉及兩個實體,即 MAC 發起者和 MAC 接收者,它們共享一個隱藏的秘密。為了證明 MAC 發起者的真實性,MAC 接收者生成一個隨機數并將其作為挑戰發送給發起者。然后,MAC 發起者必須根據秘密、消息和質詢計算新的 MAC,并將其發送回接收者。如果發起者證明能夠為任何挑戰生成有效的 MAC,則可以非常確定它知道該秘密,因此可以被認為是真實的。SHA-1 是一種經過徹底審查和國際認證的計算消息身份驗證代碼的算法,它是由美國國家標準與技術研究院 (NIST) 開發的。

Maxim 制造了一系列采用 SHA-1 算法的認證設備。教程 3675“通過安全認證保護研發投資”以安全存儲器和 DS2460 SHA-1 協處理器的形式解釋了 Maxim 認證解決方案。DSSHA1 存儲器映射 SHA-1 協處理器允許在專用集成電路 (ASIC) 或現場可編程門陣列 (FPGA) 中實現 DS2460 的計算能力,從而無需開發軟件來執行復雜的 SHA -1 計算。DSSHA1 或 DS2460 計算出的 MAC 僅適用于 Maxim SHA-1 器件。

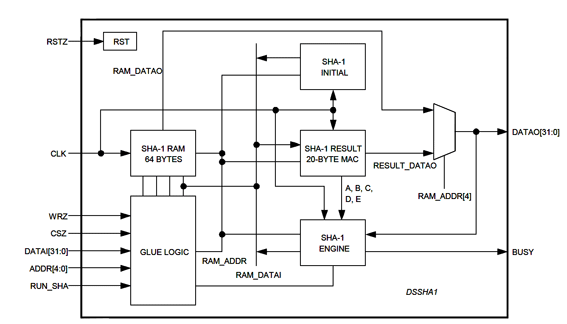

DSSHA1 是一個可合成的、內存映射的 SHA-1 協處理器,它包括一個 64 字節的通用 RAM,用于存儲 64 字節的消息。輸入消息用于計算 SHA-1 MAC。DSSHA1 輸入和輸出端口信號設計為在內部連接到 32 位總線。通過正面的比較結果,在主機系統和從屬附件之間實現了認證安全。

圖 1 顯示了 DSSHA1 框圖。表 1 描述了將 DSSHA1 連接到主機系統的信號。使用數據總線輸入、地址和控制信號,將 64 字節 SHA-1 消息插入到 RAM 中。將輸入信號 RUN_SHA 觸發為邏輯高電平將啟動 SHA-1 計算。輸出 BUSY 信號指示正在發生的計算。完成 BUSY 信號后,結果寄存器包含 20 字節的消息摘要以供讀取。

編輯:hfy

-

存儲器

+關注

關注

38文章

7528瀏覽量

164342 -

微處理器

+關注

關注

11文章

2274瀏覽量

82773 -

Mac

+關注

關注

0文章

1110瀏覽量

51706

發布評論請先 登錄

相關推薦

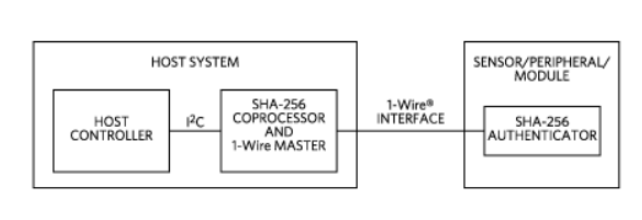

DS2465 SHA-256協處理器與1-Wire主機功能

如何通過使用FPGA高速實現SHA-1消息認證算法?

帶有EEPROM的SHA1協處理器DS2460電子資料

基于SHA-1的郵件去重算法

為什么1-Wire SHA-1器件是安全的?

DSSHA1 內存映射的SHA-1協處理器

DSSHA1數據資料(英文)

Understanding the DSSHA1 Synthesizable SHA-1 Coprocessor

dssha1綜合SHA-1協處理器

基于SHA-1算法的硬件設計及實現(FPGA實現)

安全協處理器/1-Wire? 主控器實現SHA-256認證

淺談DSSHA1可綜合SHA-1協處理器

淺談DSSHA1可綜合SHA-1協處理器

評論