通常,DDR設(shè)計(jì)完成之后 ,對(duì)信號(hào)質(zhì)量并沒(méi)有一個(gè)完全確定的概念,需要我們通過(guò)仿真和測(cè)試的手段去判斷和驗(yàn)證。而此時(shí),往往我們拿到的就是一個(gè)波形,測(cè)試波形或者仿真波形,該如何去判斷其信號(hào)質(zhì)量,參照的標(biāo)準(zhǔn)又是怎樣的,就是我們需要去考慮的重點(diǎn)。

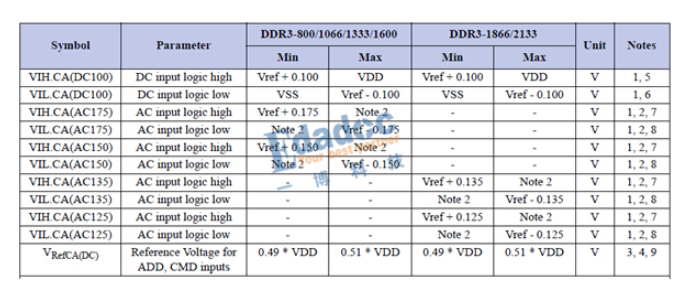

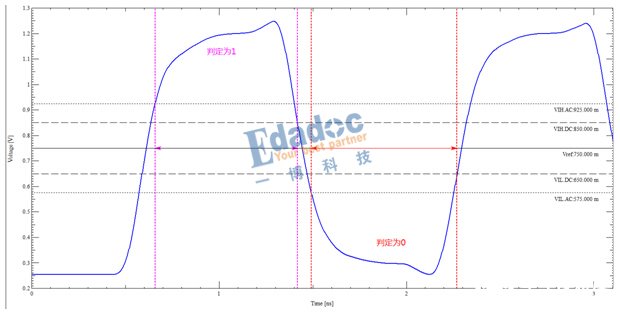

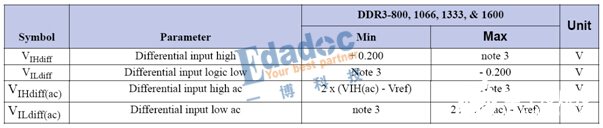

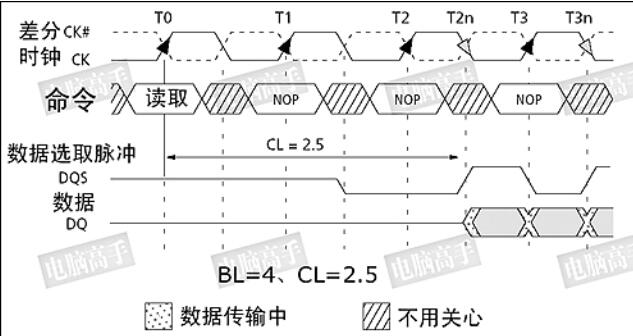

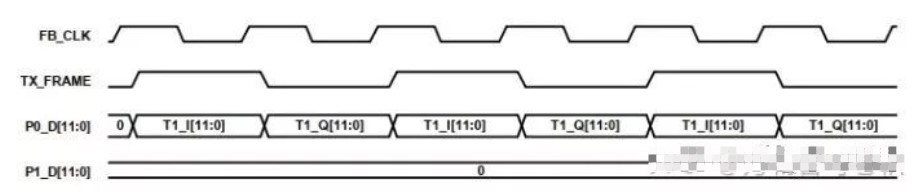

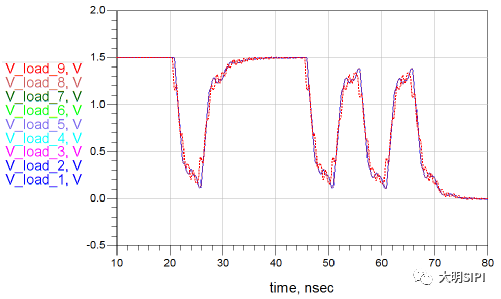

DDR信號(hào)是數(shù)字信號(hào),表現(xiàn)為0、1兩種形式,一般看到的波形都是類似于正弦波的樣式,什么時(shí)候判定為1,什么時(shí)候判定為0呢?每一個(gè)信號(hào)都是以電磁波的形式進(jìn)行傳輸,因此一定具有相應(yīng)的幅值,所以判定方法肯定是當(dāng)幅值高于某一個(gè)值時(shí),判定信號(hào)為1,低于某一個(gè)值時(shí),判定為0。而判定的依據(jù)——某一個(gè)值就是可以從JEDEC中找到的。如圖一所示,是DDR3地址命令信號(hào)的AC、DC標(biāo)準(zhǔn),對(duì)應(yīng)相應(yīng)的速率,就可以在波形上面標(biāo)注出相應(yīng)的VIH和VIL。當(dāng)幅值范圍為VIHAC(min)~VIHDC(min)時(shí),判定為1,當(dāng)幅值范圍為VILAC(max)~VILDC(max)時(shí)判定為0,如下圖二所示

圖一

圖二

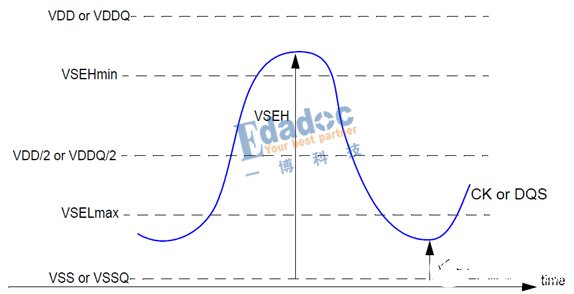

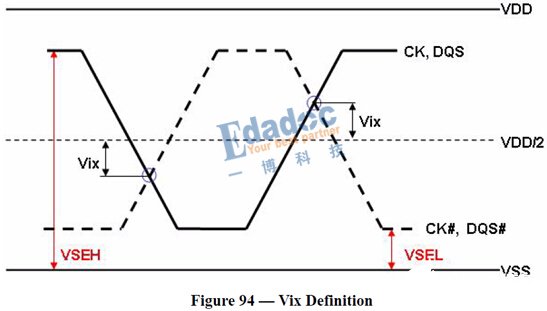

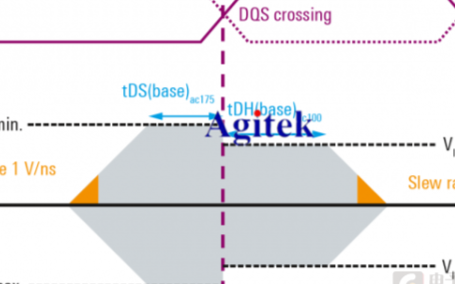

對(duì)于做為差分線的CK信號(hào)和DQS信號(hào)而言,判定的要求又分為單根和差分模式,單根模式的判定標(biāo)準(zhǔn)和地址數(shù)據(jù)線基本一致,如下圖三所示。它的判定標(biāo)準(zhǔn)只有VSEH和VSEL。實(shí)際這兩個(gè)值對(duì)應(yīng)的就是VIH.AC和VIL.AC。

圖三

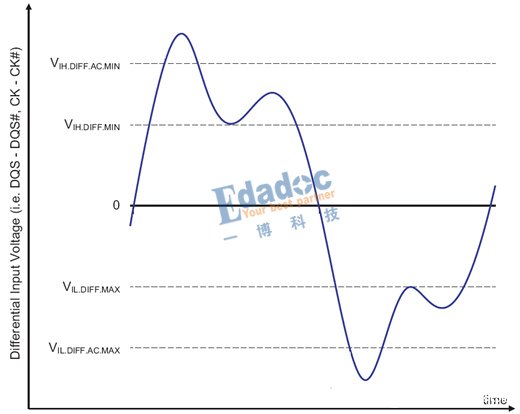

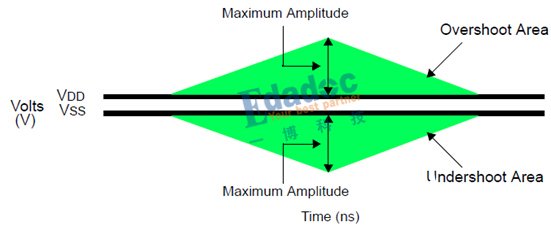

差分模式如圖四所示,數(shù)據(jù)見(jiàn)表格。

圖四

而且同時(shí)對(duì)兩個(gè)單根的交點(diǎn)也有一定的要求,如下圖五所示,兩個(gè)單根的交點(diǎn)位置要在VSEH和VSEL之間,否則的話差分模式下,正半周期和負(fù)半周期可能會(huì)有比較大的一個(gè)比例差異。

圖五

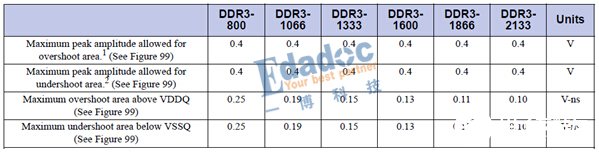

對(duì)信號(hào)幅值的要求不僅僅在這一個(gè)方面,幅值太小,會(huì)讓芯片無(wú)法識(shí)別信號(hào),那么幅值越大,豈不是對(duì)于信號(hào)的判定越有利。其實(shí)不然,一般的芯片都會(huì)有一個(gè)耐壓值,高于該值,對(duì)于芯片的使用壽命會(huì)有一個(gè)較大的影響,所以,可以看到JEDEC中,還有一個(gè)Overshoot和Undershoot的概念,下面是DDR3對(duì)于信號(hào)這方面的一個(gè)要求,圖六中是對(duì)Overshoot和Undershoot一個(gè)面積區(qū)域和具體的數(shù)值的定義,即最大值的范圍在VSS-0.4~VDD+0.4之間,斜率按照相應(yīng)的速率查找,其中斜率的定義對(duì)于數(shù)據(jù)線和地址線是有區(qū)別的,要用到的時(shí)候,在JEDEC中查找即可。

圖六

這些都是對(duì)DDR信號(hào)最基礎(chǔ)的認(rèn)識(shí),只是基于幅值方面的一些要求。

編輯:hfy

-

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42389 -

DDR

+關(guān)注

關(guān)注

11文章

715瀏覽量

65531 -

電磁波

+關(guān)注

關(guān)注

21文章

1470瀏覽量

53941 -

JEDEC

+關(guān)注

關(guān)注

1文章

36瀏覽量

17479

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何去測(cè)量數(shù)字傳輸信號(hào)的質(zhì)量?

過(guò)孔STUB長(zhǎng),DDR信號(hào)“強(qiáng)”?

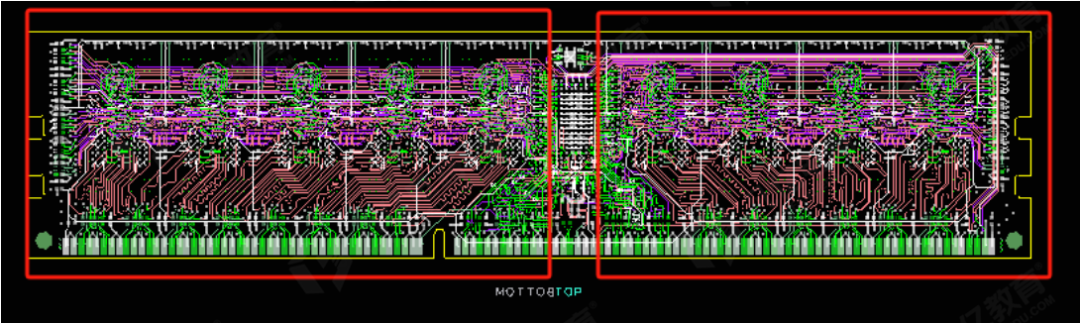

關(guān)于DDR3信號(hào)扇出和走線問(wèn)題解析

DDR工作原理_DDR DQS信號(hào)的處理

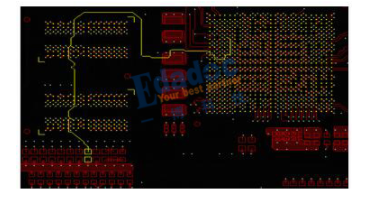

DDR高速信號(hào)線的布線原則和技巧

利用DDR3數(shù)據(jù)眼圖測(cè)試來(lái)實(shí)現(xiàn)快速檢查信號(hào)質(zhì)量

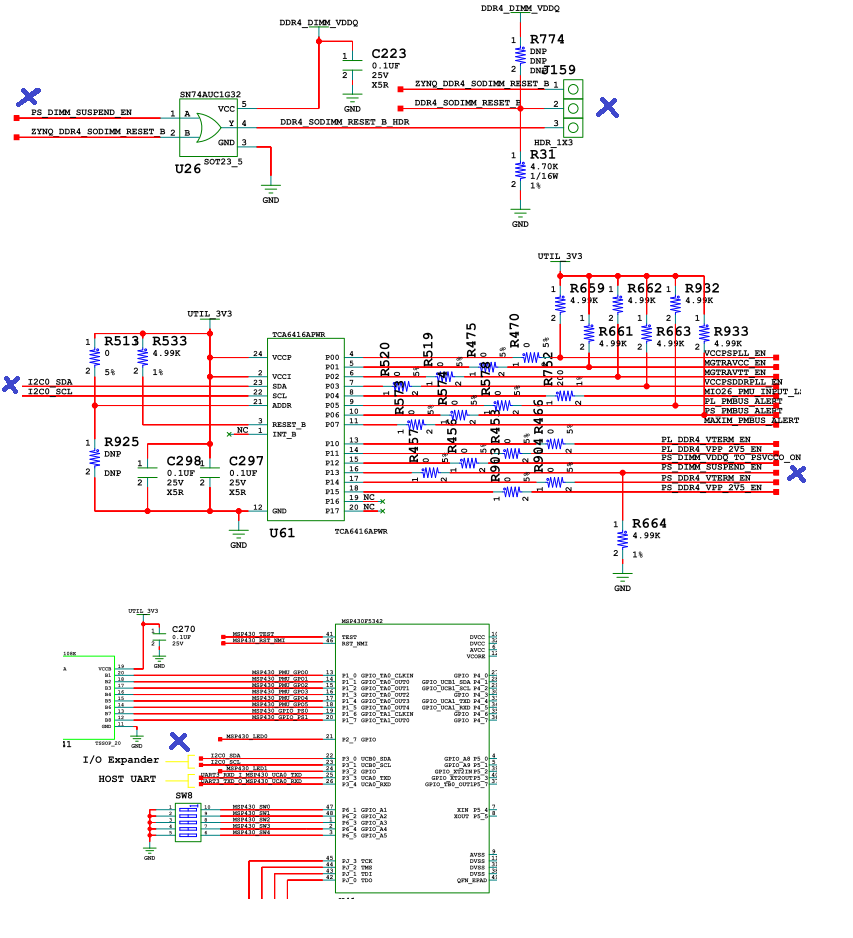

ZCU10中MPSoC對(duì)DDR復(fù)位信號(hào)設(shè)計(jì)

如何選擇DDR的拓?fù)浣Y(jié)構(gòu)?怎樣去改善信號(hào)質(zhì)量呢?

DDR4通道中過(guò)孔 stub對(duì)信號(hào)質(zhì)量的影響分析

如何去解決LVDS差分接口的DDR信號(hào)問(wèn)題

看看電源噪聲對(duì)信號(hào)質(zhì)量的影響

改善帶有ECC奇數(shù)負(fù)載的DDR2信號(hào)質(zhì)量的方法

模擬信號(hào)是什么意思?怎么判斷數(shù)字信號(hào)和模擬信號(hào)?

DDR加終端匹配電阻和不加信號(hào)質(zhì)量的區(qū)別

關(guān)于DDR信號(hào)的如何去判斷信號(hào)質(zhì)量?

關(guān)于DDR信號(hào)的如何去判斷信號(hào)質(zhì)量?

評(píng)論