作者:徐小良,何春,賈宇明,劉輝華

基于掃描路徑法的可測性設計技術是可測性設計(DFT)技術的一個重要的方法,這種方法能夠從芯片外部設定電路中各個觸發(fā)器的狀態(tài),并通過簡單的掃描鏈的設計,掃描觀測觸發(fā)器是否工作在正常狀態(tài),以此來檢測電路的正確性。但隨著數(shù)字電路朝著超大規(guī)模的方向發(fā)展,設計電路中使用的觸發(fā)器的數(shù)目也日趨龐大,怎樣采用合適的可測性設計策略,檢測到更多的觸發(fā)器,成為基于掃描路徑法的一個關鍵問題。

本文采用基于掃描路徑法的可測性設計技術,對一款約750萬門級雷達芯片的實際電路進行可測性設計。在設計中通過使用時鐘復用技術、時鐘電路處理技術以及IP隔離技術等幾種有效的設計策略,大大提高了芯片的故障覆蓋率,最終達到可測性設計的目的。

1 掃描鏈設計原理

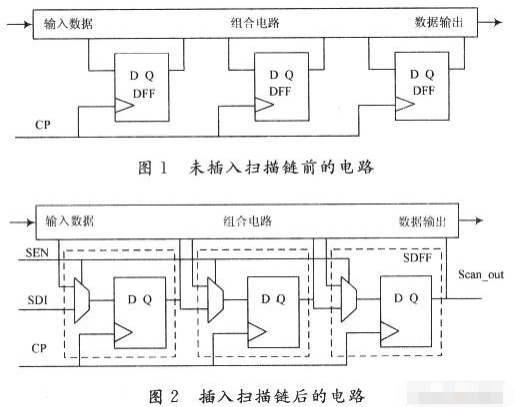

數(shù)字電路由大量的組合元件和時序元件組成,時序元件具體體現(xiàn)為單個的觸發(fā)器(DFF)。數(shù)字電路基本組成如圖1所示。其中系統(tǒng)時鐘(CP)來控制各個觸發(fā)器的數(shù)據(jù)端口相應數(shù)據(jù)的輸入輸出。

基于掃描路徑法的可測性設計就是將電路中的時序元件觸發(fā)器替換為相應的可掃描的時序元件掃描觸發(fā)器(SDFF);然后將上一級掃描觸發(fā)器的輸出端(Q)連接到下一級的數(shù)據(jù)輸入端(SDI),從而形成一個從輸入到輸出的測試串行移位寄存器,即掃描鏈(ScanChain);通過CP端時鐘的控制,實現(xiàn)對時序元件和組合邏輯的測試。實現(xiàn)掃描鏈設計后的電路如圖2所示。

采用掃描設計技術后,在掃描控制端(SEN)和時鐘端的控制下,通過掃描數(shù)據(jù)輸入端,可以把需要的數(shù)據(jù)串行地移位到掃描寄存器單元中,串行地控制各個單元;同時也可以通過掃描輸出端(Scan_out)串行地觀測它們。這樣就增加了時序電路的可控制性和可觀測性。

2 掃描鏈策略設計

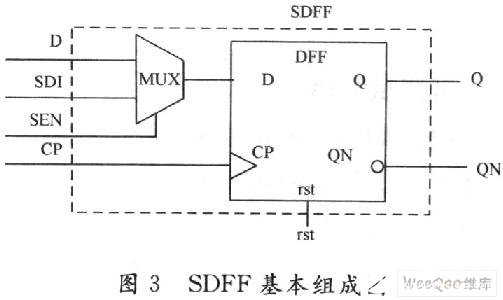

圖2中虛線部分為掃描觸發(fā)器,即掃描鏈的基本組成單元,其構(gòu)成原理如圖3所示。

掃描鏈設計前,電路中的觸發(fā)器都是通過系統(tǒng)時鐘端口控制數(shù)據(jù)的變化,因而在做掃描設計時可以通過系統(tǒng)時鐘復用檢測到更多的觸發(fā)器,以此達到控制掃描觸發(fā)器的目的。

同樣的道理,一些特殊電路中的觸發(fā)器也是采用手動或者軟件的方法將它們串聯(lián)到掃描鏈中,以此增加可掃描的觸發(fā)器數(shù),最終使故障覆蓋率得以提高。但需要注意的是,這些可測性設計策略應用的前提是不能改變原始設計的功能。

3 設計中采用的策略

在進行DFT設計并插入掃描鏈的時候,最為重要的一個問題就是測試覆蓋率,而它的最終值是由觸發(fā)器的總數(shù)和最終能夠測試到的觸發(fā)器的數(shù)目的比值決定的,因此是否能夠盡可能多地測試到本雷達芯片電路中的觸發(fā)器,成為掃描路徑法設計的一個關鍵問題。針對實際的設計電路提出了以下三種有效的設計策略,由最終測試結(jié)果可知,采用此設計策略后可大大提高測試覆蓋率,滿足設計指標需要。

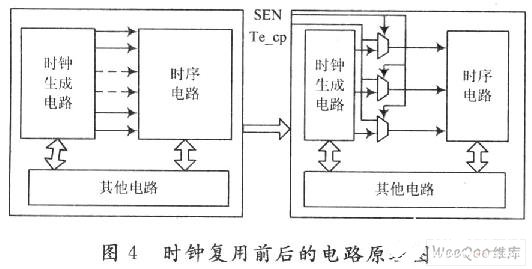

3.1 時鐘復用技術

每個觸發(fā)器都受系統(tǒng)時鐘控制,系統(tǒng)時鐘能夠覆蓋本設計中大部分的觸發(fā)器元件,因而考慮使用時鐘復用技術,在插入掃描鏈進行測試時,把測試時鐘引入到系統(tǒng)時鐘上,這樣測試時鐘就能覆蓋盡可能多的觸發(fā)器,并在插入掃描鏈后,替換成掃描觸發(fā)器。其實現(xiàn)原理如圖4所示。

從圖中可以看出,時鐘電路產(chǎn)生很多不同頻率的時鐘以滿足不同模塊的需求,在時鐘電路的輸出端口加入相應的選擇器(MUX)控制時鐘的選擇;當處于正常工作狀態(tài)時,MUX選擇正常的時鐘進入相應的模塊,進而實現(xiàn)相應的功能;當處于掃描狀態(tài)時,這些MUX都是選擇同樣的掃描測試時鐘信號(Te cp)進人到各個模塊進行測試。這樣做的優(yōu)點在于不僅滿足了測試選擇的需要,而且也盡可能地測試到所有觸發(fā)器,滿足測試覆蓋率的需要。

3.2 特殊時鐘電路處理

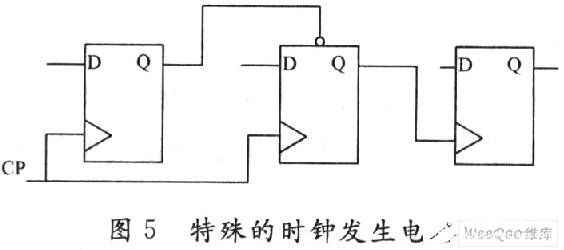

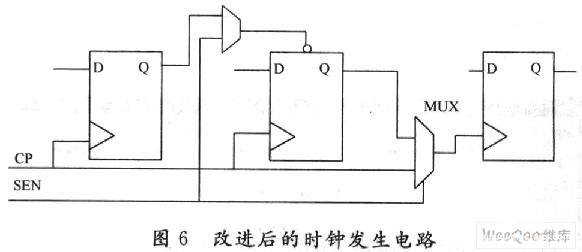

在本設計中存在很多特殊的電路,其中有一種時鐘發(fā)生電路是不能進行掃描路徑法的可測性設計,具體的電路圖如圖5所示。

在這種結(jié)構(gòu)中,時鐘從第二個觸發(fā)器的Q端輸出,輸入到第三個觸發(fā)器的時鐘(CP)端。由于掃描時鐘無法控制第三個以及后續(xù)的觸發(fā)器,設計的掃描鏈將不會覆蓋之后的電路,結(jié)果導致故障覆蓋率降低,測試覆蓋率也會下降。

改進此種電路結(jié)構(gòu)的方法是手動或者用軟件方式增加一個MUX選擇器,當在掃描鏈插入時,正常的控制時鐘信號就會進入第三個觸發(fā)器的時鐘端。具體實現(xiàn)的電路結(jié)構(gòu)如圖6所示。

使用此策略,在插入掃描鏈后,當MUX選擇器處在掃描狀態(tài)時,掃描時鐘就會連接到后續(xù)的觸發(fā)器,并將其連接到掃描鏈上,這樣就會大大提高故障覆蓋率,從而提高測試覆蓋率。

3.3 IP隔離技術

設計之中要用到很多IP模塊,在綜合后的網(wǎng)表中表現(xiàn)為一個個沒有具體電路的“黑匣子”,這些“黑匣子”的存在使得部分時序組合電路不能或者很難進行基于掃描路徑法的DFT設計,需要利用其他的DFT設計工具進行可測性設計,例如在本設計中采用的RAM和ROM存儲器模塊。

因此為確保與IP相連的下級時序電路部分能夠被正常設計的掃描鏈覆蓋,增加觸發(fā)器的可測范圍,采用的解決方案是用軟件命令解決的方法將此類IP模塊隔離,暫時不將此模塊進行DFT設計,其實現(xiàn)原理如圖7所示。

通過此種方法可以有效地將一個或多個類似的IP模塊與原電路軟隔離開。當電路工作在非掃描狀態(tài)下,數(shù)據(jù)按照正常的數(shù)據(jù)流方向流、進流出IP模塊;當電路工作在掃描狀態(tài)時,掃描數(shù)據(jù)繞過相應1P模塊,按照相應的掃描鏈路徑流進下級時序電路部分,實現(xiàn)掃描測試的功能。

這種方法既不破壞原來芯片電路的結(jié)構(gòu)和整體實現(xiàn)的功能,同時也保證了DFT設計的順利進行,提高了本芯片可測性設計的覆蓋率。

4 結(jié)果分析

4.1 測試結(jié)果

當沒有采用任何設計策略時,本芯片的測試覆蓋率只能達到30%~40%左右,遠遠達不到要求的性能指標。

從圖8可以看出,當采用了以上設計策略后測試覆蓋率(test coverage)、故障覆蓋率(fault coverage)和ATPG覆蓋率分別達到96.95 9/6,94.52%和99.99%。

4.2 測試結(jié)果分析

在圖8所示的測試結(jié)果數(shù)據(jù)欄中,左側(cè)的數(shù)據(jù)欄中顯示的是總共生成的測試向量以及有效的測試向量數(shù)目。右側(cè)顯示的是在掃描鏈測試過程中能夠測出的各種故障數(shù)目,其中故障覆蓋率F的計算公式為:

其中:不可測故障包括摒棄故障、固定故障、冗余故障等。本設計考慮了很多故障模型,其中就包括很多的固定故障類型(例如:芯片端口被鎖定為固定值,無法檢測到)計算到上述計算公式中,因此實際的不可測故障要比工具中統(tǒng)計的數(shù)字要少;通過以上分析可知,實際能達到的故障覆蓋率要優(yōu)于測試結(jié)果。

5 結(jié) 語

本文對一款約750萬門的雷達數(shù)字處理芯片的電路進行基于掃描路徑法的可測性設計,在設計中針對實際電路門數(shù)特別龐大的特點,采用時鐘復用的技術,合理利用已經(jīng)存在設計資源,使可測到的觸發(fā)器數(shù)目大大增加;針對特殊的電路應用特殊的處理策略,增加了可測性設計的故障覆蓋率。由試驗結(jié)果可知,與未采用以上提到的設計策略相比,其最終的測試覆蓋率得到很明顯的提升,實現(xiàn)了設計策略應用的目標,最終也達到了設計的指標要求。

責任編輯:gt

-

芯片

+關注

關注

456文章

51182瀏覽量

427279 -

雷達

+關注

關注

50文章

2966瀏覽量

118022 -

觸發(fā)器

+關注

關注

14文章

2003瀏覽量

61347

發(fā)布評論請先 登錄

相關推薦

如何使用SoC FPGA,實現(xiàn)汽車雷達的數(shù)字化處理

YC數(shù)字處理芯片VPC3215相關資料分享

圖像數(shù)字處理芯片SDA9220電子資料

數(shù)字處理電路SDA9400電子資料

請教一下中頻數(shù)字處理的核心器件 AD6644設計技巧

遠距離射頻卡讀寫器數(shù)字處理模塊的設計怎么實現(xiàn)?

三菱電機汽車數(shù)字處理中心采用ADI的SHARC處理器

基于DSP芯片的音頻信號數(shù)字處理接口

AD6644做中頻數(shù)字處理模塊及接口的設計

基于DSP的實時嵌入式數(shù)字處理系統(tǒng)設計剖析

基于可測性設計的雷達數(shù)字處理芯片的實現(xiàn)

基于可測性設計的雷達數(shù)字處理芯片的實現(xiàn)

評論