在當今的許多細分市場,交錯式模數(shù)轉(zhuǎn)換器(ADC)在許多應(yīng)用中都具有多項優(yōu)勢。在通信基礎(chǔ)設(shè)施中,存在著一種推動因素,使ADC的采樣速率不斷提高,以便支持多頻段、多載波無線電,除此之外滿足DPD(數(shù)字預(yù)失真)等線性化技術(shù)中更寬的帶寬要求。在軍事和航空航天領(lǐng)域,采樣速率更高的ADC可讓多功能系統(tǒng)用于通信、電子監(jiān)控和雷達等多種應(yīng)用中——此處僅舉數(shù)例。工業(yè)儀器儀表應(yīng)用中始終需要采樣速率更高的ADC,以便充分精確地測量速度更高的信號。

首先,一定要準確地了解交織型ADC是什么。要了解交錯,最好了解一下實際發(fā)生的情況以及它是如何實現(xiàn)的。有了基本的了解后,再討論交錯的好處。當然,我們都知道,天下沒有免費的午餐,因此需要充分評估和驗證交織采樣相關(guān)的技術(shù)難點。

關(guān)于交錯

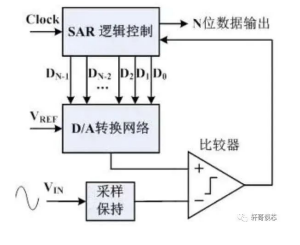

若ADC為交錯式,則兩個或兩個以上具有固定時鐘相位差關(guān)系的ADC用來同步采樣輸入信號,并產(chǎn)生組合輸出信號,使得采樣帶寬為單個ADC帶寬的數(shù)倍。利用m個ADC可讓有效采樣速率增加m倍。為簡便起見并易于理解,我們重點考察兩個ADC的情況。這種情況下,如果兩個ADC的每一個采樣速率均為fS, 且呈交錯式,則最終采樣速率為2× fS。這兩個ADC必須具有確定的時鐘相位差關(guān)系,才能正確交錯。時鐘相位關(guān)系由等式1給出,其中:n是某個特定的ADC,m是ADC總數(shù)。

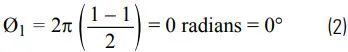

舉例而言,兩個ADC采樣速率均為100 MSPS且呈交錯式,因此采樣速率為200 MSPS。此時,等式1可用來推導(dǎo)出兩個ADC的時鐘相位關(guān)系,如等式2和等式3。

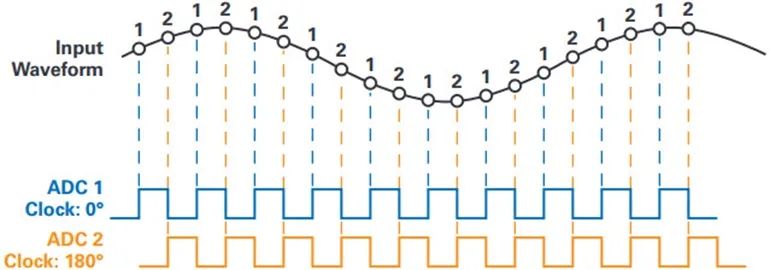

注意,如果已知時鐘相位關(guān)系,便可確定不同量化值的組合輸出。圖1以圖形說明時鐘相位關(guān)系,以及兩個100 MSPS交織型ADC的樣本結(jié)構(gòu)。注意180°時鐘相位關(guān)系,以及樣本是如何交 錯的。輸入波形也可由兩個ADC進行采樣。在這種情況下,采用經(jīng)過2分頻的200 MHz時鐘輸入,并所需的時鐘相位發(fā)送至每個ADC,便可實現(xiàn)交錯。

圖1. 兩個交錯式100 MSPS ADC—基本原理圖。

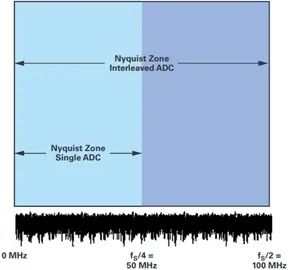

此概念還可以另一種方式表達,如圖2所示。通過將這兩個100MSPS ADC以交錯方式組合,采樣速率便能增加至200 MSPS。這樣每個奈奎斯特區(qū)可以從50 MHz擴展到100 MHz,使工作時的可 用帶寬翻倍。增加的工作帶寬可為多個市場領(lǐng)域的應(yīng)用帶來諸多優(yōu)勢。無線電系統(tǒng)可以增加其支持的頻段數(shù);雷達系統(tǒng)可以增加空間分辨率;而測量設(shè)備可以實現(xiàn)更高的模擬輸入帶寬。

圖2. 兩個交錯式100 MSPS ADC—時鐘和樣本。

交錯的優(yōu)勢

交錯結(jié)構(gòu)的優(yōu)勢可惠及多個細分市場。交織型ADC最大好處是增加了帶寬,因為ADC的奈奎斯特帶寬更寬了。同樣,我們舉兩個100 MSPS ADC交錯以實現(xiàn)200 MSPS采樣速率的例子。圖3顯示通過交錯兩個ADC,可以大幅增加帶寬。這為多種應(yīng)用場景產(chǎn)生了諸多收益。就像蜂窩標準增加了通道帶寬和工作頻段數(shù)一樣,對ADC可用帶寬的要求也越來越高。此外,在軍事應(yīng)用中,需要更好的空間識別能力以及增加后端通信的通道帶寬,這些都要求ADC提供更高的帶寬。由于這些領(lǐng)域?qū)挼囊笤絹碓礁撸虼诵枰獪蚀_地測量這些信號。因此,為了正確地獲取和測量這些高帶寬信號,測量設(shè)備也需要更高的帶寬。很多設(shè)計中的系統(tǒng)要求其實領(lǐng)先于商用ADC技術(shù)。交錯結(jié)構(gòu)可以彌補這一技術(shù)差距。

圖3. 兩個交織型ADC——奈奎斯特區(qū)。

增加采樣速率能夠為這些應(yīng)用提供更多的帶寬,而且頻率規(guī)劃更輕松,還能降低通常在ADC輸入端使用抗混疊濾波器時帶來的復(fù)雜性和成本。面對這些優(yōu)勢,大家一定想知道需要為此付 出什么代價。就像大多數(shù)事情一樣,天下沒有免費的午餐。交織型ADC具有更高的帶寬和其他有用的優(yōu)勢,但在處理交織型ADC時也會帶來一些挑戰(zhàn)。

交錯挑戰(zhàn)

在交錯組合ADC時存在一些挑戰(zhàn),還有一些注意事項。由于與交錯ADC相關(guān)的缺陷,輸出頻譜中會出現(xiàn)雜散。這些缺陷基本上是兩個正在交錯的ADC之間不匹配。輸出頻譜中的雜散導(dǎo)致的基本不匹配有四種。包括失調(diào)不匹配、增益不匹配、時序不匹配和帶寬不匹配。

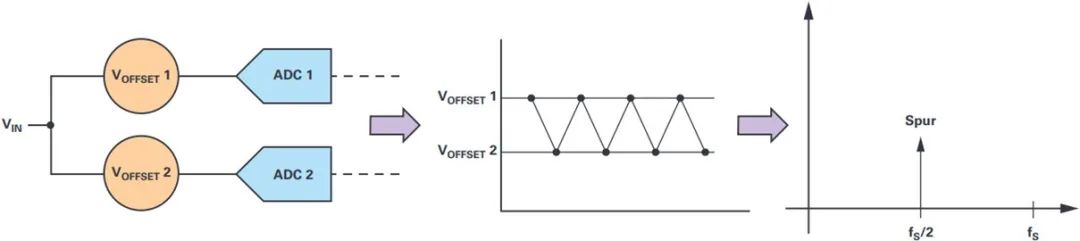

其中最容易理解的可能是兩個ADC之間的失調(diào)不匹配。每個ADC都會有一個相關(guān)的直流失調(diào)值。當兩個ADC交錯并在兩個ADC之間來回交替采樣時,每個連續(xù)采樣的直流失調(diào)會發(fā)生變化。圖4 舉例說明了每個ADC如何具有自己的直流失調(diào),以及交錯輸出如何有效地在這兩個直流失調(diào)值之間來回切換。輸出以fS/2的速率在這些失調(diào)值之間切換,將導(dǎo)致位于fS/2的輸出頻譜中產(chǎn)生雜散。由于不匹配本身沒有頻率分量,并且僅為直流,因此出現(xiàn)在輸出頻譜中的雜散頻率僅取決于采樣頻率,并將始終出現(xiàn)fS/2在2頻率下。雜散的幅度取決于ADC之間失調(diào)不匹配的幅度。不匹配值越大,雜散值就越大。為了盡可能減少失調(diào)不匹配導(dǎo)致的雜散,不需要完全消除每個ADC中的直流失調(diào)。這樣做會濾除信號中的所有直流成分,不適合使用零中頻(ZIF)架構(gòu)的系統(tǒng),該架構(gòu)信號成分復(fù)雜,DC量實際是有用信號。相反,更合適的技術(shù)是讓其中一個ADC的失調(diào)與另一個ADC匹配。選擇一個ADC的失調(diào)作為基準,另一個ADC的失調(diào)設(shè)置為盡可能接近的值。失調(diào)值的匹配度越高,在fS/2產(chǎn)生的雜散就越低。

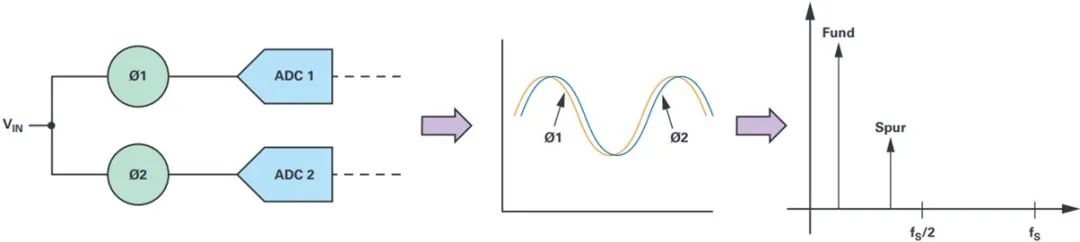

圖4. 失調(diào)不匹配。

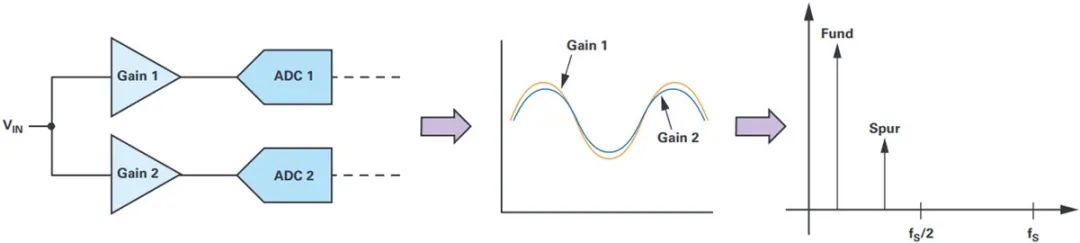

交錯時要注意的第二個不匹配是ADC之間的增益不匹配。圖5顯示了兩個交錯式轉(zhuǎn)換器之間的增益不匹配。在這種情況下,有一個不匹配頻率分量。為了觀察這種不匹配,必須向ADC施加 信號。對于失調(diào)不匹配,無需信號即可查看兩個ADC的固有直流失調(diào)。對于增益不匹配,如果不存在信號,就無法測量增益不匹配,因而無法了解增益不匹配。增益不匹配將會產(chǎn)生與輸入頻率和采樣速率相關(guān)的輸出頻譜雜散,出現(xiàn)在fS/2 ± fIN處。為了最大程度地降低增益不匹配引起的雜散,采用了與失調(diào)不匹配類似的策略。選擇其中一個ADC的增益作為基準,另一個ADC的增益設(shè)置為盡可能接近的值。每個ADC增益值的匹配度越高,輸出頻譜中產(chǎn)生的雜散就越小。

圖5. 增益不匹配。

接下來,我們必須探討兩個ADC之間的時序不匹配。時序不匹配有兩個分量:ADC模擬部分的群延遲和時鐘相位偏差。ADC中的模擬電路具有相關(guān)的群延遲,兩個ADC的群延遲值可能不同。此外還有時鐘偏斜,它也包括兩個分量:各ADC的孔徑不確定性和一個與輸入各轉(zhuǎn)換器的時鐘相位精度相關(guān)的分量。圖6以圖形說明ADC時序不匹配的機制和影響。與增益不匹配雜散相似,時序不匹配雜散也與輸入頻率和采樣速率呈函數(shù)關(guān)系,出現(xiàn)在fS/2 ± fIN處。

圖6. 時序不匹配

為了盡可能降低時序不匹配引起的雜散,需要利用合適的電路設(shè)計技術(shù)使各轉(zhuǎn)換器模擬部分的群延遲恰當匹配。此外,時鐘路徑設(shè)計必須盡量一致以使孔徑不確定性差異最小。最后,必須精確控制時鐘相位關(guān)系,使得兩個輸入時鐘盡可能相差180°。與其他不匹配一樣,目標是盡量消除引起時序不匹配的機制。

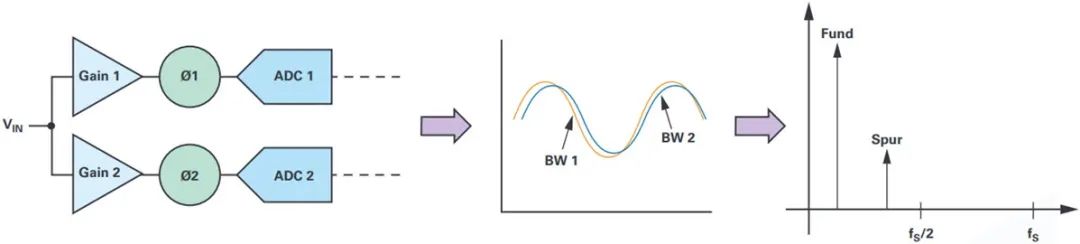

最后一個不匹配可能最難理解和處理:帶寬不匹配。如圖7所示,帶寬不匹配具有增益和相位/頻率分量。這使得解決帶寬不匹配問題變得更為困難,因為它含有另外兩個不匹配參數(shù)的分量。然而,在帶寬不匹配中,我們可在不同的頻率下看到不同增益值。此外,帶寬具有時序分量,使不同頻率下的信號通過每個轉(zhuǎn)換器時具有不同的延遲。出色的電路設(shè)計和布局布線實踐是減少ADC間帶寬失配的最好方法。ADC之間的匹配越好,則產(chǎn)生的雜散就越少。正如增益和時序不匹配會導(dǎo)致在輸出頻譜的fS/2 ± fIN處產(chǎn)生雜散一樣,帶寬不匹配也會在相同頻率處產(chǎn)生雜散。

圖7. 帶寬不匹配。

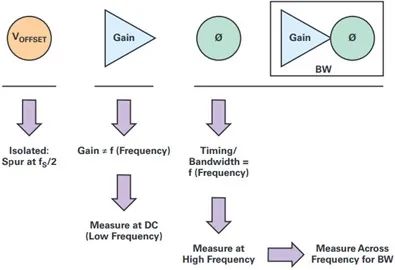

現(xiàn)在我們已經(jīng)討論了交錯ADC時引起問題的四種不同的不匹配,可以發(fā)現(xiàn)有一個共性。四個不匹配中有三個會在輸出頻譜的fS/2 ± fIN處產(chǎn)生雜散。失調(diào)不匹配雜散很容易識別,因為只有它位于fS/2處,并可輕松地進行補償。增益、時序和帶寬不匹配都會在輸出頻譜的fS/2 ± fIN 處產(chǎn)生雜散;因此,隨之而來的問題是:如何確定它們各自的影響。圖8以簡單的圖形方式指導(dǎo)如何從交織型ADC的不同不匹配中識別雜散來源。

圖8. 交錯式不匹配的相互關(guān)系。

如果只是考察增益不匹配,那么它就是一個低頻(或直流)類型的不匹配。通過在直流附近執(zhí)行低頻增益測量,然后在較高的頻率處執(zhí)行增益測量,可將帶寬不匹配的增益分量與增益不 匹配分離。增益不匹配與頻率無函數(shù)關(guān)系,而帶寬不匹配的增益分量與頻率呈函數(shù)關(guān)系。對于時序不匹配,可以采用類似的方法。在直流附近執(zhí)行低頻測量,然后在較高的頻率下執(zhí)行后續(xù)測量,以便將帶寬不匹配的時序分量與時序不匹配分離。

結(jié)論

最新通信系統(tǒng)設(shè)計、尖端雷達技術(shù)和超高帶寬測量設(shè)備似乎始終領(lǐng)先于現(xiàn)有的ADC技術(shù)。在這些需求的推動下,ADC的用戶和制造商都想方設(shè)法,試圖跟上這些需求的步伐。與提高典型ADC轉(zhuǎn)換速率的傳統(tǒng)方式相比,交錯ADC可以更快的速度實現(xiàn)更寬的帶寬。將兩個或更多ADC交錯起來,可以增加可用帶寬,并以更快的速度滿足系統(tǒng)設(shè)計要求。然而,交錯ADC并非沒有代價,ADC之間的不匹配不容忽視。雖然不匹配確實存在,但了解其本質(zhì)及如何正確處理它們,設(shè)計人員就能更加明智地利用這些交織型ADC,并滿足最新系統(tǒng)設(shè)計不斷增長的要求。

責(zé)任編輯:lq

-

adc

+關(guān)注

關(guān)注

99文章

6533瀏覽量

545753 -

時鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131799 -

頻譜

+關(guān)注

關(guān)注

7文章

887瀏覽量

45785

原文標題:交織型ADC到底是個啥?今天咱們就科普一下~

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AN-283: Σ-Δ型ADC和DAC[中文版]

![AN-283: Σ-Δ<b class='flag-5'>型</b><b class='flag-5'>ADC</b>和DAC[中文版]](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

TVP5158采集四路圖像,解交織后圖像錯誤,為什么?

使用ADC12DJ3200做采樣系統(tǒng)時,發(fā)現(xiàn)SFDR受限于交織雜散,有什么方法降低Fs/2-Fin處的雜散?

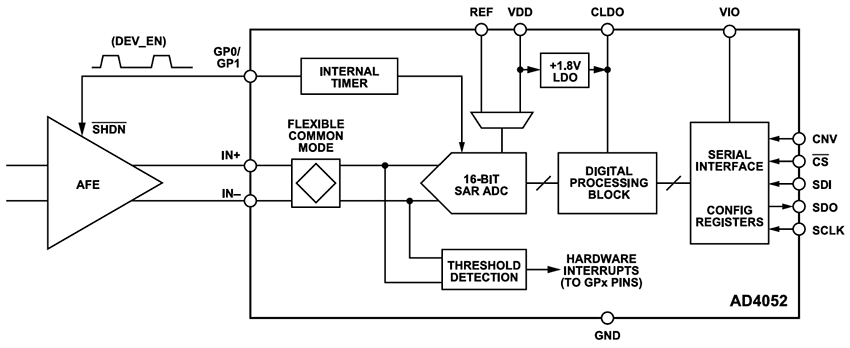

AD4052緊湊型低功耗Easy Drive SAR ADC

ads62p49輸出ramp型測試碼,但是FPGA無法準確可靠地接收到該測試碼,怎么解決?

高準確度信號鏈解決方案快速實現(xiàn)七位半DMM

求助,關(guān)于ADC12DL3200EVM時間交織采樣的問題求解

ADS131B23-Q1這種Δ-∑型的ADC前端的RC設(shè)計有什么注意的嗎?

將LM50接在雙極性的ADC上,能否采集到準確的溫度?

不同類型adc的優(yōu)缺點

adc的分類及特點

RA8 Cortex-M85 Helium入門指南(3)

如何確保ADC輸出接地的準確性

STM32G431的ADC數(shù)據(jù)不準確是什么原因?qū)е碌模?/a>

ADC都有哪些分類

準確地了解交織型ADC是什么

準確地了解交織型ADC是什么

評論