1、實際走線分析:

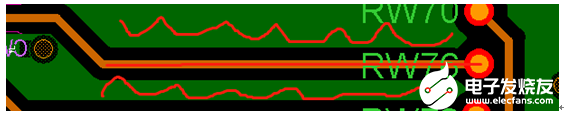

上面的走線橘色為信號走線,周圍綠色(波浪標注)為周圍包地,下方為第二層完整地平面。

從上圖來看設(shè)計師的本意是好的,有參考地平面,周圍也有包地,此時設(shè)計正確的話可以保證回流路徑阻抗最小,因為可以從兩邊包地回流和地平面回流,此時可以效果最好。

但是,上面出現(xiàn)的問題就是包地并未通過地孔和地平面連接起來。具體如下所示:

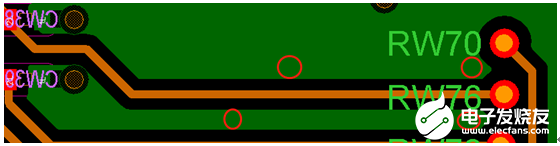

假設(shè)回流路徑是兩邊包地,信號流向為從右向左,下邊部分包地紅色路徑為回流信號,此時回流信號向右走,但是因為前面沒有接地孔,所以信號返回,尋找最小路徑(圖中下邊白色路徑);另上邊回流也是,因為靠近過孔處無接地過孔,則信號沿著灰色路線找到最近的接地過孔,此時這兩個不完整的包地,導(dǎo)致了信號路徑阻抗不是最小,且下邊走線較細,寄生電感較大,且為一端接地,此時模型就是一個天線,很有可能導(dǎo)致“天線輻射能量”,所以有了完整的地平面,包地只是錦上添花的行為,但是一定要注意包地處理不好,有可能導(dǎo)致更為嚴重的輻射。

最好的解決方法如下:

在兩邊包地線上沿一定距離打上接地/包地過孔,此時可以解決回流路徑阻抗增大的問題。

2、實際走線分析

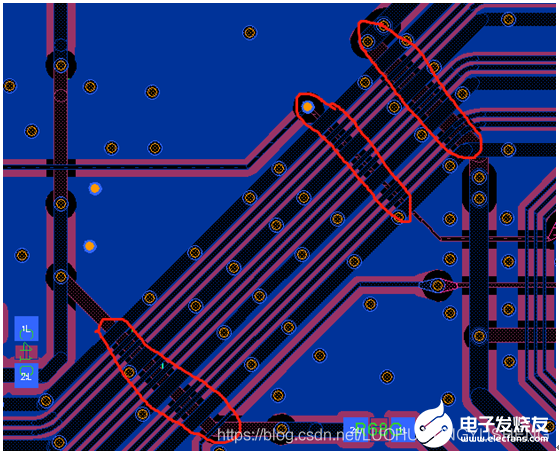

如下圖所示為一組PCIE走線,其中包括三組差分線,發(fā)送、接收和時鐘參考。如下走線差分線走的沒有問題,但是背部的橫向走線切斷了背面的完整地平面,雖然走線周圍是有完整包地的,但是地平面被三端走線破壞嚴重。如果做高速分析以及實際測試驗證很久的話,我們都知道完整的地平面是根本,周圍包地只是錦上添花的行為,我們以時鐘來分析信號回流。

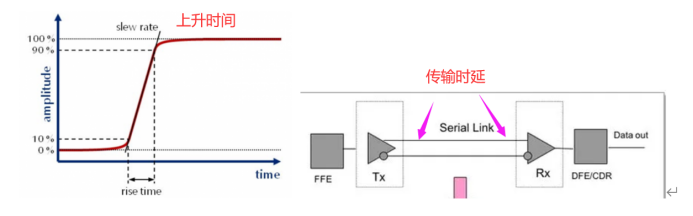

時鐘信號回流分析:

時鐘信號是由PCIE主機給到PCIE從機的,所以信號流向是指向左下角的。而此時的信號回流路徑包含包地路徑和地平面路徑。

包地路徑很好,信號直接沿著包地路徑回流沒有多大問題;但是對于地平面回流就存在問題了,所以此時來看一下:

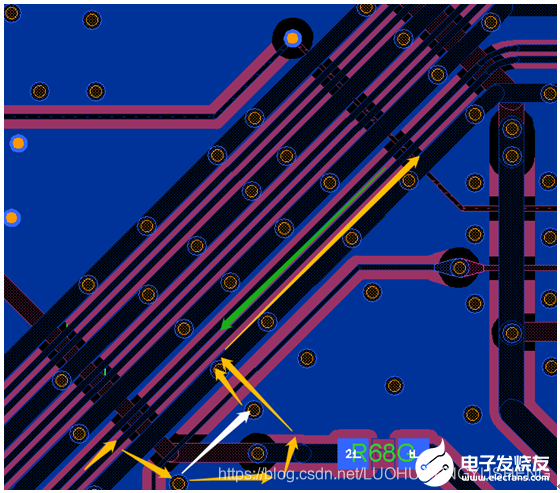

假設(shè)地平面回流信號在未分割處是在信號下方鏡像回流,但是因為下方走線導(dǎo)致地平面被破壞,假設(shè)黃色箭頭指示為地平面回流信號,當遇到分割,則電流沿著分割界面一直走,直到繞過分割平面,然后再回到信號路徑鏡像對應(yīng)面;當然也有一條路徑是尋找最近過孔,如白色路徑,沿著過孔走頂層,再經(jīng)過過孔回到底層參考地,此時大家發(fā)現(xiàn)一個很明顯的問題那就是路程變長了(因為繞路了),此時在低頻下沒有問題,但是在高頻下速率很高,一個簡單的上升沿就可能導(dǎo)致輻射嚴重超標,而此時回流路徑變長,寄生電感增加,感抗變大,很有可能導(dǎo)致嚴重的EMC問題,所以請一定不要這樣做。

所以成本允許的話,對于這種一定設(shè)計為四層板,因為兩層板真的很難找到一個完整的地參考平面,哪怕四層板完整的參考地沒有,但是對應(yīng)信號層找出完整的電源平面也是可以的。另外而言,是在不允許,則可以在分割的兩個地之間連接一個0歐姆電阻,也就是我們俗稱的“跨接電阻”,就是把兩邊連接起來,此時回流信號直接走我們搭建的“跨街橋”就行,不用繞路,當然阻抗就是最小的。

版權(quán)聲明:本文為博主原創(chuàng)文章,遵循 CC 4.0 BY-SA 版權(quán)協(xié)議,轉(zhuǎn)載請附上原文出處鏈接和本聲明。

本文鏈接:https://blog.csdn.net/LUOHUATINGYUSHENG/article/details/94489590

審核編輯:何安

-

回流

+關(guān)注

關(guān)注

0文章

21瀏覽量

9970 -

高速信號

+關(guān)注

關(guān)注

1文章

231瀏覽量

17762

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于SMT回流焊接,你了解多少?

高速、RF射頻信號的參考平面分析

一文詳解信號的回流路徑

使用TPS61030的電壓模式升壓轉(zhuǎn)換器小信號控制環(huán)路分析

高速電路設(shè)計與信號完整性分析

高速PCB信號完整性分析及應(yīng)用

高速PCB信號完整性分析及硬件系統(tǒng)設(shè)計中的應(yīng)用

環(huán)路測試儀的工作原理是什么

環(huán)路測試注入信號是不是越小越好

環(huán)路增益和開環(huán)增益的區(qū)別是什么

深度解析高速串行信號的誤碼測試|線上講堂

關(guān)于高速信號回流環(huán)路實際分析

關(guān)于高速信號回流環(huán)路實際分析

評論