用戶定義的原語

在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。

U D P的實例語句與基本門的實例語句完全相同,即 U D P實例語句的語法與基本門的實例語句語法一致。

6.1 UDP的定義

使用具有如下語法的U D P說明定義U D P。

p r i m i t i v e U D P _ n a m e (OutputName, List_of_inputs )

O u t p u t _ d e c l a r a t i o n

L i s t _ o f _ i n p u t _ d e c l a r a t i o n s

[R e g _ d e c l a r a t i o n]

[I n i t i a l _ s t a t e m e n t]

t a b l e

L i s t _ o f _ t a b e l _ e n t r i e s

e n d t a b l e

e n d p r i m i t i v e

U D P的定義不依賴于模塊定義,因此出現在模塊定義以外。也可以在單獨的文本文件中

定義U D P。U D P只能有一個輸出和一個或多個輸入。第一個端口必須是輸出端口。此外,輸出可以取值0、1或x(不允許取z值)。輸入中出現值z以x處理。U D P的行為以表的形式描述。在U D P中可以描述下面兩類行為:

1) 組合電路

2) 時序電路(邊沿觸發和電平觸發)

6.2 組合電路UDP

在組合電路U D P中,表規定了不同的輸入組合和相對應的輸出值。沒有指定的任意組合輸出為x。下面以2 - 1多路選擇器為例加以說明。

p r i m i t i v e MUX2x1 (Z, Hab, Bay, Sel ) ;

o u t p u t Z;

i n p u t Hab,Bay, Sel;

t a b l e

// Hab Bay Sel : Z 注:本行僅作為注釋。

0 ? 1 : 0 ;

1 ? 1 : 1 ;

? 0 0 : 0 ;

? 1 0 : 1 ;

0 0 x : 0 ;

1 1 x : 1 ;

e n d t a b l e

e n d p r i m i t i v e

字符?代表不必關心相應變量的具體值,即它可以是0、1或x。輸入端口的次序必須與表中各項的次序匹配,即表中的第一列對應于原語端口隊列的第一個輸入 (例子中為 H a b),第二列是 B a y,第三列是 S e l。在多路選擇器的表中沒有輸入組合 0 1x項(還有其它一些項 );在這種情況下,輸出的缺省值為 x(對其它未定義的項也是如此 )。

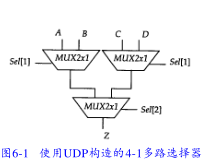

圖6 - 1為使用2 - 1多路選擇器原語組成的4 - 1多路選擇器的示例。

如上例所示,在U D P實例中,總共可以指定 2個時延,這是由于U D P的輸出可以取值0、1或x(無截止時延)。

6.3 時序電路UDP

在時序電路U D P中,使用1位寄存器描述內部狀態。該寄存器的值是時序電路U D P的輸出值。共有兩種不同類型的時序電路U D P:一種模擬電平觸發行為;另一種模擬邊沿觸發行為。時序電路U D P使用寄存器當前值和輸入值決定寄存器的下一狀態 (和后繼的輸出)。

6.3.1 初始化狀態寄存器

時序電路U D P的狀態初始化可以使用帶有一條過程賦值語句的初始化語句實現。形式如下:

i n i t i a l r e g _ n a m e = 0,1,or x;

初始化語句在U D P定義中出現。

6.3.2 電平觸發的時序電路UDP

下面是D鎖存器建模的電平觸發的時序電路 U D P示例。只要時鐘為低電平 0,數據就從輸入傳遞到輸出;否則輸出值被鎖存。

p r i m i t i v e Latch (Q, Clk, D) ;

o u t p u t Q;

r e g Q;

i n p u t Clk, D;

t a b l e

// Clk D Q(State) Q( n e x t )

0 1 : ? : 1 ;

0 0 : ? : 0 ;

1 ? : ? : - ;

e n d t a b l e

e n d p r i m i t i v e

“-”字符表示值“無變化”。注意U D P的狀態存儲在寄存器D中。

6.3.3 邊沿觸發的時序電路UDP

下例用邊沿觸發時序電路U D P為D邊沿觸發觸發器建模。初始化語句用于初始化觸發器的狀態。

表項( 0 1 )表示從0轉換到1,表項( 0 x )表示從0轉換到x,表項( ? 0 )表示從任意值( 0 , 1或x)轉換到0,表項( ? ? )表示任意轉換。對任意未定義的轉換,輸出缺省為 x。

假定D _ E d g e _ F F為U D P定義,它現在就能夠象基本門一樣在模塊中使用,如下面的 4位寄存器所示。

6.3.4 邊沿觸發和電平觸發的混合行為

在同一個表中能夠混合電平觸發和邊沿觸發項。在這種情況下,邊沿變化在電平觸發之前處理,即電平觸發項覆蓋邊沿觸發項。下例是帶異步清空的D觸發器的U D P描述。

6.4 另一實例

下面是3位表決電路的U D P描述。如果輸入向量中存在2個或更多的1,則輸出為1。

6.5 表項匯總

原文標題:Verilog入門-用戶定義的原語

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

Verilog

+關注

關注

28文章

1351瀏覽量

110391 -

HDL

+關注

關注

8文章

328瀏覽量

47468

原文標題:Verilog入門-用戶定義的原語

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog HDL指定用戶定義原語UDP的能力介紹

Verilog HDL指定用戶定義原語UDP的能力介紹

評論