引言:從本文開(kāi)始,我們陸續(xù)介紹下有關(guān)7系列FPGA通用PCB設(shè)計(jì)指導(dǎo),重點(diǎn)介紹在PCB和接口級(jí)別做出設(shè)計(jì)決策的策略。由于FPGA本身也屬于數(shù)字集成電路,文章中的大部分設(shè)計(jì)策略及概念也可為其他數(shù)字IC電路設(shè)計(jì)提供參考。文章內(nèi)容主要包括以下五個(gè)章節(jié)內(nèi)容:

PCB技術(shù)基礎(chǔ):討論當(dāng)前PCB技術(shù)的基礎(chǔ),重點(diǎn)是物理結(jié)構(gòu)和常見(jiàn)假設(shè)。

配電系統(tǒng)(PDS):涵蓋7系列FPGA的配電系統(tǒng),包括去耦電容選擇、穩(wěn)壓器和PCB幾何結(jié)構(gòu)的使用、仿真和測(cè)量的所有細(xì)節(jié)。

SelectIO信號(hào)設(shè)計(jì):包含SelectIO 標(biāo)準(zhǔn)、I/O拓?fù)鋱D和端接策略以及有關(guān)仿真和測(cè)量技術(shù)的信息。

PCB材料和走線:為獲得最佳性能的高頻應(yīng)用,提供一些關(guān)于管理信號(hào)衰減的設(shè)計(jì)策略。

高速信號(hào)傳輸設(shè)計(jì):闡述了傳輸線的高速設(shè)計(jì)。

所提供的分析和實(shí)例可以大大加快具體設(shè)計(jì)的速度。

本文我們介紹第一部分內(nèi)容,即PCB技術(shù)基礎(chǔ)。

印刷電路板(PCB)是電氣系統(tǒng),其電氣特性與安裝在其上的分立元件和器件一樣復(fù)雜。PCB設(shè)計(jì)者需要對(duì)PCB的許多方面都有完全的控制權(quán);然而,當(dāng)前的技術(shù)對(duì)其幾何結(jié)構(gòu)和由此產(chǎn)生的電性能施加了限制和限制,本小結(jié)介紹以下內(nèi)容:

PCB結(jié)構(gòu)

輸電線路

回流

1. PCB結(jié)構(gòu)

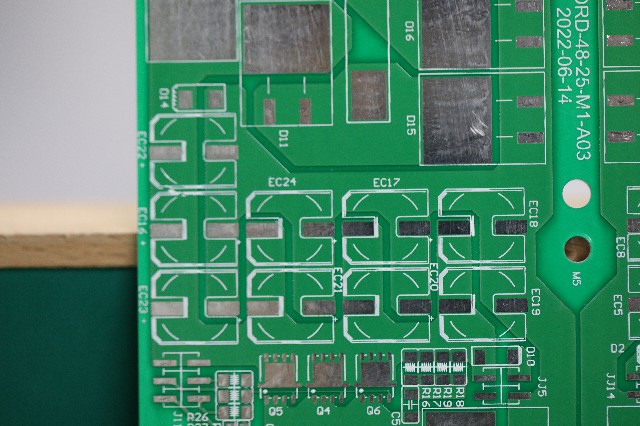

PCB技術(shù)在過(guò)去幾十年中沒(méi)有發(fā)生顯著變化。兩面鍍銅的絕緣體基材(通常是FR4,環(huán)氧樹(shù)脂/玻璃復(fù)合材料)的一部分銅被腐蝕掉,形成導(dǎo)電路徑。電鍍和蝕刻基板的層與蝕刻基板之間的額外絕緣體基板粘合在一起。在層疊上鉆孔,將導(dǎo)電鍍層應(yīng)用于這些過(guò)孔,在不同層的蝕刻銅之間選擇性拓?fù)涑蓪?dǎo)電連接。

圖1、PCB構(gòu)成

雖然PCB技術(shù)有了進(jìn)步,但PCB的基本結(jié)構(gòu)沒(méi)有改變,例如材料特性、使用的層疊層數(shù)、幾何結(jié)構(gòu)和鉆孔技術(shù)(允許孔只穿透堆疊的一部分)。通過(guò)PCB技術(shù)形成的結(jié)構(gòu)被抽象為一組物理/電氣結(jié)構(gòu):走線、平面(或電源層)、通孔和焊盤。

1.1 走線

走線是一種物理金屬條(通常是銅),在PCB的X-Y坐標(biāo)上的兩個(gè)或多個(gè)點(diǎn)之間進(jìn)行電氣連接。走線承載了兩點(diǎn)之間信號(hào)的傳輸。

1.2 平面(Planes)

平面是覆蓋整個(gè)PCB層的不間斷金屬區(qū)域。小平面,一個(gè)平面的變體,是一個(gè)不間斷的金屬區(qū)域,只覆蓋PCB層的一部分。通常,一個(gè)PCB層中存在多個(gè)小平面。平面和小平面將能量分配給PCB上的許多點(diǎn)。它們?cè)谧呔€傳輸信號(hào)時(shí)非常重要,因?yàn)樗鼈兪切盘?hào)回流傳輸介質(zhì)。圖1顯示了完整平面(GND)和小平面(局部鋪銅)。

1.3 過(guò)孔

過(guò)孔是一塊金屬,在PCB的Z軸空間中的兩個(gè)或多個(gè)點(diǎn)之間進(jìn)行電氣連接。過(guò)孔在PCB層之間傳輸信號(hào)或電源。在當(dāng)前的平板穿透孔(PTH)技術(shù)中,通孔是通過(guò)在PCB上鉆孔的內(nèi)表面電鍍而成的。在目前的微孔技術(shù)(Microvias,也稱為高密度互連或HDI)中,通孔是用激光燒蝕基底材料并使導(dǎo)電鍍層變形而形成的。這些微孔不能穿透超過(guò)一層或兩層,但是,它們可以堆疊或階梯式形成貫穿整個(gè)板厚的通孔。

1.4焊盤和反焊盤

因?yàn)镻TH過(guò)孔在過(guò)孔的整個(gè)長(zhǎng)度上都是導(dǎo)電的,所以需要一種方法來(lái)選擇性地對(duì)PCB的各個(gè)層的跡線、平面和小平面進(jìn)行電連接。這是焊盤和反焊盤的作用。 焊盤是規(guī)定形狀的小面積銅。反焊盤是規(guī)定形狀的小區(qū)域,在那里銅被去除。焊盤既可與通孔一起使用,也可用作安裝表面貼裝元件的裸露外層銅。反焊盤主要與過(guò)孔一起使用。

圖3、焊盤結(jié)構(gòu)

對(duì)于走線,焊盤用于在通孔和給定層上的走線或平面形狀之間進(jìn)行電氣連接。要使通孔與PCB層上的走線形成牢固連接,必須有一個(gè)焊盤以保證機(jī)械穩(wěn)定性。焊盤的尺寸必須符合鉆孔公差/定位限制。

反焊盤在平面(Planes)層使用。因在為平面和小平面銅是不間斷的,所以任何穿過(guò)銅的通孔都會(huì)與銅形成電氣連接。在那里過(guò)孔并不是用來(lái)與通過(guò)的平面或小平面進(jìn)行電氣連接的,反焊盤會(huì)去除過(guò)孔穿透的層區(qū)域中的銅。

1.5 Lands

為了焊接表面貼裝元件,外層上的焊盤通常稱為焊環(huán)(圖3中錫膏層)。與這些焊盤進(jìn)行電氣連接通常需要通孔。由于PTH技術(shù)的制造限制,很少采用可以在Lands區(qū)域內(nèi)放置通孔。取而代之的是,使用一小段連接到表面焊盤的走線。連接走線的最小長(zhǎng)度由PCB制造商的最小尺寸規(guī)格確定。微孔技術(shù)不受限制,過(guò)孔可以直接放置在焊盤。為了有關(guān)PCB焊盤和BGA封裝的更多信息,請(qǐng)參閱7系列FPGA封裝和引腳產(chǎn)品規(guī)范用戶指南(UG475)附錄“BGA封裝的推薦PCB設(shè)計(jì)規(guī)則”。

1.6 尺寸

定義PCB尺寸的主要因素是PCB制造限制、FPGA封裝幾何形狀和系統(tǒng)符合性。其他因素,如面向制造的設(shè)計(jì)(DFM)和可靠性施加了進(jìn)一步的限制,但由于這些是特定于應(yīng)用程序的,因此本用戶指南中沒(méi)有記錄這些因素。

FPGA封裝的尺寸與PCB制造限制相結(jié)合,直接和間接地定義了本節(jié)中描述的PCB結(jié)構(gòu)(PCB結(jié)構(gòu))的大部分幾何方面。這大大限制了PCB設(shè)計(jì)者。封裝球間距(FF封裝為1.0 mm)定義了焊盤布局。當(dāng)前PCB技術(shù)的最小表面特征尺寸定義了器件下區(qū)域的通孔排列。最小通孔直徑和這些通孔周圍的隔離區(qū)域由PCB制造商定義,這些直徑限制了通孔之間的可用空間量與最大走線寬度。PCB制造限制限制了最小走線寬度和最小間距。

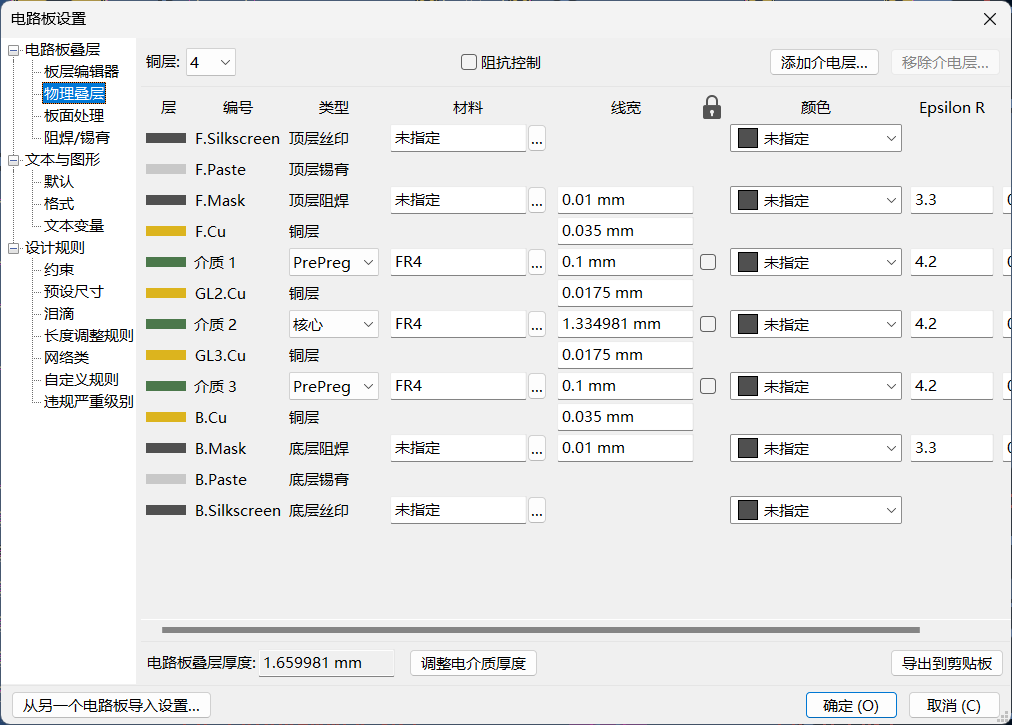

圖4、12層PCB層疊設(shè)計(jì)案例

容納FPGA所需的PCB層的總數(shù)由信號(hào)層的數(shù)量和平面層的數(shù)量定義,大多數(shù)用于大型FPGA的PCB從12層到22層不等。

信號(hào)層的數(shù)量由進(jìn)出FPGA封裝的I/O信號(hào)通道的數(shù)量定義(通常與封裝中的總用戶I/O數(shù)有關(guān))。

平面層的數(shù)量由向FPGA供電并為信號(hào)層提供參考和隔離所需的電源和地平面層的數(shù)量來(lái)定義。

系統(tǒng)總體要求通常定義了電路板的總厚度,因此,隨著電路板層數(shù)的增加,信號(hào)層與平面層(參考層)、以及信號(hào)層與信號(hào)之間的層間距會(huì)變得越來(lái)越小,這會(huì)引入信號(hào)層間的串?dāng)_以及影響信號(hào)阻抗以及電源系統(tǒng)寄生電感等。 信號(hào)走線到參考平面層的Z方向間距(由電路板總厚度和電路板層數(shù)定義)是走線中的一個(gè)決定性因素,走線寬度(由FPGA封裝球間距和PCB通過(guò)制造限制定義)是控制阻抗的另一個(gè)因素。設(shè)計(jì)者通常很少控制FPGA下的過(guò)孔陣列區(qū)域的走線阻抗。當(dāng)走線穿出BGA陣列時(shí),其寬度可以改變?yōu)槟繕?biāo)阻抗的寬度(通常為50Ω單端)。

去耦電容器布局和分立終端電阻布局是其他領(lǐng)域的權(quán)衡優(yōu)化。DFM約束通常在FPGA(器件封裝)周圍定義一個(gè)隔離區(qū)域,在該區(qū)域中不能放置分立的組件。禁區(qū)的目的是為裝配和返工留出空間必要的。為了因此,在“禁止入內(nèi)”區(qū)域之外的區(qū)域是一個(gè)組件放置位置的區(qū)域。由PCB設(shè)計(jì)師決定高優(yōu)先級(jí)組件。去偶電容器布置約束在第2部分“配電系統(tǒng)”中進(jìn)行了描述。

2 傳輸線

信號(hào)走線和參考平面的組合形成傳輸線。PCB系統(tǒng)中的所有I/O信號(hào)都通過(guò)傳輸線傳輸。 對(duì)于單端I/O接口,信號(hào)走線和參考平面都是將信號(hào)從PCB上的一個(gè)位置傳輸?shù)搅硪粋€(gè)位置所必需的。對(duì)于差分I/O接口,傳輸線由兩根走線和一個(gè)參考面組成。雖然在差分信號(hào)的情況下,參考面的存在并不是嚴(yán)格必要的,但對(duì)于pcb中差分走線的實(shí)際實(shí)現(xiàn)卻是必要的。

在PCB系統(tǒng)中,良好的信號(hào)完整性依賴于具有阻抗受控的傳輸線。阻抗由走線的幾何形狀和信號(hào)走線周圍以及信號(hào)走線與參考面之間的填充材料的介電常數(shù)決定。

3 回流

傳輸線及其信號(hào)完整性的一個(gè)經(jīng)常被忽視的方面是回流。假設(shè)一條信號(hào)線本身形成一條傳輸線是不正確的。在信號(hào)走線中流動(dòng)的電流在其下方的參考平面中具有相等和相反的互補(bǔ)電流。走線電壓和走線電流與參考面電壓和參考面電流的關(guān)系定義了由走線和參考面形成的傳輸線的特性阻抗。雖然走線下參考平面連續(xù)性的中斷效果不如切斷信號(hào)走線那么顯著,但傳輸線和共享參考平面的任何設(shè)備的性能都會(huì)受到影響。

圖5、信號(hào)回流路徑

重要的是要注意參考平面的連續(xù)性和回流路徑。打斷參考平面的連續(xù)性,如孔、槽或隔離縫隙,在信號(hào)傳輸中引起顯著的阻抗不連續(xù)性。它們也可能是串?dāng)_的重要來(lái)源,并導(dǎo)致配電系統(tǒng)(PDS)噪聲。回流路徑的重要性不可小覷。

原文標(biāo)題:Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)(一)

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606060 -

pcb

+關(guān)注

關(guān)注

4326文章

23161瀏覽量

399992

原文標(biāo)題:Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)(一)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

假設(shè)檢驗(yàn)的功效和樣本數(shù)量

電源 PCB 布局中的常見(jiàn)錯(cuò)誤及避免方式

PCB 設(shè)計(jì)規(guī)則、層疊結(jié)構(gòu)的導(dǎo)入/導(dǎo)出

五種常見(jiàn)的PCB表面處理技術(shù)

常見(jiàn)的PCB元件封裝類型

PCB線路板常見(jiàn)缺陷原因分析:解鎖電路板制造的隱秘挑戰(zhàn)

pcb板設(shè)計(jì)中的常見(jiàn)錯(cuò)誤

了解雙面和多層pcb板的優(yōu)缺點(diǎn)

PCB設(shè)計(jì)中常見(jiàn)的DFM問(wèn)題

Samtec 技術(shù)大咖說(shuō) | PCB VS 電纜背板?

PCB線路板制造中常見(jiàn)的錯(cuò)誤有哪些,如何避免?

【AWTK使用經(jīng)驗(yàn)】如何響應(yīng)物理按鍵

PCB設(shè)計(jì)中的常見(jiàn)問(wèn)題有哪些?

PCB板的顏色應(yīng)該怎么選?為什么綠色最常見(jiàn)?

PCB設(shè)計(jì)工作中常見(jiàn)的錯(cuò)誤有哪些?

PCB的物理結(jié)構(gòu)和常見(jiàn)假設(shè)

PCB的物理結(jié)構(gòu)和常見(jiàn)假設(shè)

評(píng)論