一:fifo是什么

FIFO的完整英文拼寫(xiě)為FirstIn First Out,即先進(jìn)先出。FPGA或者ASIC中使用到的FIFO一般指的是對(duì)數(shù)據(jù)的存儲(chǔ)具有先進(jìn)先出特性的一個(gè)存儲(chǔ)器,常被用于數(shù)據(jù)的緩存或者高速異步數(shù)據(jù)的交互。

二:FIFO有幾種結(jié)構(gòu)

FIFO從大的情況來(lái)分,有兩類(lèi)結(jié)構(gòu):?jiǎn)?a href="http://www.qldv.cn/tags/時(shí)鐘/" target="_blank">時(shí)鐘FIFO(SCFIFO)和雙時(shí)鐘FIFO(DCFIFO),其中雙時(shí)鐘FIFO又可以分為普通雙時(shí)鐘(DCFIFO)和混合寬度雙時(shí)鐘FIFO (DCFIFO_MIXED_WIDTHS)。三種FIFO結(jié)構(gòu)的英文含義如下所示:

?SCFIFO: 單時(shí)鐘FIFO

?DCFIFO:雙時(shí)鐘 FIFO

?DCFIFO_MIXED_WIDTHS: 混合寬度雙時(shí)鐘

在沒(méi)有特別指明的情況下,混合寬度雙時(shí)鐘FIFO和雙時(shí)鐘FIFO統(tǒng)稱(chēng)為雙時(shí)鐘FIFO。

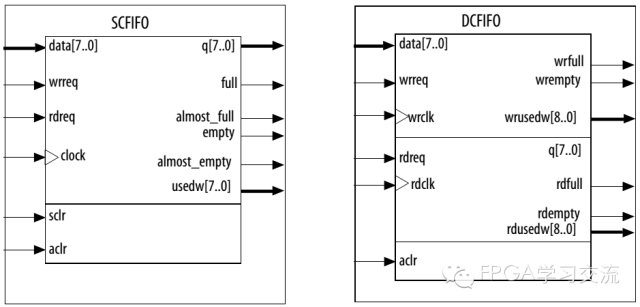

下圖為分別為單時(shí)鐘FIFO和雙時(shí)鐘FIFO的符號(hào)圖:

從圖中我們可以看到,單時(shí)鐘FIFO具有一個(gè)獨(dú)立的時(shí)鐘端口clock,當(dāng)Clock上升沿到達(dá)時(shí),且wrreq有效時(shí),將data[7..0]中的數(shù)據(jù)寫(xiě)入FIFO;當(dāng)Clock上升沿到達(dá)時(shí),且rdreq有效時(shí),將q[7..0]中的數(shù)據(jù)輸出FIFO;full是滿(mǎn)標(biāo)志位,當(dāng)FIFO寫(xiě)滿(mǎn)時(shí)有效,almost_full是將滿(mǎn)標(biāo)志,當(dāng)快寫(xiě)滿(mǎn)時(shí)有效,almost_full數(shù)值可以配置;同理empty與almost_empty是空標(biāo)志和將要空標(biāo)志,自己也可以配置almost_empty。usedw[7..0]是當(dāng)前FIFO可以使用的數(shù)據(jù)。sclr是同步清零,當(dāng)有效時(shí)且Clocks上升沿到達(dá)時(shí)清楚FIFO的數(shù)據(jù);aclr是異步清零,當(dāng)有效時(shí)清除FIFO的數(shù)據(jù)。

雙時(shí)鐘FIFO和單時(shí)鐘FIFO基本一樣,就是讀寫(xiě)分別采用不同的時(shí)鐘信號(hào)。wrfull為寫(xiě)滿(mǎn)標(biāo)志,wrempty為寫(xiě)空標(biāo)志,當(dāng)我們想在只有FIFO空的時(shí)候才能寫(xiě)入時(shí)就用wrempty來(lái)判斷,wrusedw[8..0]寫(xiě)入多少數(shù)據(jù),rdusedw[8..0]能讀出多少數(shù)據(jù)。這里將寫(xiě)入的數(shù)據(jù)和刻度的數(shù)據(jù)分開(kāi)計(jì)數(shù)的原因是,當(dāng)我們寫(xiě)入數(shù)據(jù)長(zhǎng)度和讀數(shù)據(jù)長(zhǎng)度不同時(shí),比如寫(xiě)的數(shù)據(jù)長(zhǎng)度是16位,讀的數(shù)據(jù)長(zhǎng)度是8位,當(dāng)寫(xiě)入一個(gè)數(shù)據(jù)wrusedw[8..0]=1,而rdusedw[8..0]=2。rdfull是讀滿(mǎn)標(biāo)志,當(dāng)我們要想要只有寫(xiě)滿(mǎn)時(shí)才可讀可根據(jù)這個(gè)標(biāo)志判斷(讀數(shù)據(jù)包)。rdempty讀空標(biāo)志,當(dāng)FIFO沒(méi)有可讀數(shù)據(jù)時(shí)有效。aclr異步請(qǐng)零。雙時(shí)鐘FIFO只有異步清零。

三:不同結(jié)構(gòu)的FIFO各有什么作用

單時(shí)鐘FIFO:

單時(shí)鐘FIFO常用于片內(nèi)數(shù)據(jù)交互,例如,在FPGA的控制下從外部傳感器讀取到的一連串傳感器數(shù)據(jù),首先被寫(xiě)入FIFO中,然后再以UART串口的數(shù)據(jù)發(fā)送速率將數(shù)據(jù)依次發(fā)送出去。由于傳感器的單次讀取數(shù)據(jù)可能很快,但并不是時(shí)刻都需要采集數(shù)據(jù),例如某傳感器使用SPI接口的協(xié)議,F(xiàn)PGA以2M的SPI數(shù)據(jù)速率從該傳感器中讀取20個(gè)數(shù)據(jù),然后以9600的波特率通過(guò)串口發(fā)送出去。此過(guò)程每秒鐘執(zhí)行一次。因?yàn)?M的數(shù)據(jù)速率遠(yuǎn)高于串口9600的波特率,因此需要將從傳感器中采集到的數(shù)據(jù)首先用FIFO緩存起來(lái),然后再以串口的數(shù)據(jù)速率緩慢發(fā)送出去。這里,由于傳感器數(shù)據(jù)的讀取和串口數(shù)據(jù)的發(fā)送都是可以同步于同一個(gè)時(shí)鐘的,因此可以使用單時(shí)鐘結(jié)構(gòu)的FIFO來(lái)實(shí)現(xiàn)此功能。

雙時(shí)鐘FIFO:

雙時(shí)鐘FIFO的一個(gè)典型應(yīng)用就是異步數(shù)據(jù)的收發(fā)。

所謂異步數(shù)據(jù)是指數(shù)據(jù)的發(fā)送端和接收端分別同步與不同的時(shí)鐘域,使用雙時(shí)鐘FIFO的獨(dú)立的讀寫(xiě)時(shí)鐘結(jié)構(gòu),能夠?qū)⒉煌瑫r(shí)鐘域中的數(shù)據(jù)同步到所需的時(shí)鐘域系統(tǒng)中。例如,在一個(gè)視頻圖像采集系統(tǒng)中,實(shí)現(xiàn)將攝像頭采集的數(shù)據(jù)通過(guò)VGA在顯示器上顯示。攝像頭輸入的數(shù)據(jù)長(zhǎng)度和速度與輸出到VGA顯示的數(shù)據(jù)長(zhǎng)度和速度都不相同,這種情況下使用雙時(shí)鐘FIFO。

四:如何在Altera FPGA中使用FIFO實(shí)現(xiàn)功能設(shè)計(jì)

在Altera FPGA中使用FIFO實(shí)現(xiàn)用戶(hù)功能設(shè)計(jì)主要有三種實(shí)現(xiàn)方式,第一種為用戶(hù)根據(jù)需求自己編寫(xiě)FIFO邏輯,當(dāng)用戶(hù)對(duì)于FIFO的功能有特殊需求時(shí),可以使用此種方式實(shí)現(xiàn),但此種方式要求用戶(hù)有較高的RTL設(shè)計(jì)能力。第二種方式為使用第三方提供的開(kāi)源IP核,此種IP核以源碼的形式提供,能夠快速的應(yīng)用到用戶(hù)系統(tǒng)中,當(dāng)用戶(hù)對(duì)FIFO功能有特殊需求時(shí),可以在此源碼的基礎(chǔ)上進(jìn)行修改,以適應(yīng)自己的系統(tǒng)需求。第三種方式為使用Quartus II軟件提供的免費(fèi)FIFO IP核,此種方式下,Quartus II軟件為用戶(hù)提供了友好的圖形化界面方便用戶(hù)對(duì)FIFO的各種參數(shù)和結(jié)構(gòu)進(jìn)行配置,生成的FIFO IP核針對(duì)Altera不同系列的器件,還可以實(shí)現(xiàn)結(jié)構(gòu)上的優(yōu)化。

原文標(biāo)題:一起來(lái)了解一下FIFO!

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605989 -

fifo

+關(guān)注

關(guān)注

3文章

389瀏覽量

43855

原文標(biāo)題:一起來(lái)了解一下FIFO!

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Altera正式獨(dú)立運(yùn)營(yíng):FPGA行業(yè)格局將迎來(lái)新變局

如何在Windows中使用MTP協(xié)議

FIFO Generator的Xilinx官方手冊(cè)

如何在智能手機(jī)系統(tǒng)中使用bq27505

如何在MSP430?MCU中使用智能模擬組合

如何在反向降壓-升壓拓?fù)?b class='flag-5'>中使用TPS6290x

如何在FPGA中實(shí)現(xiàn)隨機(jī)數(shù)發(fā)生器

如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

請(qǐng)問(wèn)cmakelists中的變量如何在程序中使用?

如何在labview FPGA端實(shí)現(xiàn)二維插值的功能?

Altera將AI注入新的中端FPGA

如何在Altera FPGA中使用FIFO實(shí)現(xiàn)功能設(shè)計(jì)?

如何在Altera FPGA中使用FIFO實(shí)現(xiàn)功能設(shè)計(jì)?

評(píng)論