隨著5G技術(shù)的發(fā)展,射頻前端(RFFE)設(shè)計變得越來越復(fù)雜,而系統(tǒng)級封裝(SiP)技術(shù)因其可集成多顆裸芯片與無源器件的特點,開始被廣泛用于射頻前端的設(shè)計中。 芯片設(shè)計與封裝設(shè)計傳統(tǒng)上是由各自工程團隊獨立完成,這樣做的缺陷是增加了迭代時間和溝通成本。如果能夠?qū)崿F(xiàn)芯片和封裝協(xié)同設(shè)計,不僅可大幅減少迭代次數(shù),提高設(shè)計成功率,而且使能芯片工程師在設(shè)計流程中隨時評估封裝性能。 目前在市場上,要實現(xiàn)快速的芯片和封裝協(xié)同仿真的方法并不多。芯和半導(dǎo)體獨創(chuàng)的這套聯(lián)合仿真流程中,三維建模簡單易用,并配有專門針對聯(lián)合仿真的優(yōu)化求解器,能夠提供更高的仿真加速和仿真效率。

三維建模和仿真流程

1.導(dǎo)入芯片和封裝版圖文件

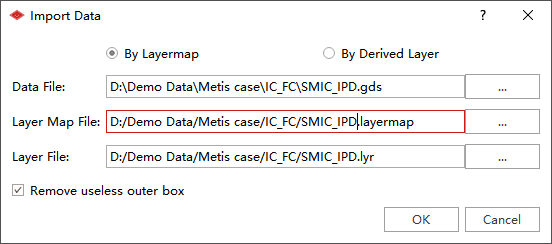

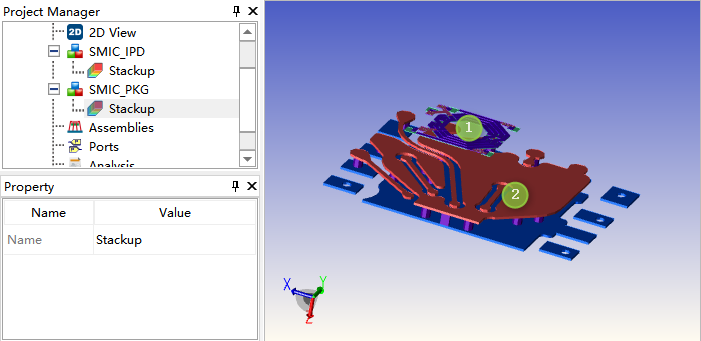

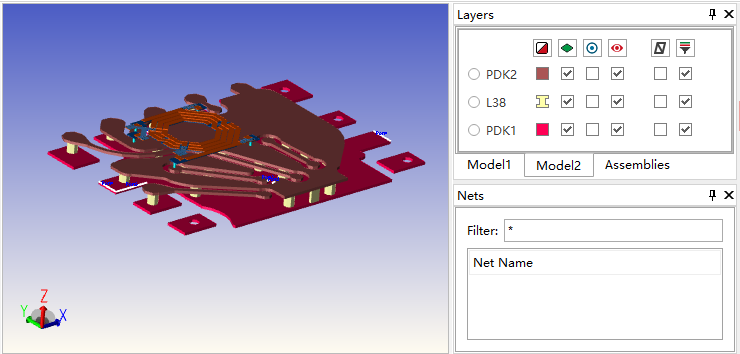

在Metis工具中,可直接導(dǎo)入Cadence的設(shè)計文件(.mcm/.sip/.brd)、ODB++文件、以及DXF和GDS文件。本案例中芯片和封裝版圖均為GDS格式,同時還需要layermap文件和仿真工藝信息lyr文件。依次導(dǎo)入芯片和封裝版圖后,在Metis 3D視圖中自動生成了它們的三維結(jié)構(gòu)(圖2),此時它們的相對位置是任意,需要通過Bump將它們連接在一起。

圖1 導(dǎo)入版圖界面

圖2導(dǎo)入芯片和封裝文件

2.模型堆疊

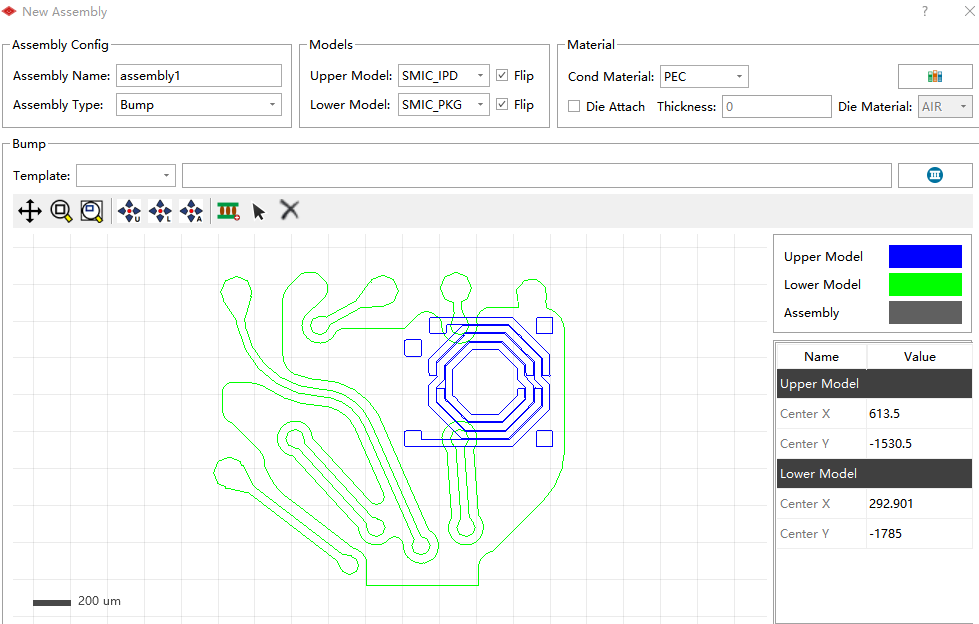

在左側(cè)的項目管理欄,選擇Assemblies,進入堆疊設(shè)置界面。在上側(cè)Model欄,我們將芯片設(shè)置為Upper Model,將封裝設(shè)置為Lower Model(圖3)。

圖3 切割后的模型 左:Serdes; 右:DDR

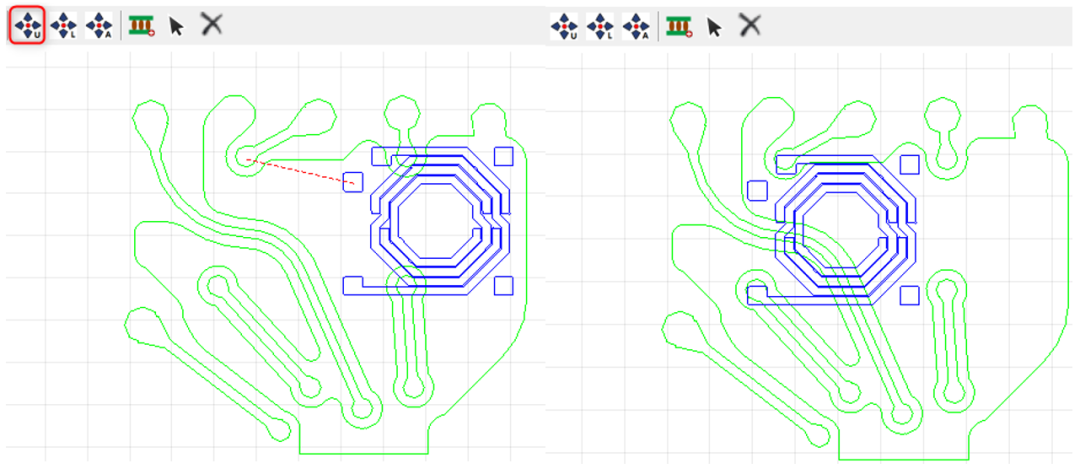

接著我們使用拖拽功能,將Upper Model拖拽至正確的封裝焊點位置(圖4)。

圖4 移動upper Model至正確位置(右圖)

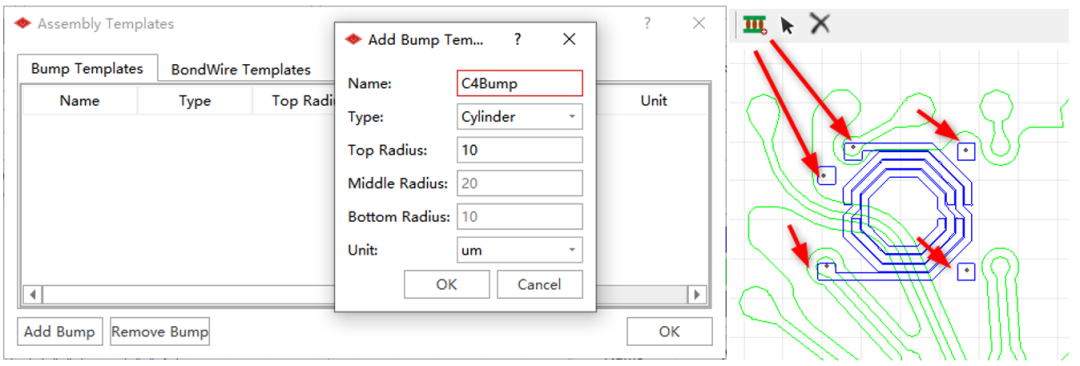

最后創(chuàng)建合適的Bump模型,通過在芯片pad上點擊增加Bump模型,將芯片和封裝結(jié)構(gòu)連接在一起(圖5)。

圖5 Bump建模及添加

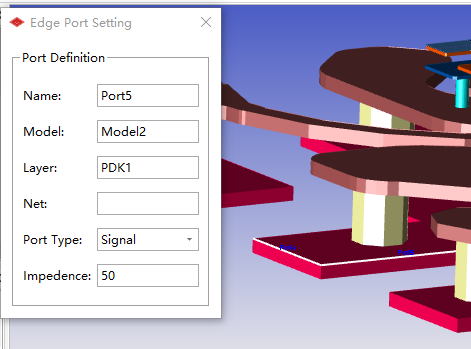

3.端口添加

模型堆疊完畢后,用戶可以直接在3D視圖中添加集總端口,其中信號類型,金屬層次,端口阻抗可任意配置。在本案例中,我們選擇封裝焊盤的一邊作為信號端口。

圖6 疊層及端口管理

圖7 生成的最終仿真模型

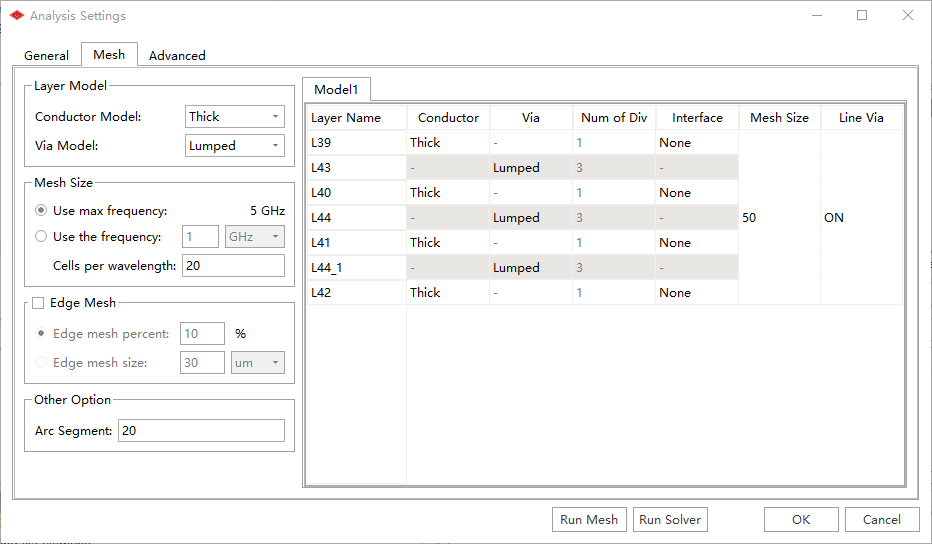

4.仿真環(huán)境設(shè)置

Metis的網(wǎng)格劃分、金屬和過孔模型可以根據(jù)不同的結(jié)構(gòu)進行分開設(shè)置,從而達到仿真精度與效率的雙重提升。本案例中芯片的金屬設(shè)置為Thick,過孔為Lumped,網(wǎng)格大小為50um,而封裝的金屬設(shè)置為3D,過孔為3D,網(wǎng)格大小為200um。最后點擊Run Solver進行聯(lián)合仿真。

圖8 芯片的仿真設(shè)置

5.仿真結(jié)果比對

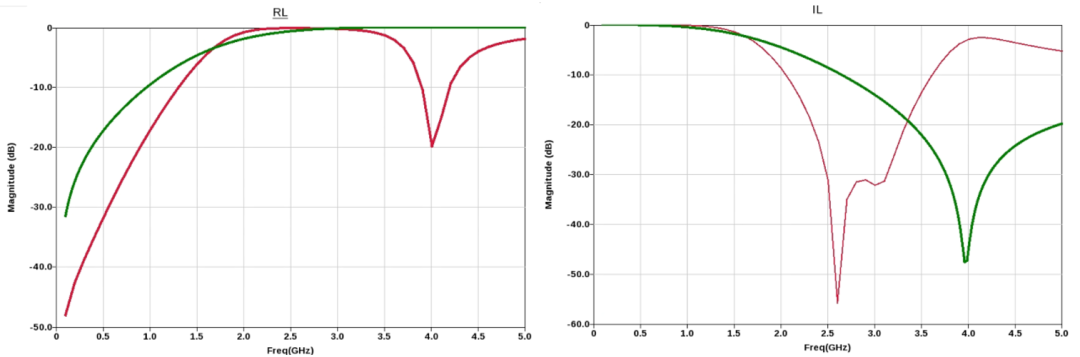

我們分別仿真了不帶封裝和帶封裝兩種應(yīng)用場景,來分析封裝對芯片濾波特性的影響。綠色曲線是不帶封裝的芯片仿真數(shù)據(jù),紅色曲線是帶封裝的芯片仿真數(shù)據(jù)。通過對比RL和IL兩個指標(biāo),我們發(fā)現(xiàn)在通帶內(nèi)濾波器特性并沒有明顯惡化,但是由于封裝的容性寄生,導(dǎo)致帶外的抑制性能急劇下降。這將對射頻系統(tǒng)接收信號和本征信號帶來干擾,從而導(dǎo)致信號的阻塞。由此我們得出結(jié)論,封裝效應(yīng)是芯片設(shè)計不得不考慮的重要因素,同時Metis能很好的解決聯(lián)合仿真建模困難,優(yōu)化設(shè)計效率低的問題。

圖9 RL與IL比對結(jié)果

總結(jié)

本文介紹了一種采用芯和半導(dǎo)體的Metis工具實現(xiàn)芯片和封裝聯(lián)合仿真的方法。通過Metis分別導(dǎo)入芯片和封裝的版圖文件,將芯片倒裝焊在封裝基板上,建立三維堆疊模型。最后使用Metis進行快速的電磁仿真分析,我們考察了封裝對芯片性能指標(biāo)的影響。此案例可以幫助設(shè)計人員進行芯片和封裝協(xié)同設(shè)計可大幅減少迭代次數(shù),提高設(shè)計成功率,使能芯片工程師在設(shè)計流程中隨時評估封裝性能。

編輯:jq

-

芯片

+關(guān)注

關(guān)注

456文章

51192瀏覽量

427341 -

濾波器

+關(guān)注

關(guān)注

161文章

7862瀏覽量

178948 -

封裝

+關(guān)注

關(guān)注

127文章

7997瀏覽量

143417 -

RFFE

+關(guān)注

關(guān)注

0文章

8瀏覽量

5890

原文標(biāo)題:怎樣實現(xiàn) “高效的芯片與封裝的聯(lián)合仿真”?

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

三分鐘帶你搞懂,芯片封裝的發(fā)展路徑!你知道封裝技術(shù)都有哪些嗎?#華芯邦 #芯片封裝 #封裝路徑 #芯片制造

傳統(tǒng)封裝你了解多少,小白快捷學(xué)習(xí) | 第1集 #傳統(tǒng)封裝 #先進封裝 #芯片封裝 #華芯邦 #

中美貿(mào)易戰(zhàn),國產(chǎn)芯片發(fā)展艱難,先進封裝助力中國芯突圍!#芯片封裝 #先進封裝 #華芯邦 #

芯片封裝是什么?芯片封裝中芯片環(huán)氧膠的應(yīng)用有哪些?

自動駕駛聯(lián)合仿真——功能模型接口FMI(終)

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(四)

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(三)

康謀分享 | 自動駕駛聯(lián)合仿真——功能模型接口FMI(二)

怎樣實現(xiàn)高效的芯片與封裝的聯(lián)合仿真?

怎樣實現(xiàn)高效的芯片與封裝的聯(lián)合仿真?

評論